DS07-16401-2E

FUJITSU SEMICONDUCTOR

DATA SHEET

32-bit RISC Microcontroller

CMOS

FR50 Family MB91360G Series

MB91FV360GA/F361GA/F362GA

s

DESCRIPTION

The Fujitsu MB91360G series is a standard microcontroller containing a wide range of I/O peripherals and bus

control functions. The MB91360G series features a 32-bit RISC CPU (FR50 series) core and is suitable for

embedded control applications requiring high-performance and high-speed CPU processing. The MB91360G

series also contains up to 4 Kbyte instruction cache memory and other internal memories to improve the execution

speed of the CPU.

s

FEATURES

∑ Execution time : down to 15.6 ns (64 MHz)

∑ FR50 series CPU : RISC architecture

The CPU has a general-purpose register architecture with improved numeric implementation whereby a wide

range of delayed branch instructions reduces losses in execution time due to pipeline breaks.

Bit manipulation instructions and memory access instructions have been enhanced resulting in improved code

efficiency and execution speed for control implementation.

∑

A five-stage pipeline structure provides high-speed processing (one instruction per cycle)

∑

32-bit linear address space : 4 Gbytes

∑

Fixed 16-bit instruction size (basic instructions)

∑

High-speed multiplication/step division

∑

High-speed interrupt processing (6 cycles)

∑

General-purpose registers : 16

◊

32 bits

(Continued)

s

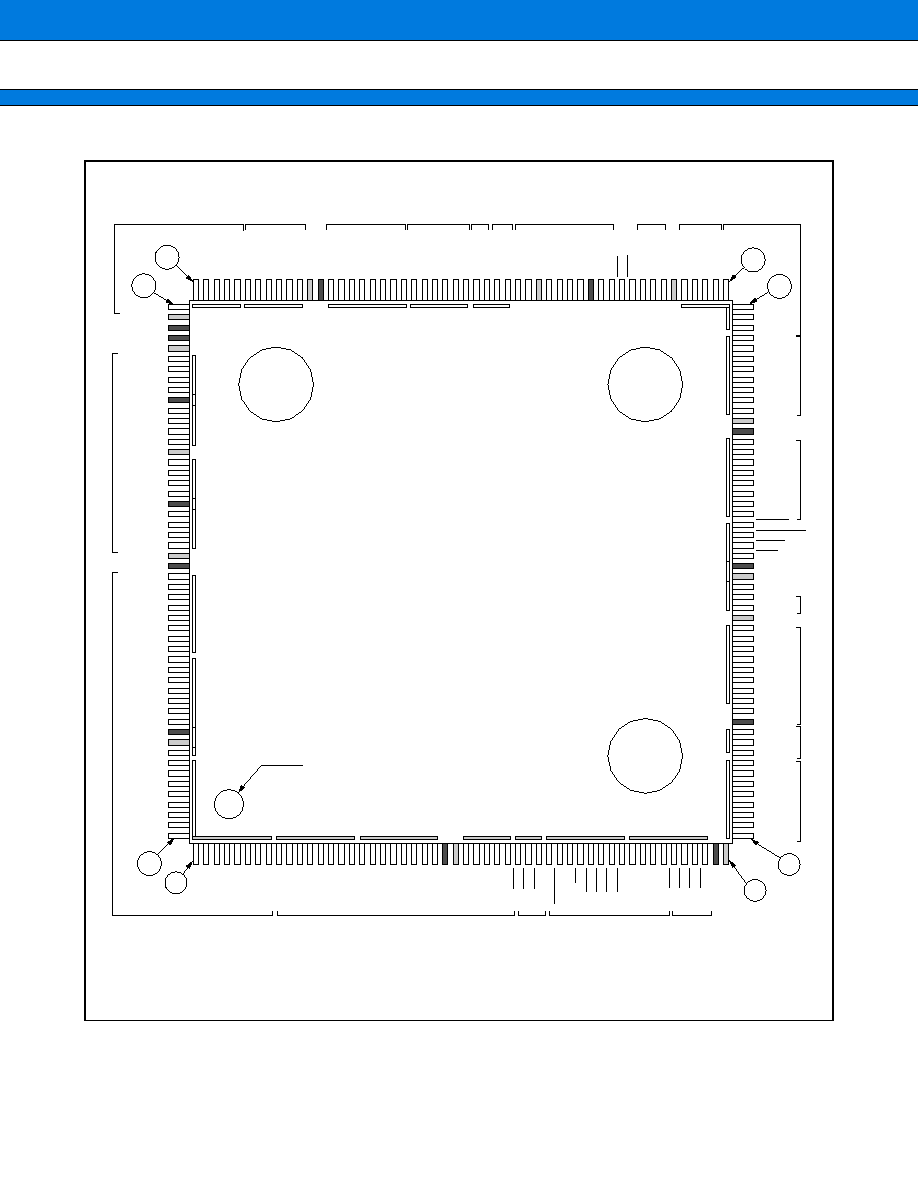

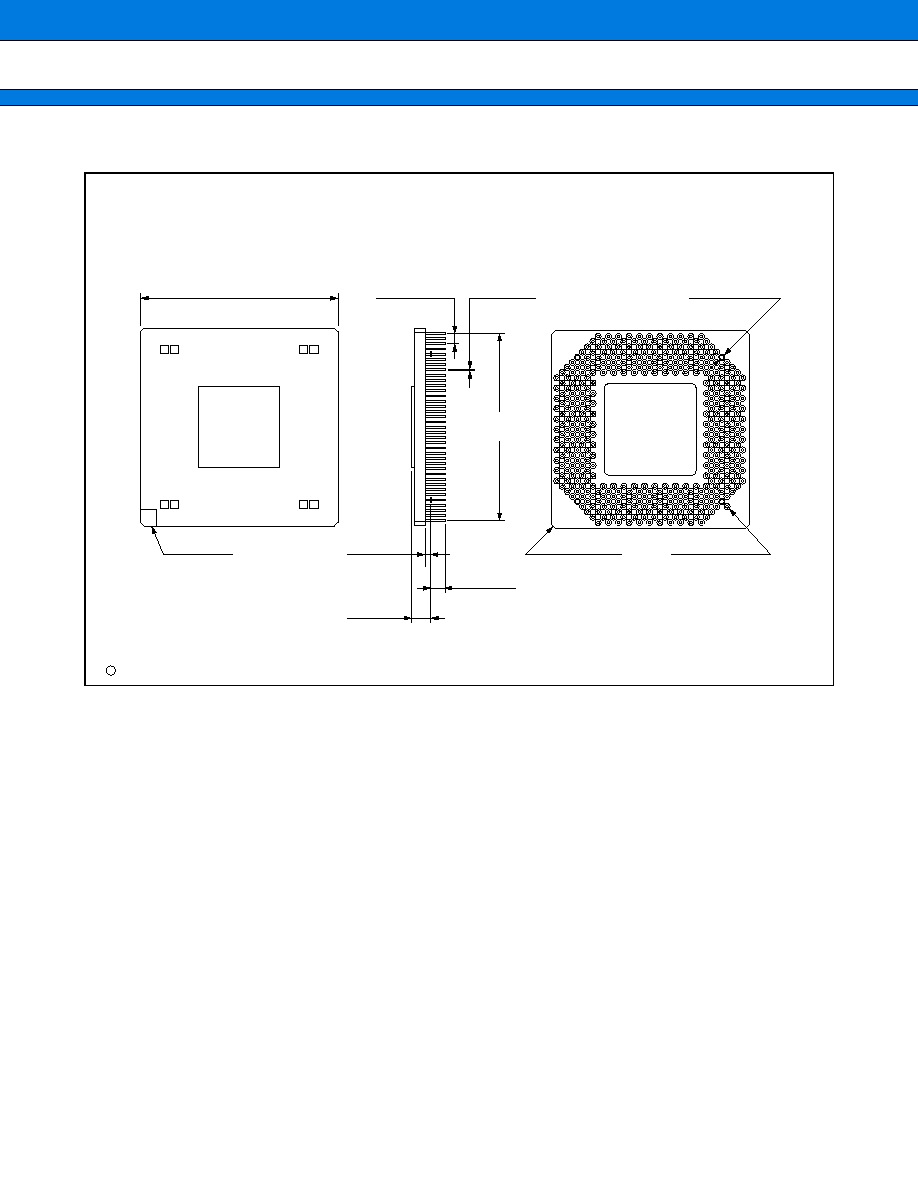

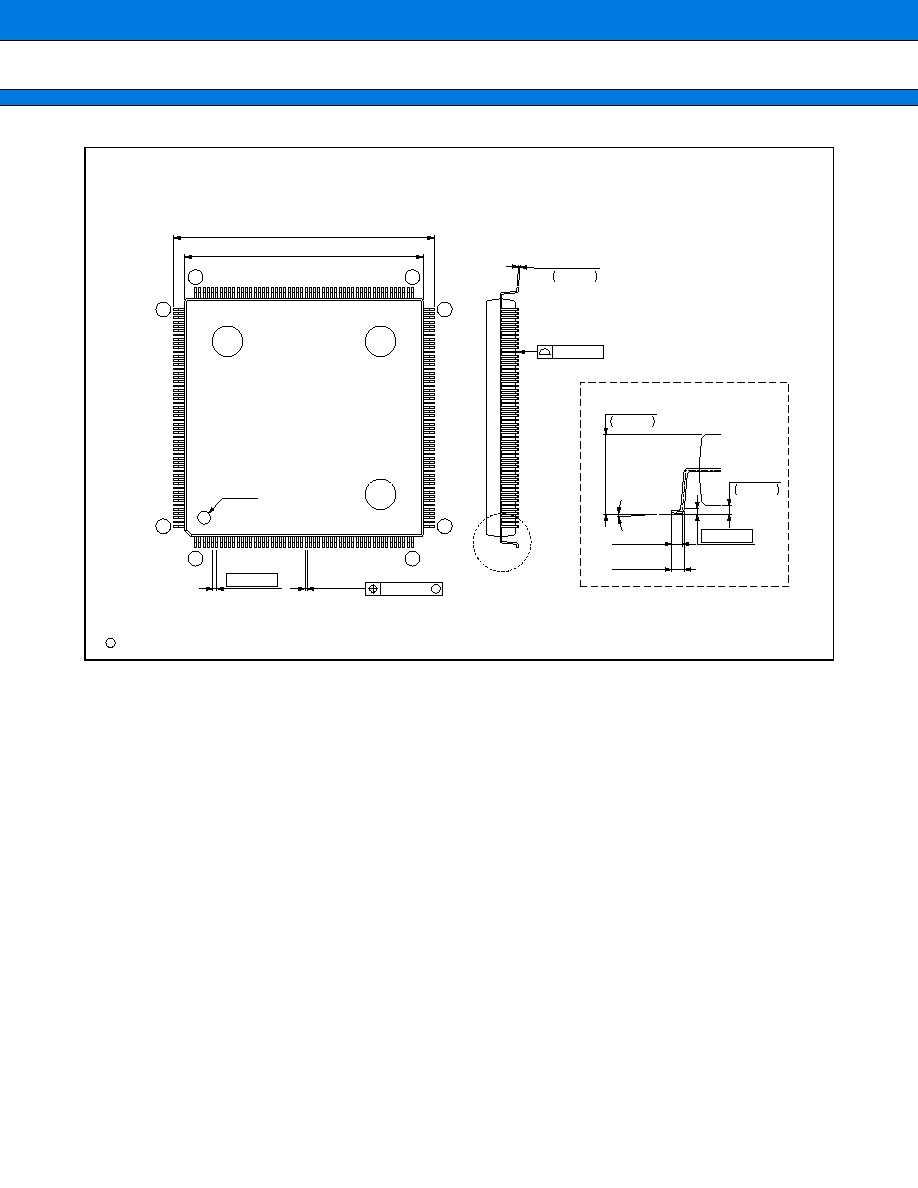

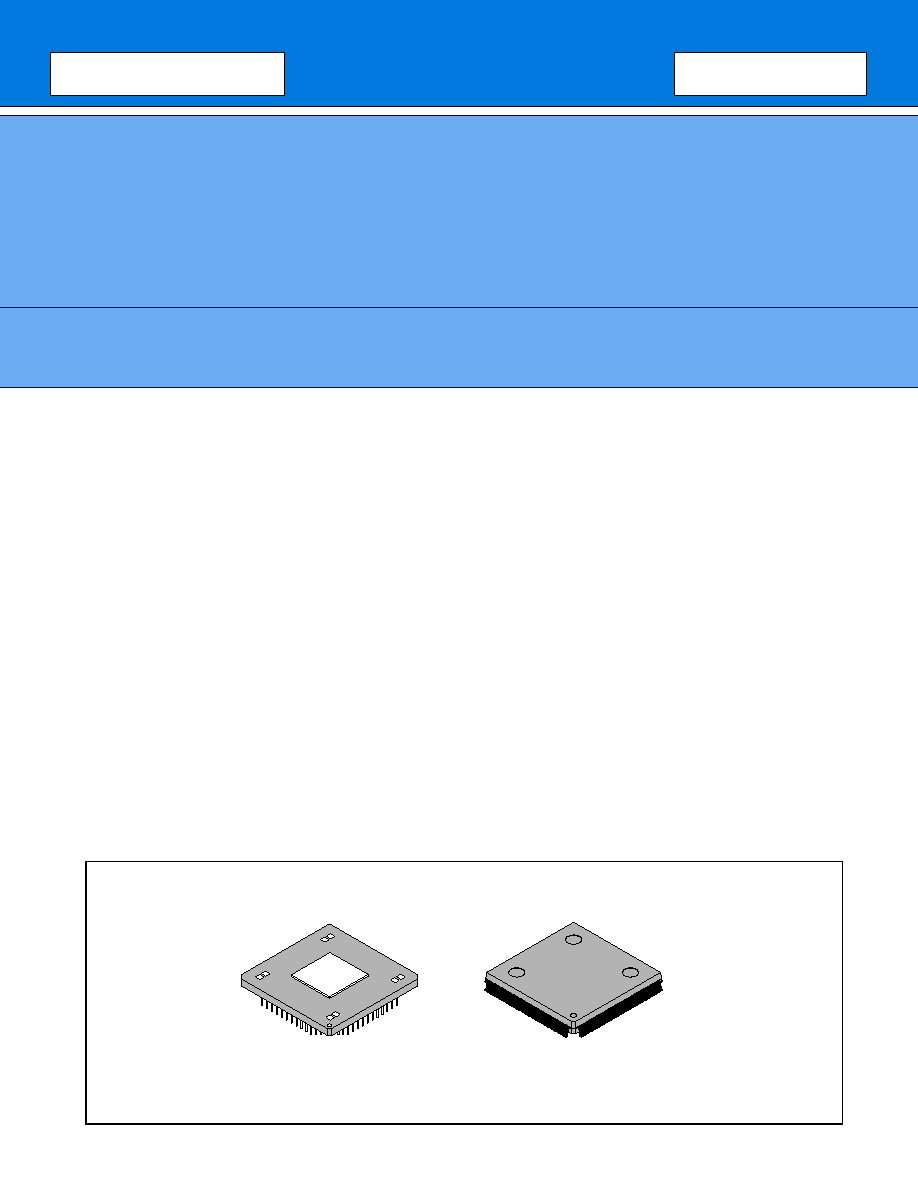

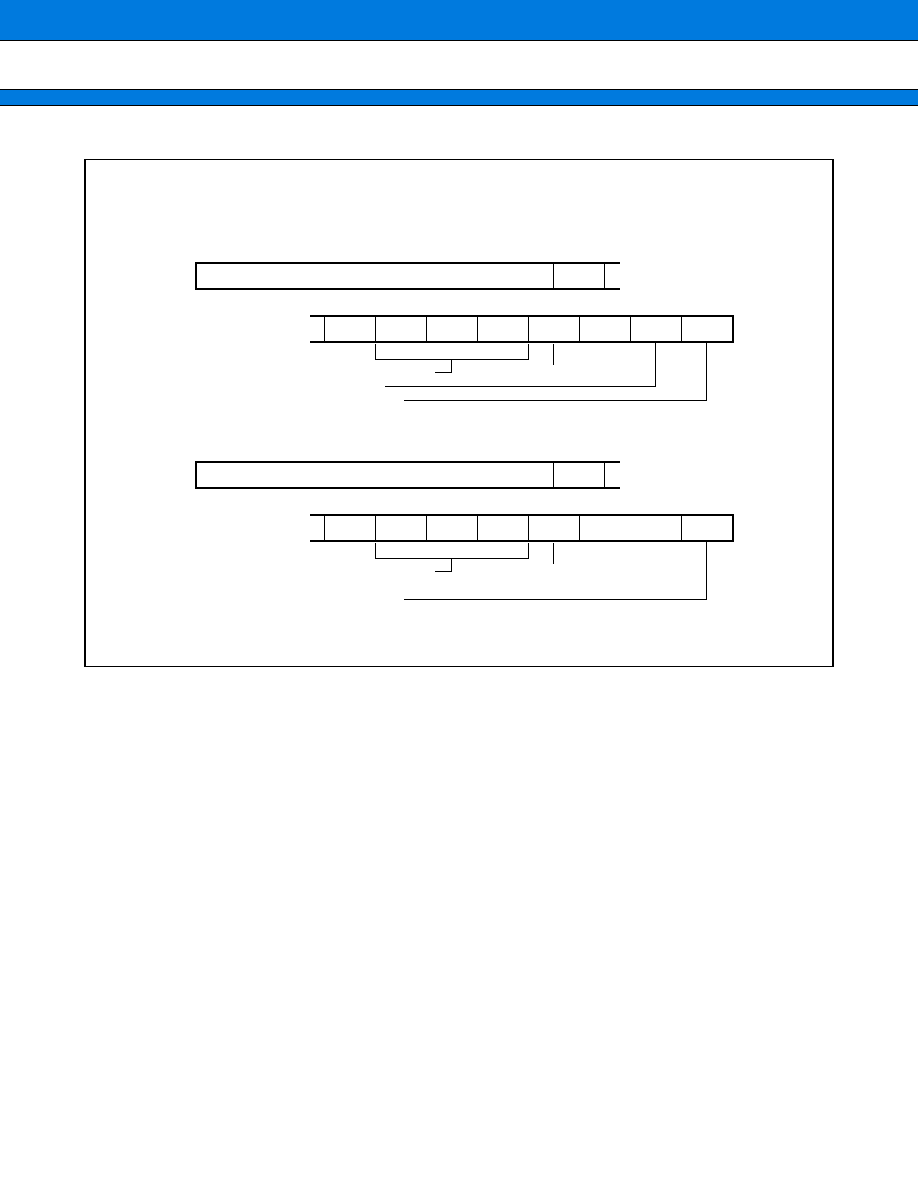

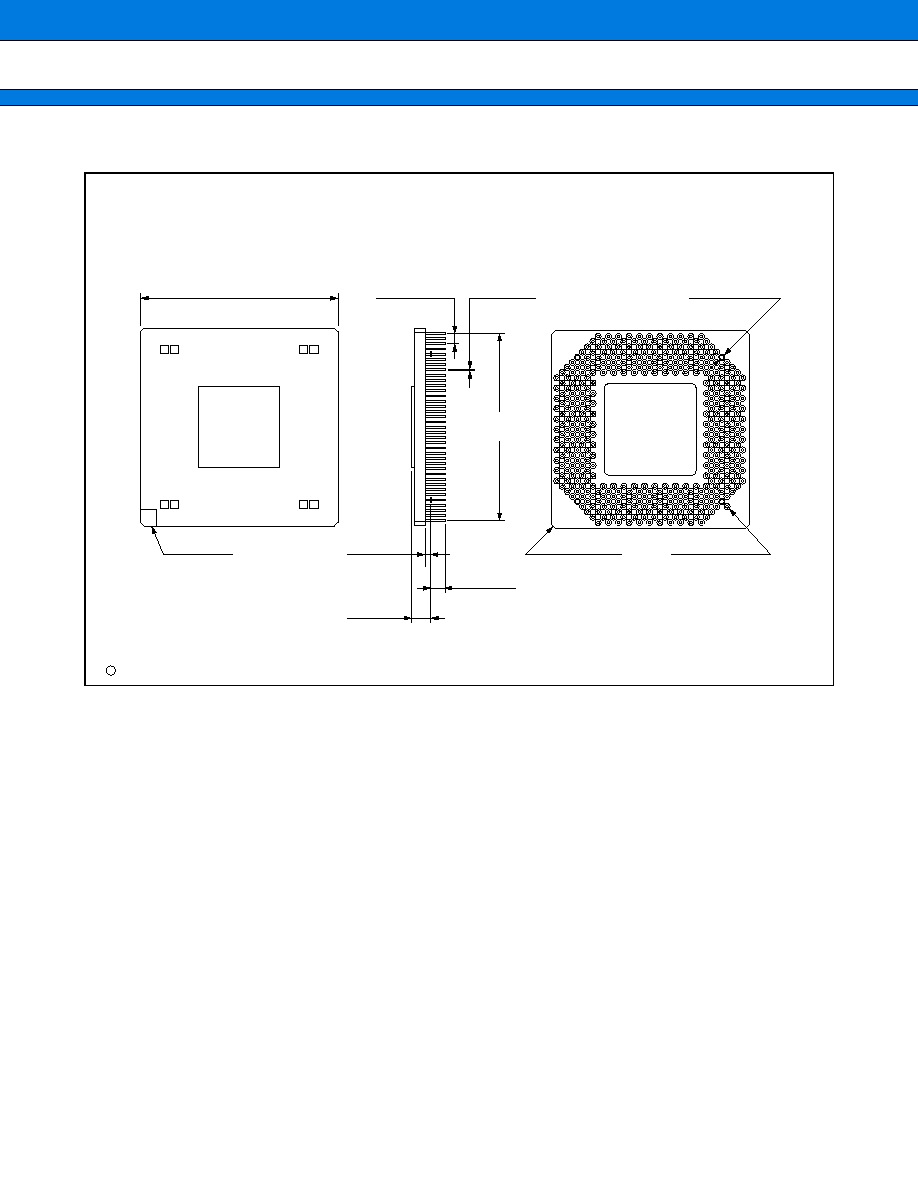

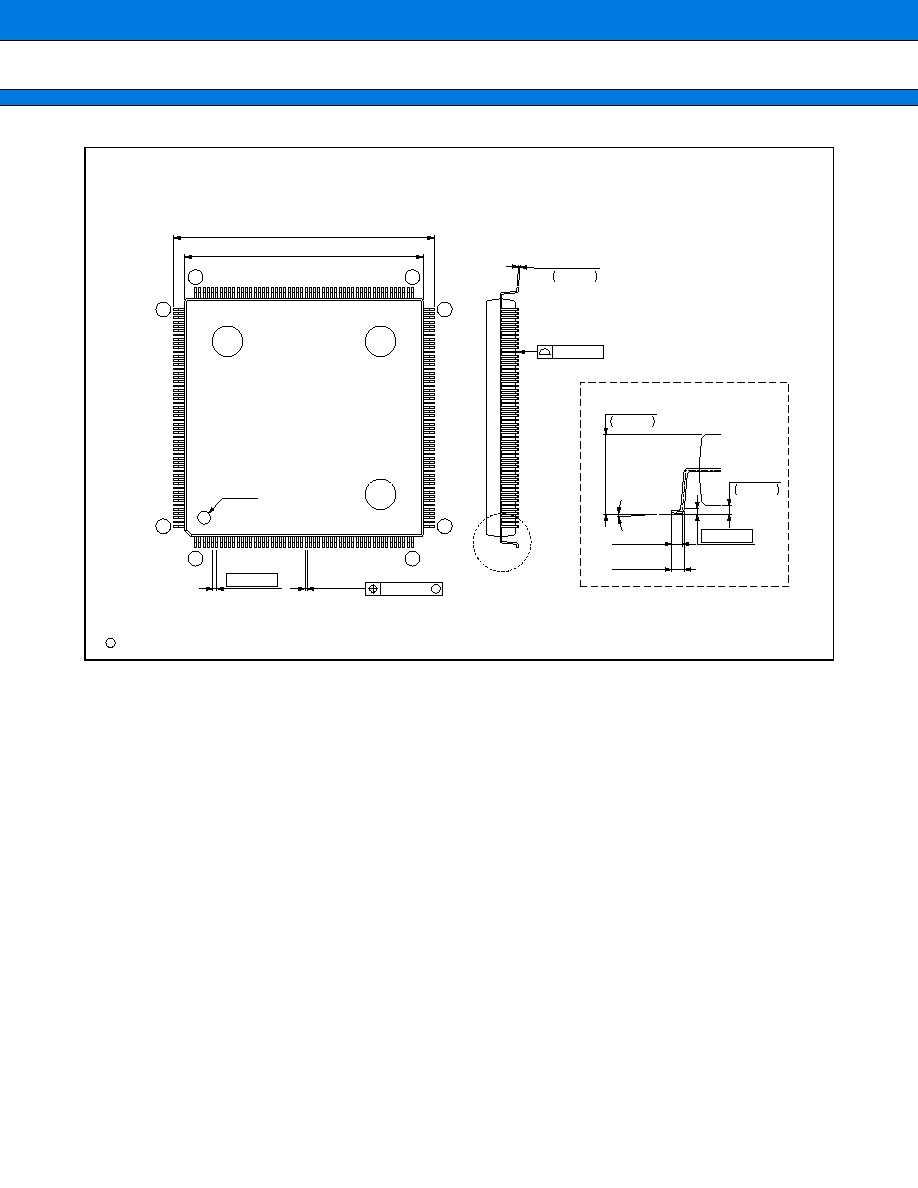

PACKAGE

401-pin Ceramics PGA

208-pin plastic QFP

(PGA-401C-A02)

(FPT-208P-M04)

MB91360G Series

2

(Continued)

∑ External bus interface unit with a wide range of functions

Divides the external memory space into a maximum of eight areas. Chip select signal setting, data bus width

selection (8, 16, 32-bit) , and area size can be specified for each area.

∑

Address bus up to 32 bit wide

∑

Programmable auto-wait function

∑ Internal instruction cache

The MB91360G series contains up to 4-Kbyte instruction cache to improve the execution speed of external

programs.

∑

Two-way set associative caching

∑ DMAC

Direct memory access (DMA) can be used to perform various types of data transfer without going via the CPU.

This improves system performance.

∑

Eight channels (including up to 3 external channels)

∑

Three transfer modes supported : single/block, burst, continuous transfer

∑ Power consumption control mechanisms

The MB91360G series contains a number of functions for controlling the operating clock to reduce power

consumption.

∑

Software control : Sleep and stop/real time clock functions

∑

Hardware control : Hardware standby function

∑

Gear (divider) function : The CPU and peripheral clock frequencies can be set independently.

∑ Contains a range of peripheral functions

∑

UART, U-timer

∑

Real Time Clock (with optional subclock operation and subclock calibration module)

∑

Stepper Motor Control

∑

Sound Generator

∑

Serial IO (SIO) , SIO-Prescaler

∑

Power Down Reset

∑

Alarm Comparator

∑

IO-Timer

∑

I

2

C Interface

∑

10 Bit D/A Converter

∑

CAN Interface

∑

10-bit A/D converter

∑

16-bit reload timer

∑

16-bit PWM timer

∑

Watchdog timer

∑

Bit search module

∑

Interrupt controller

∑

External interrupt inputs

∑

I/O port function

∑ Interrupt levels

"16 maskable interrupt levels"

∑ Other

∑

Power supply voltage

∑

5 V power supply used, the internal regulator creates internal supply of 3.3 V

∑

Package : MB91FV360GA uses a PGA401 package, MB91F361GA and MB91F362GA are delivered in a

QFP208 package.

MB91360G Series

3

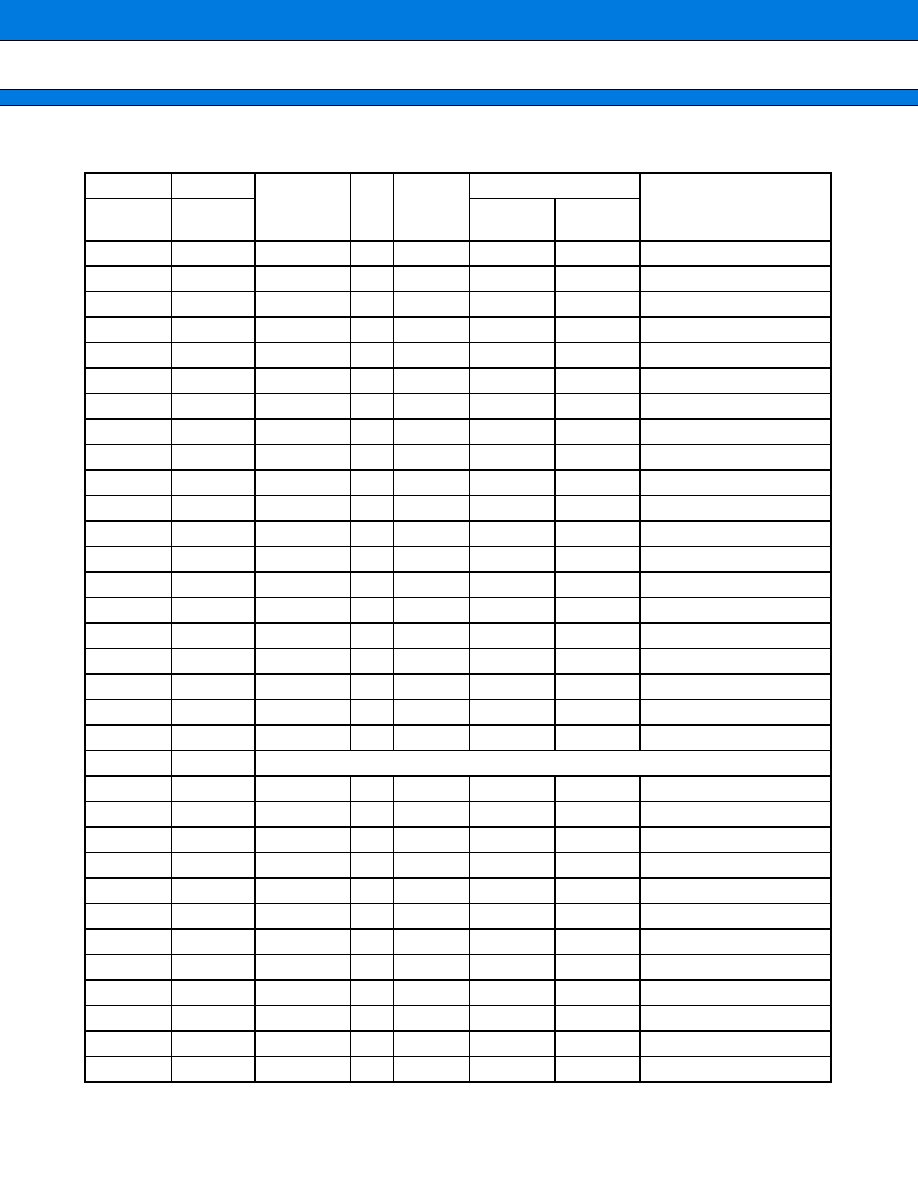

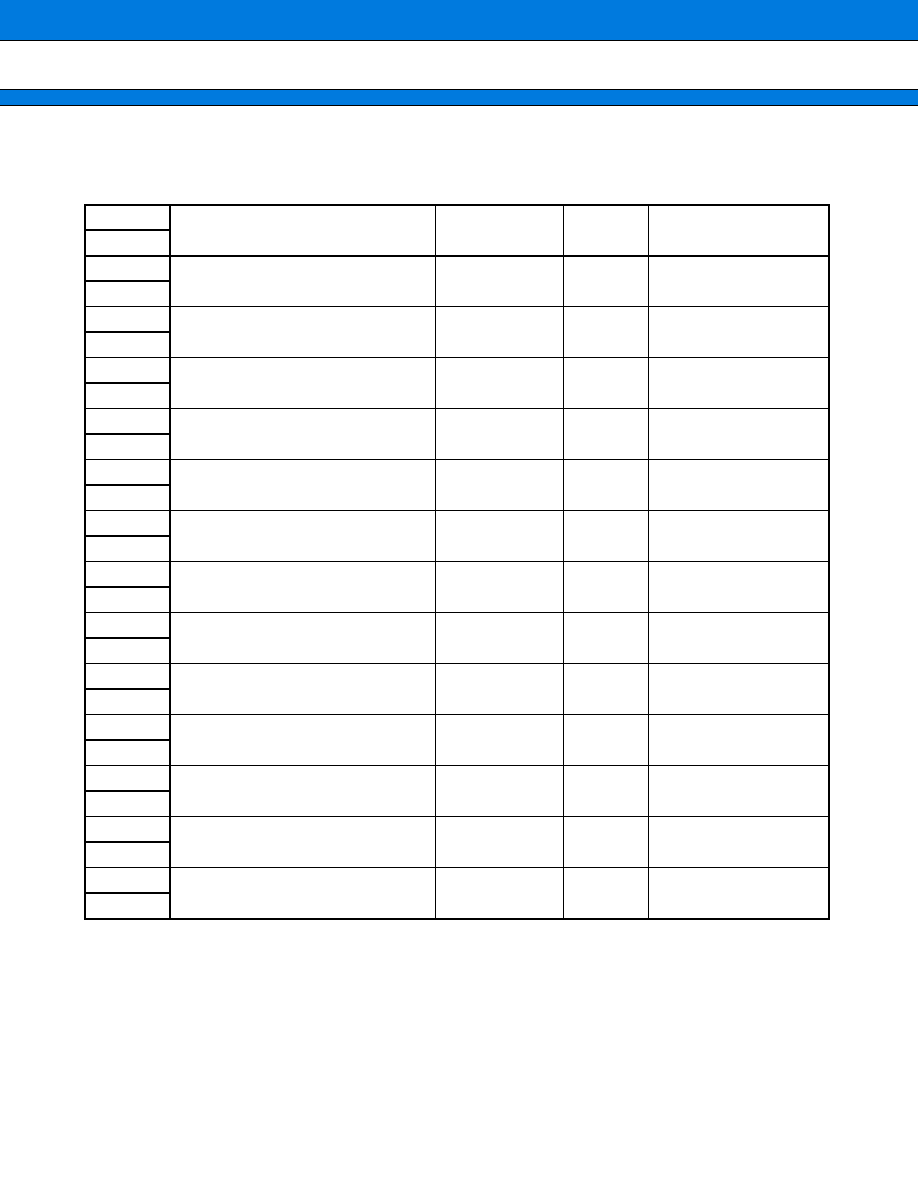

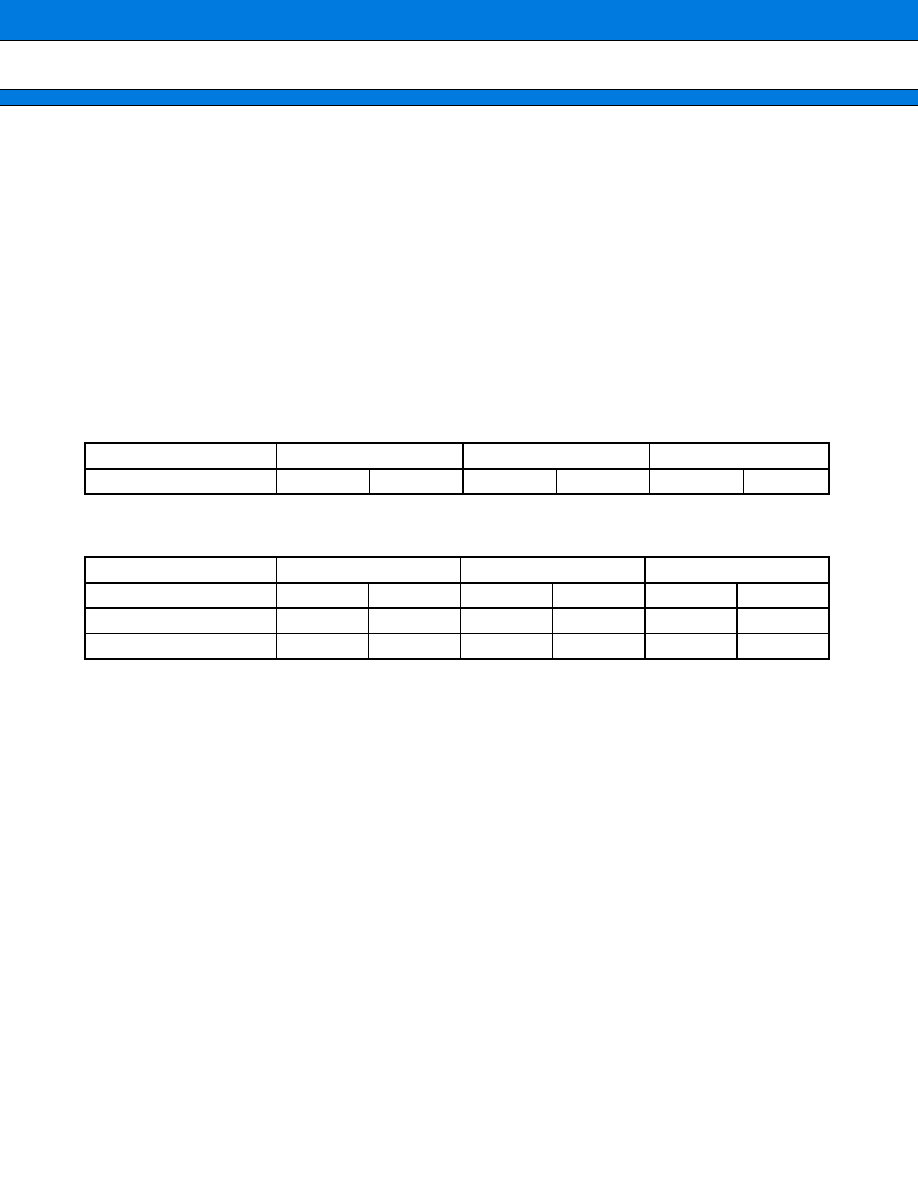

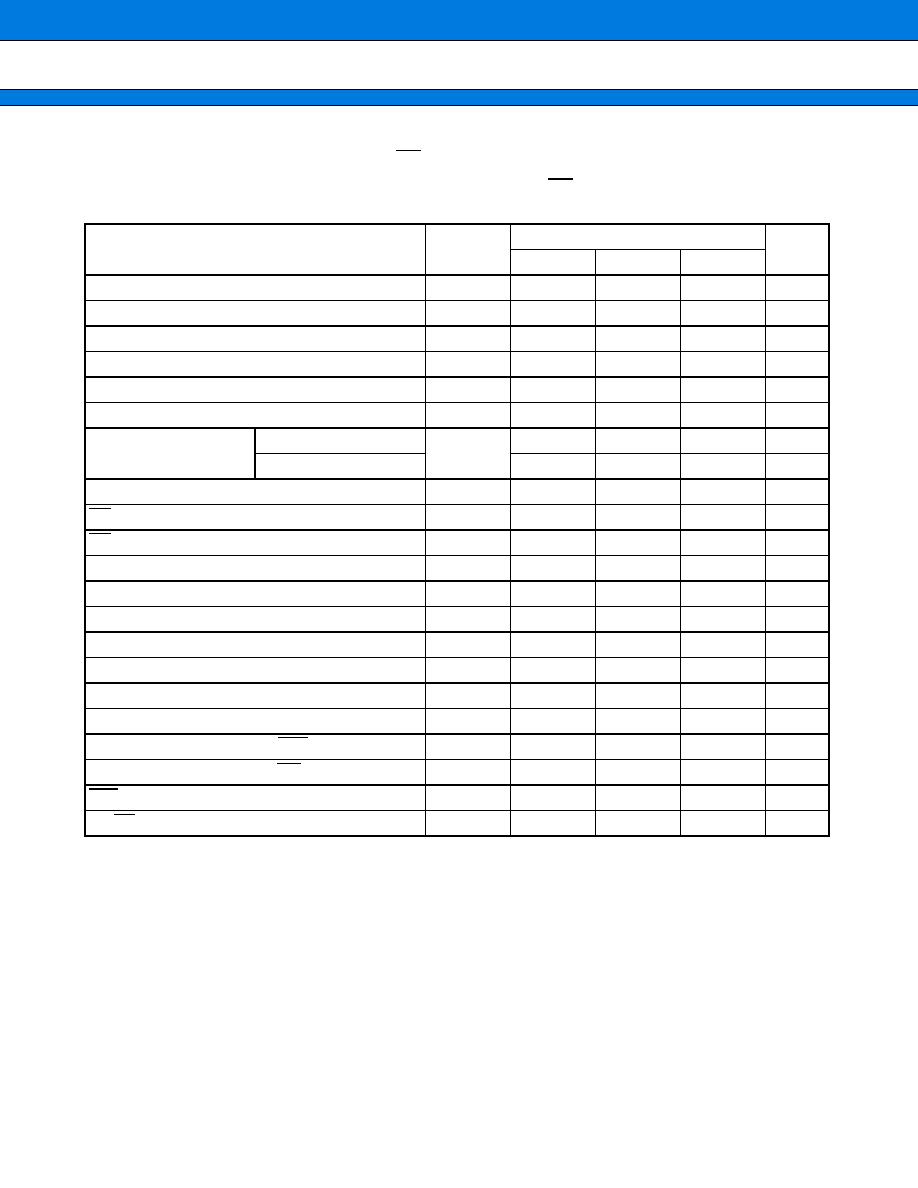

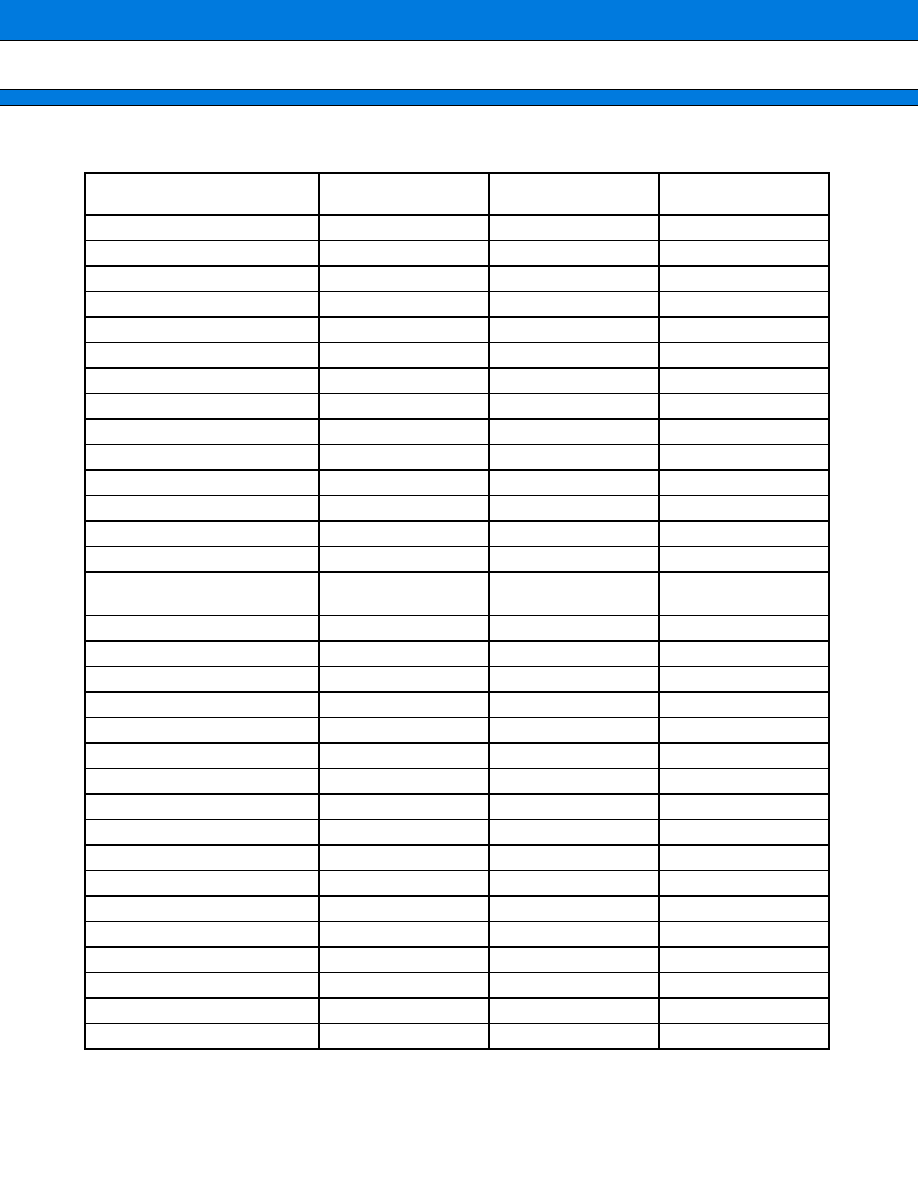

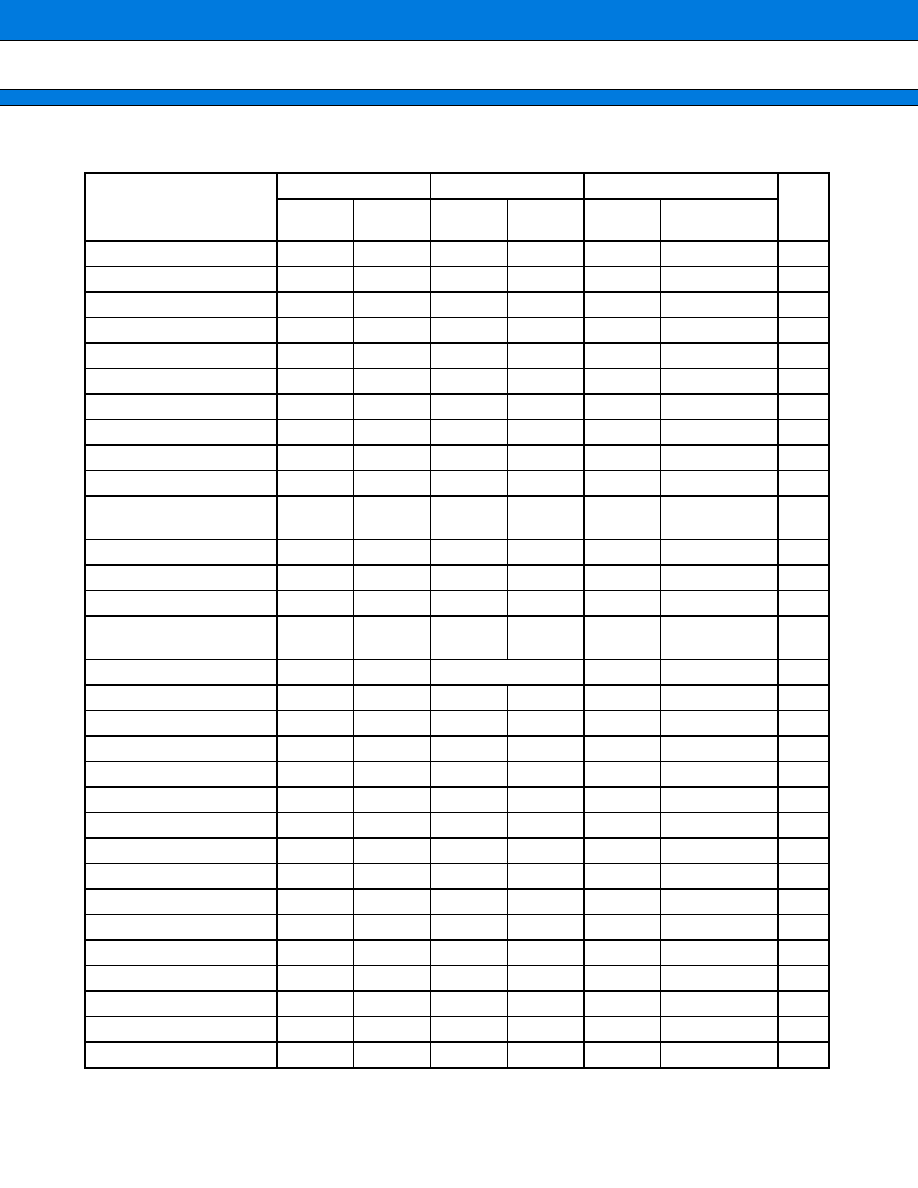

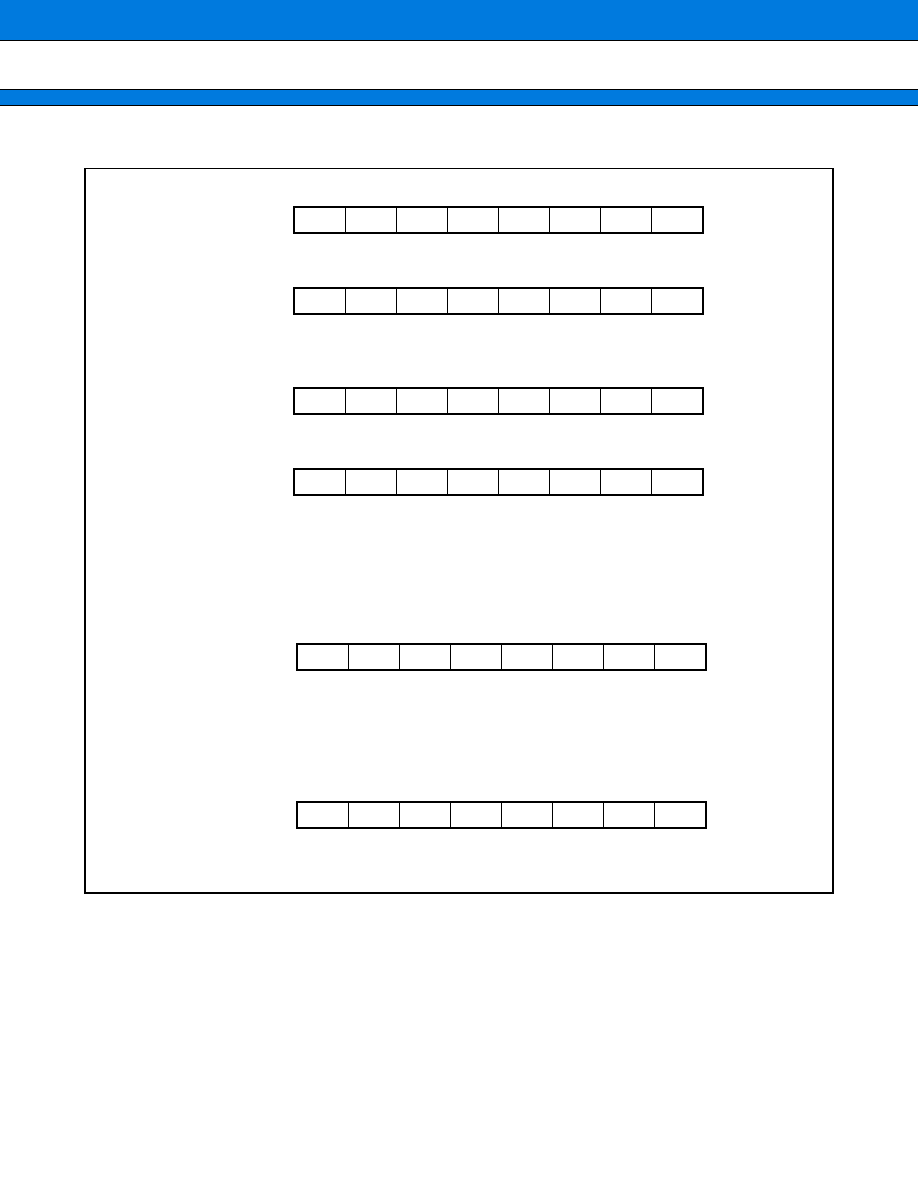

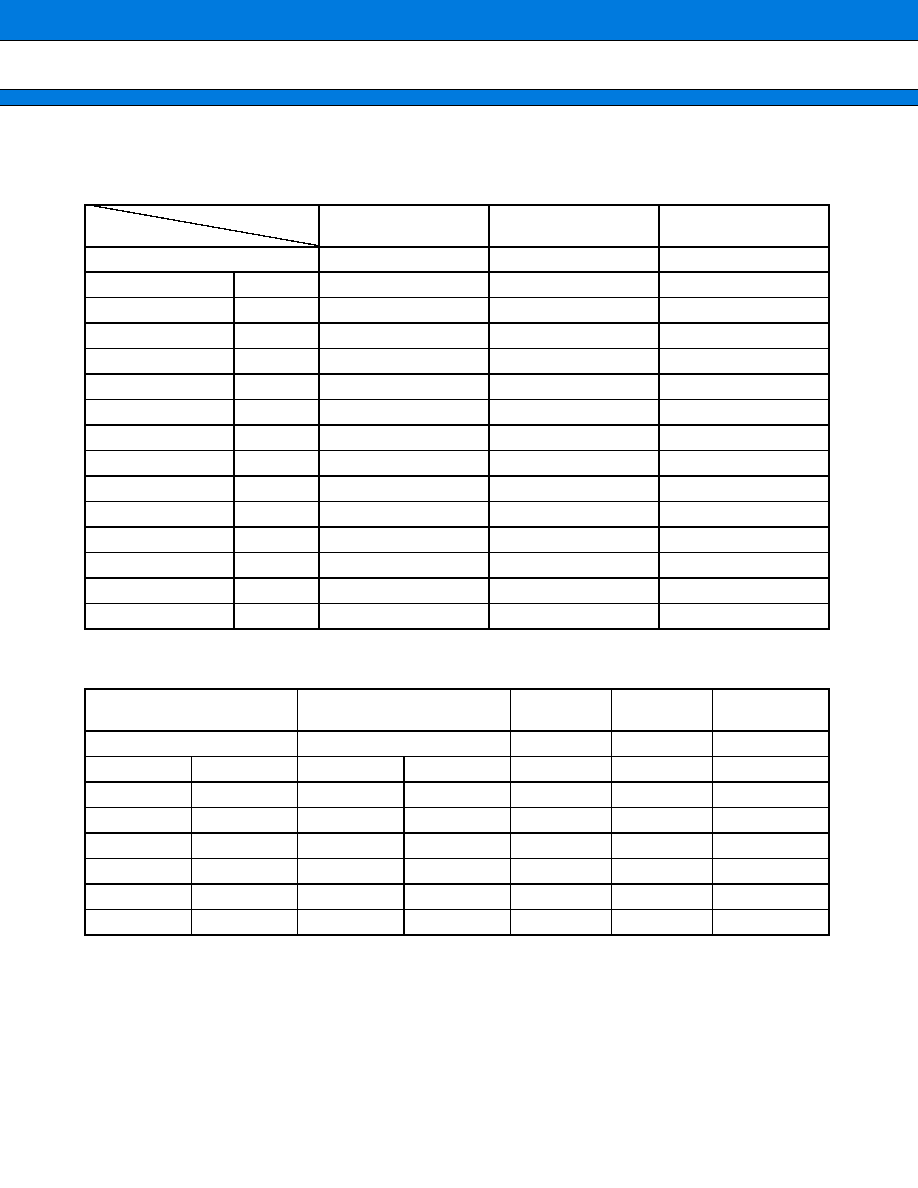

s

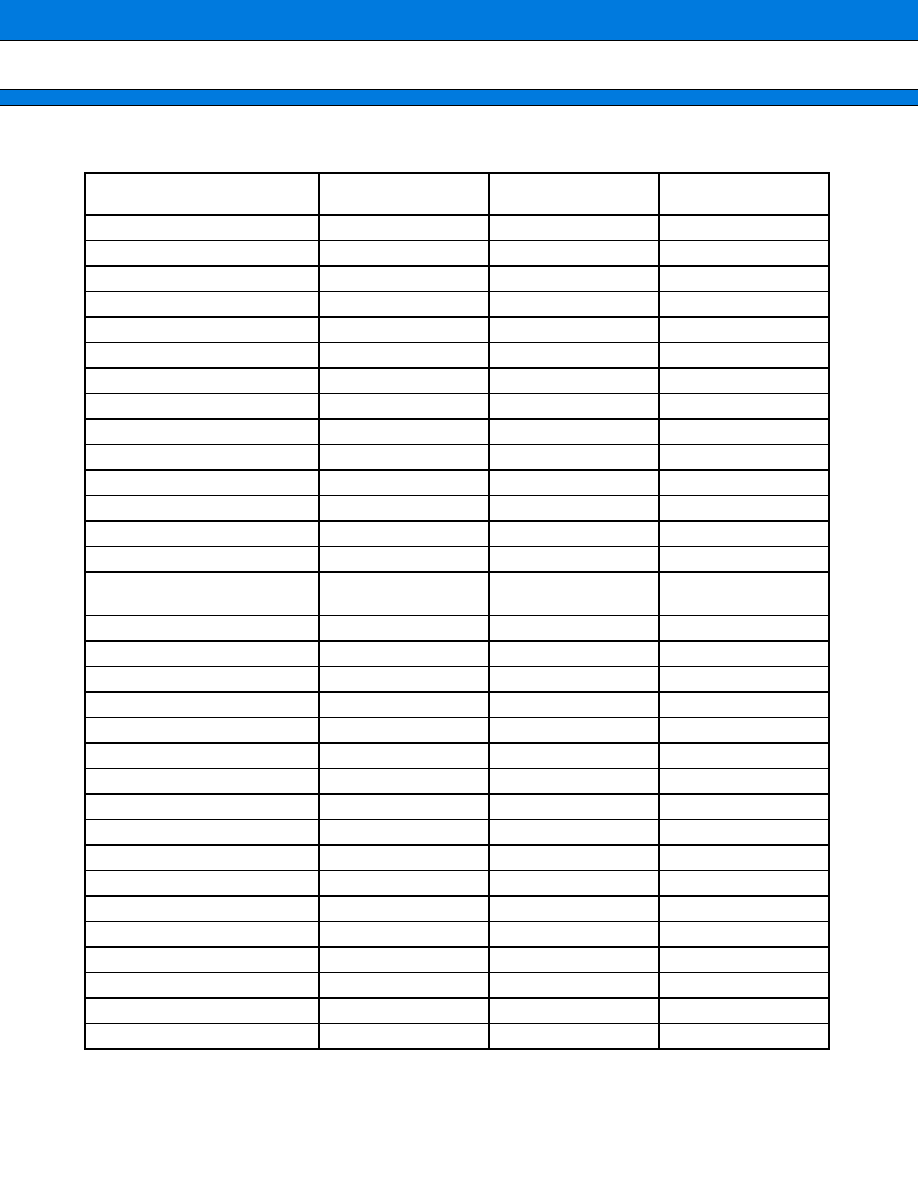

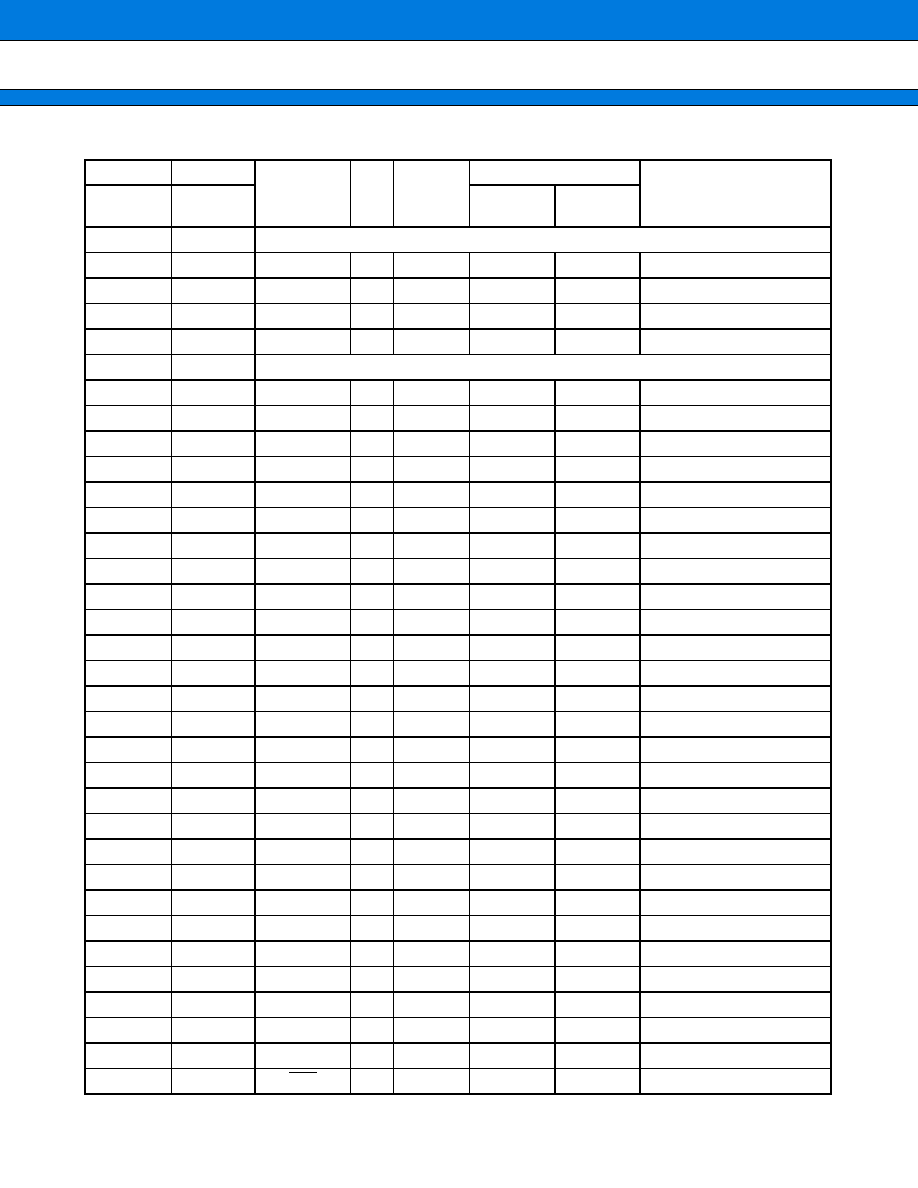

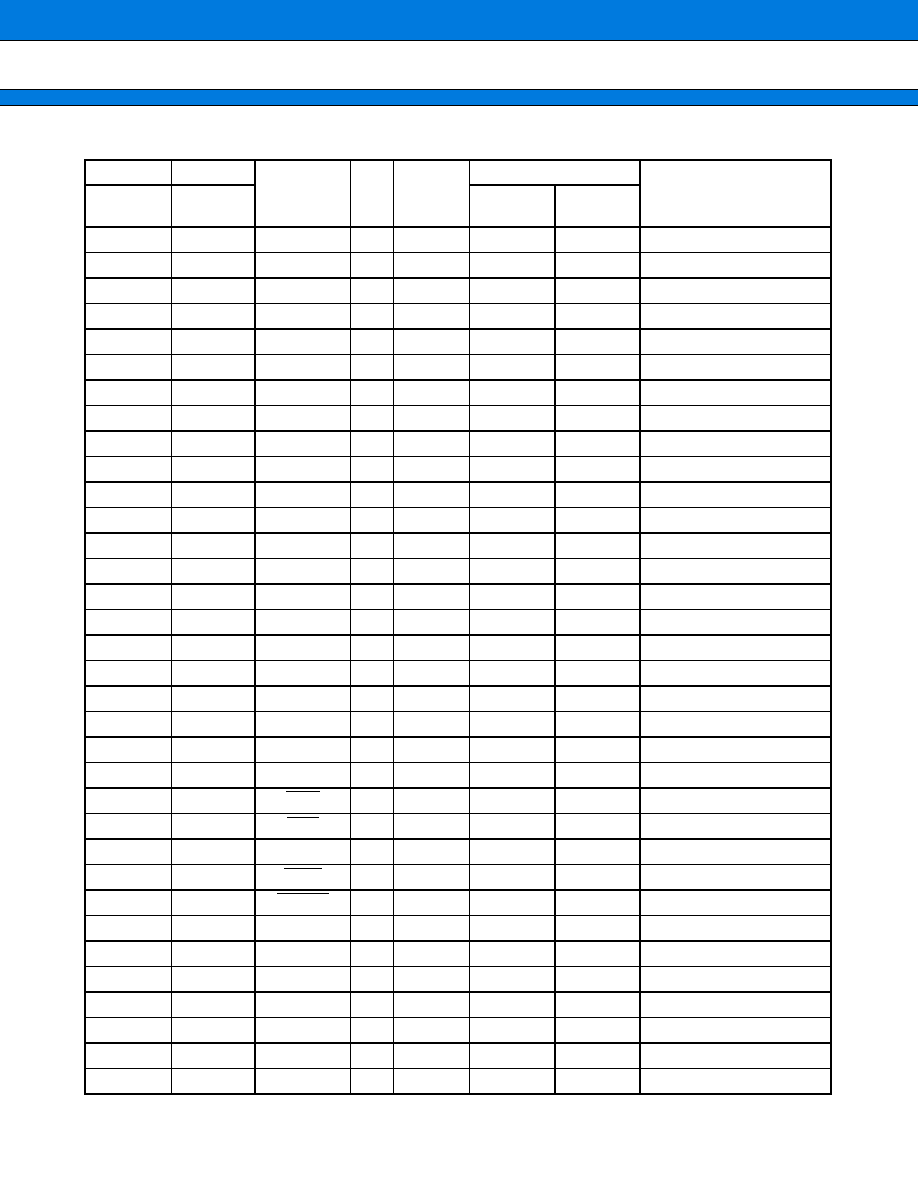

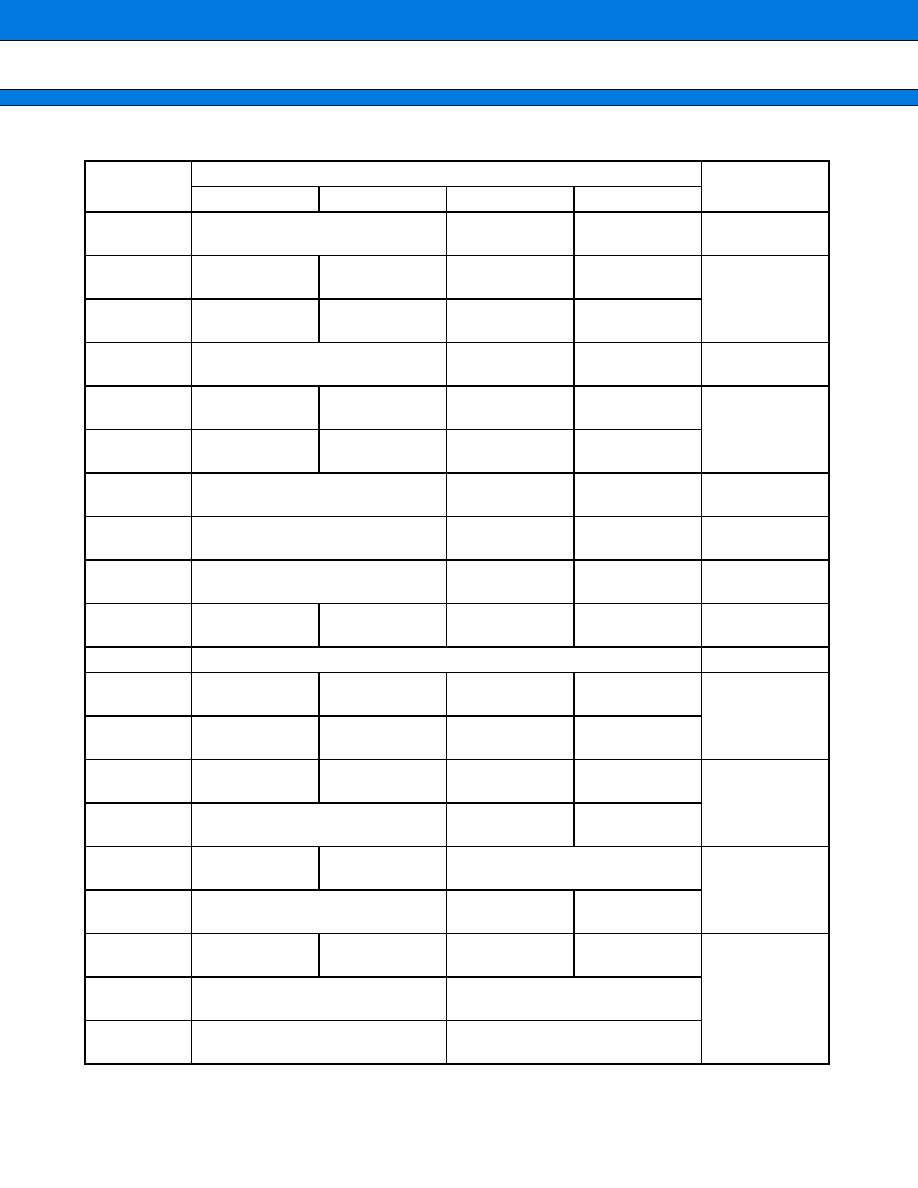

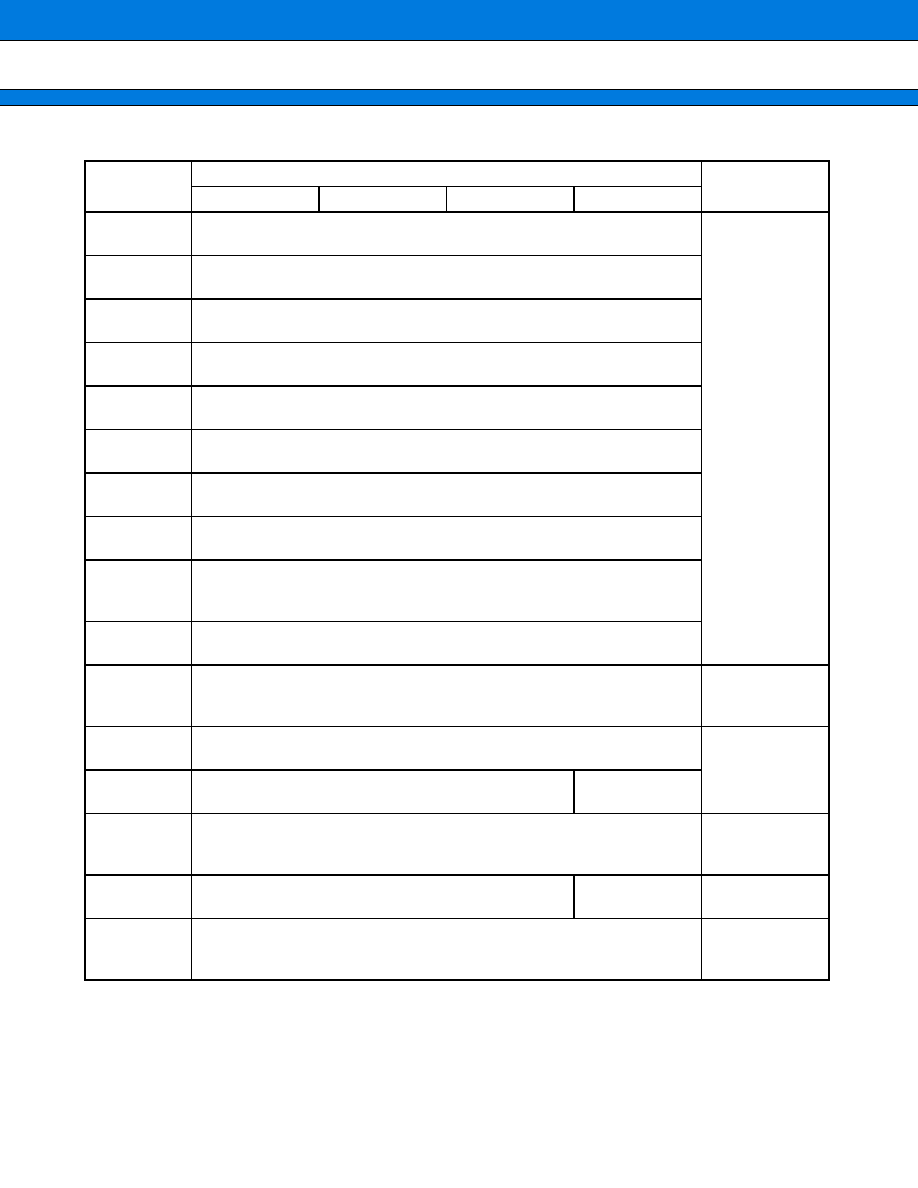

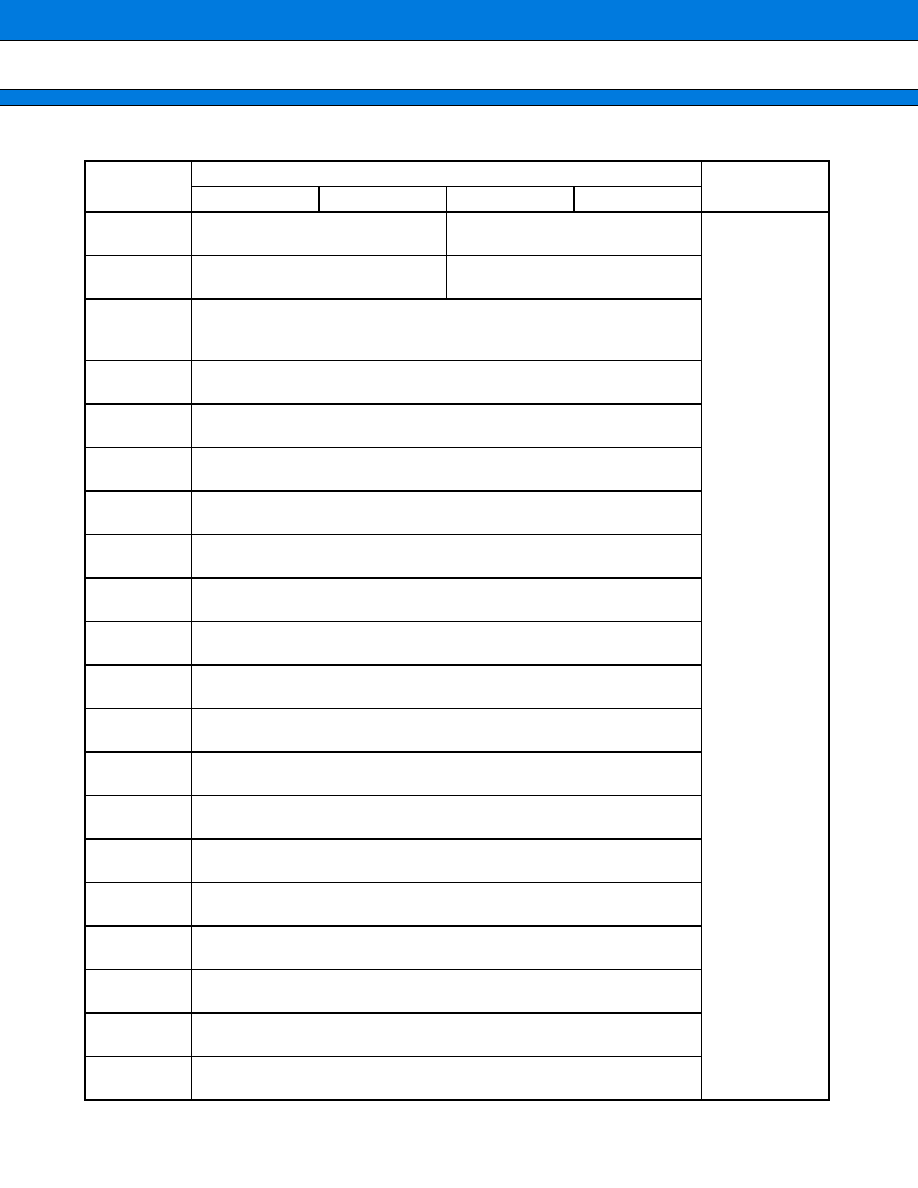

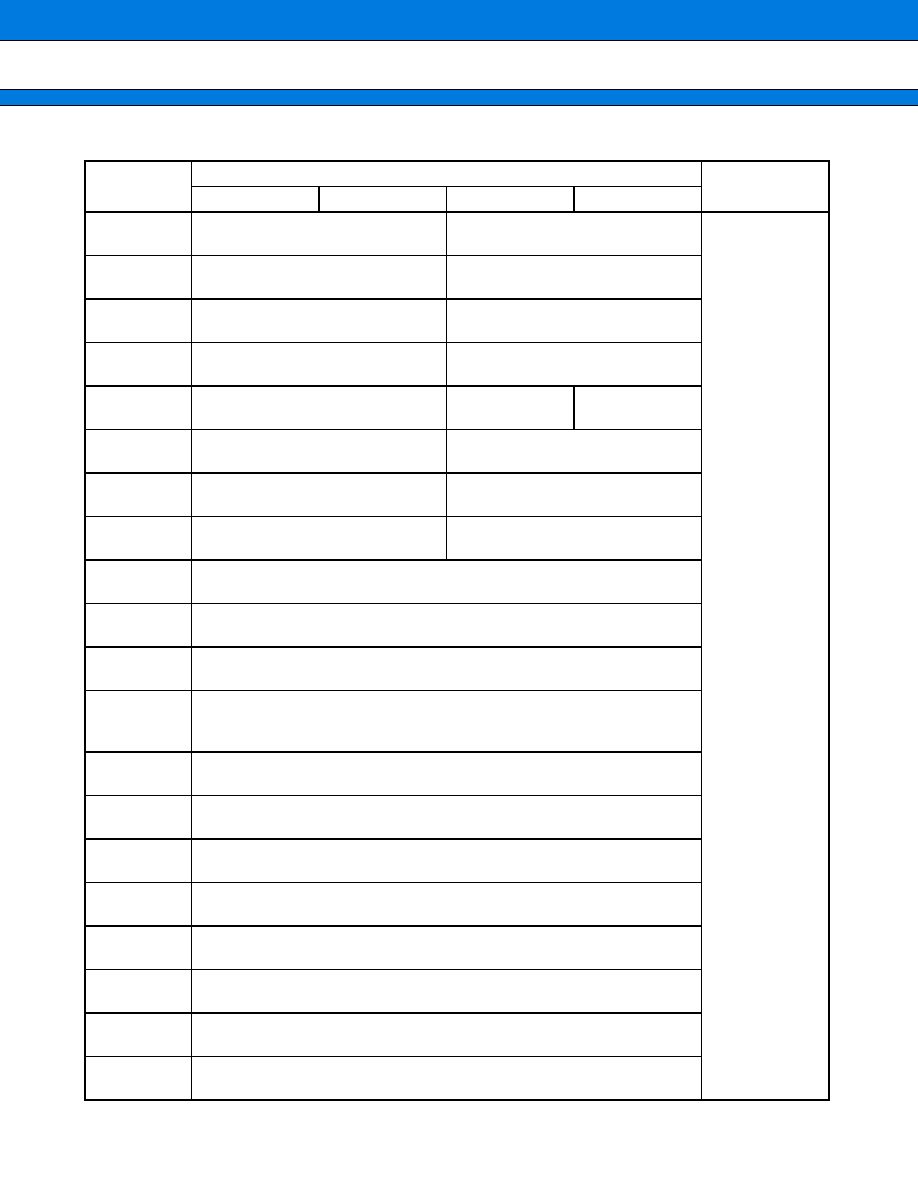

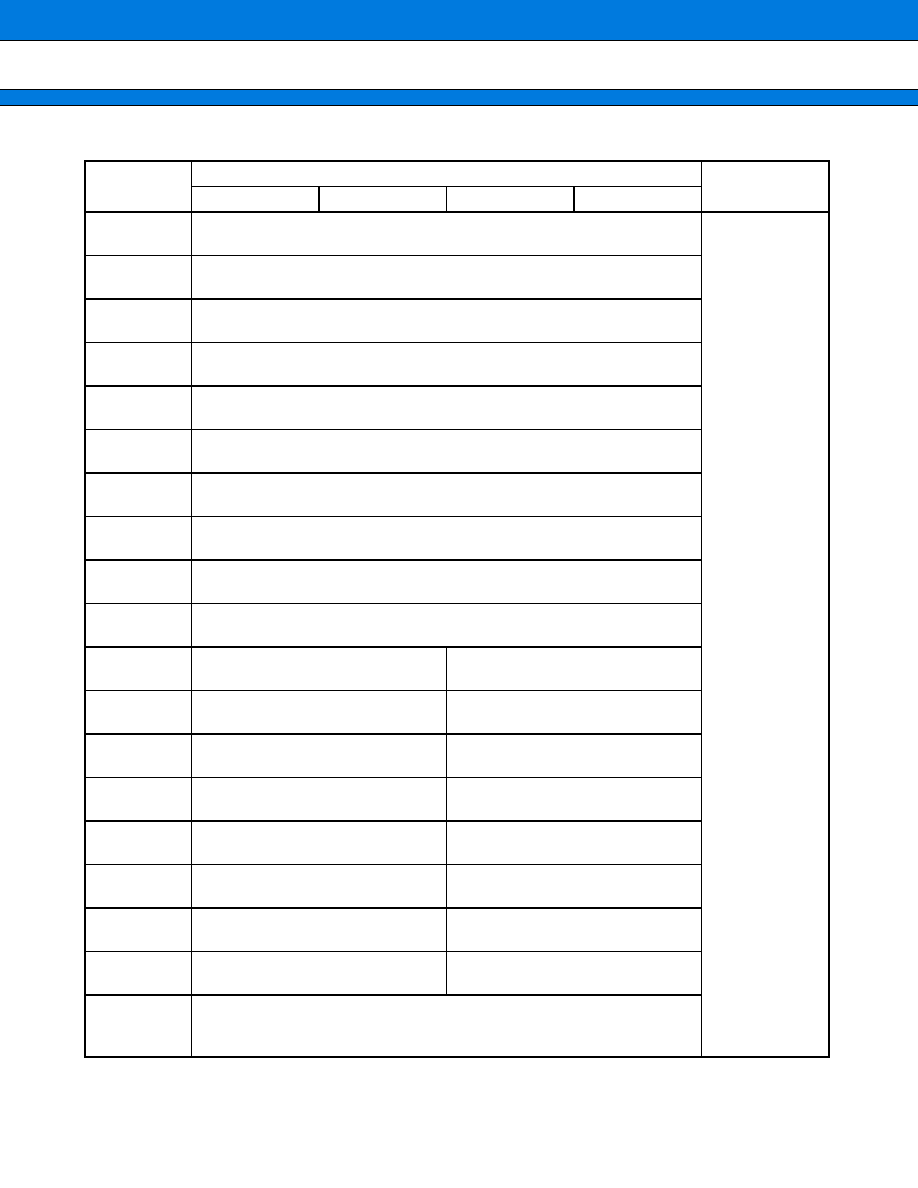

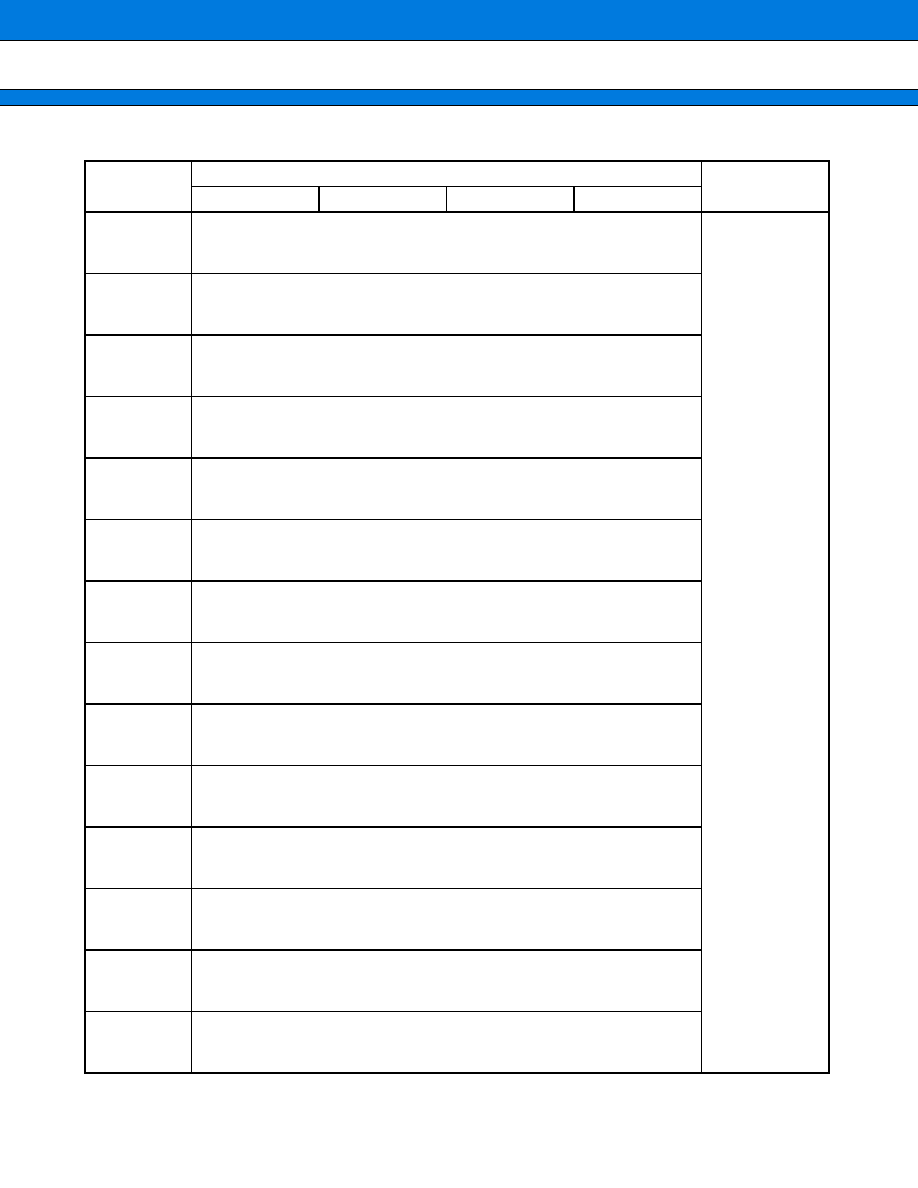

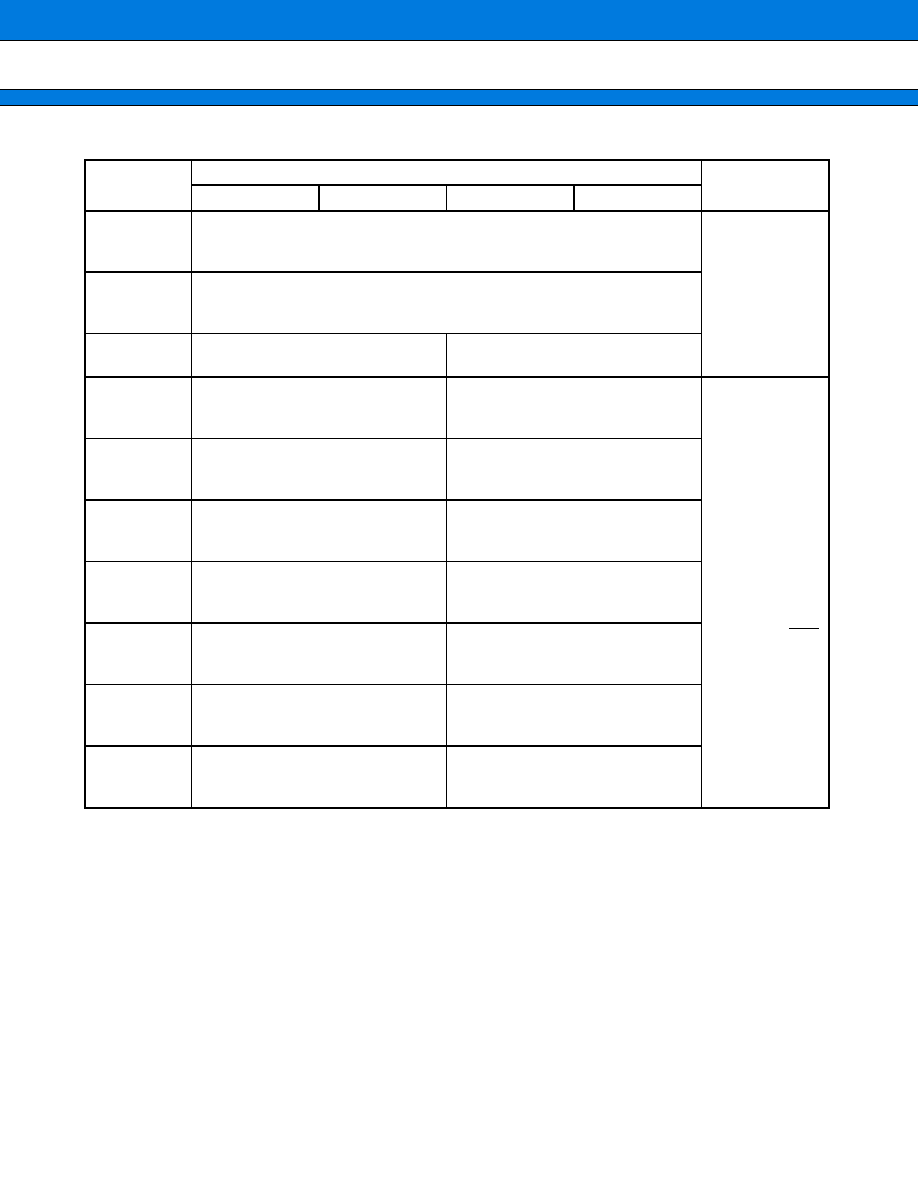

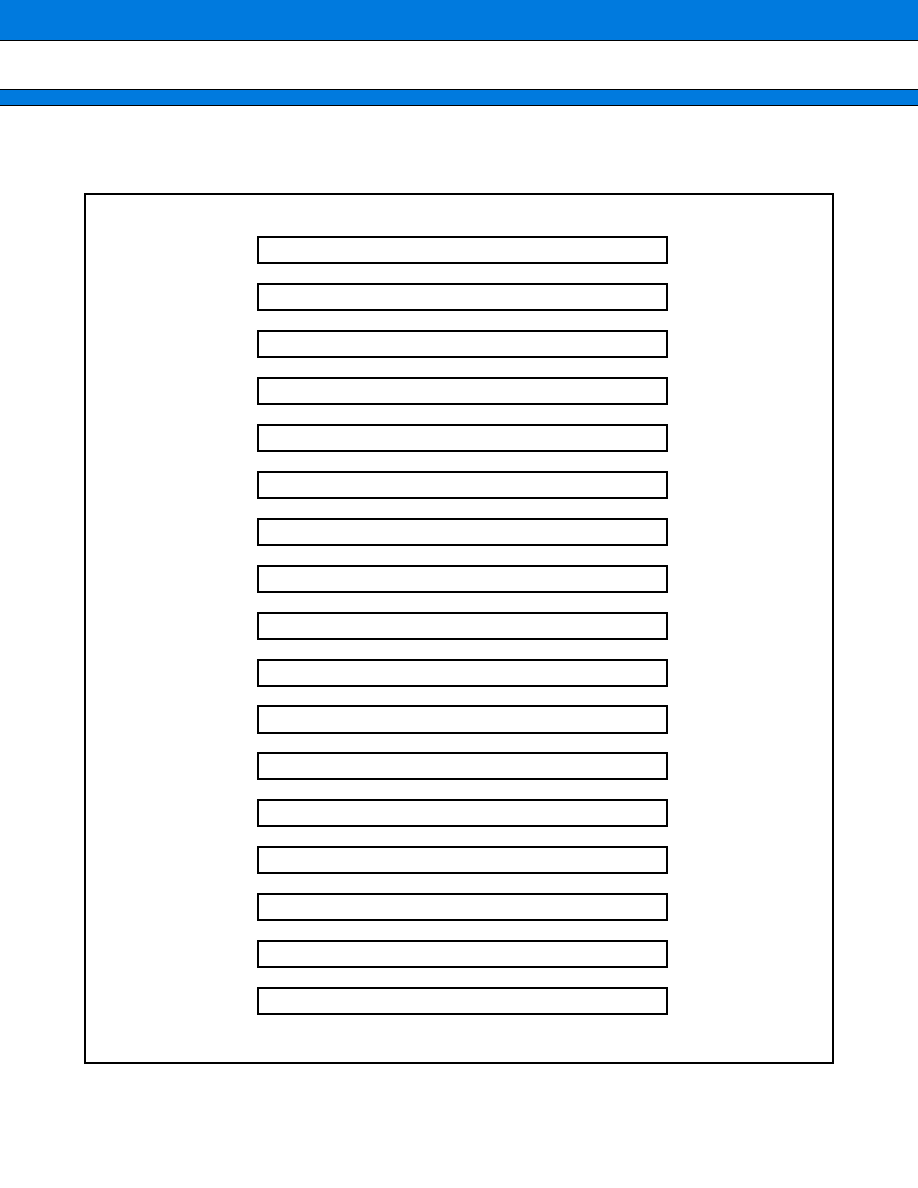

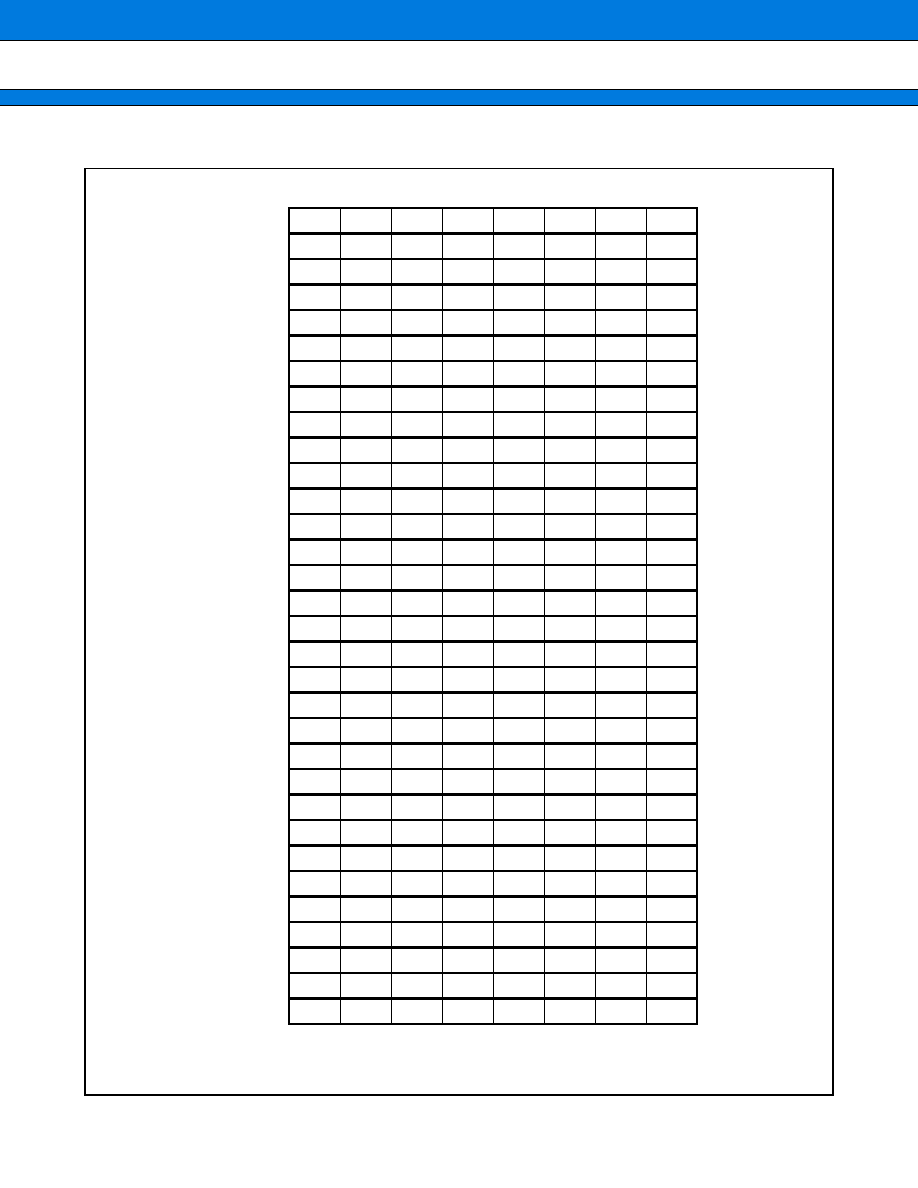

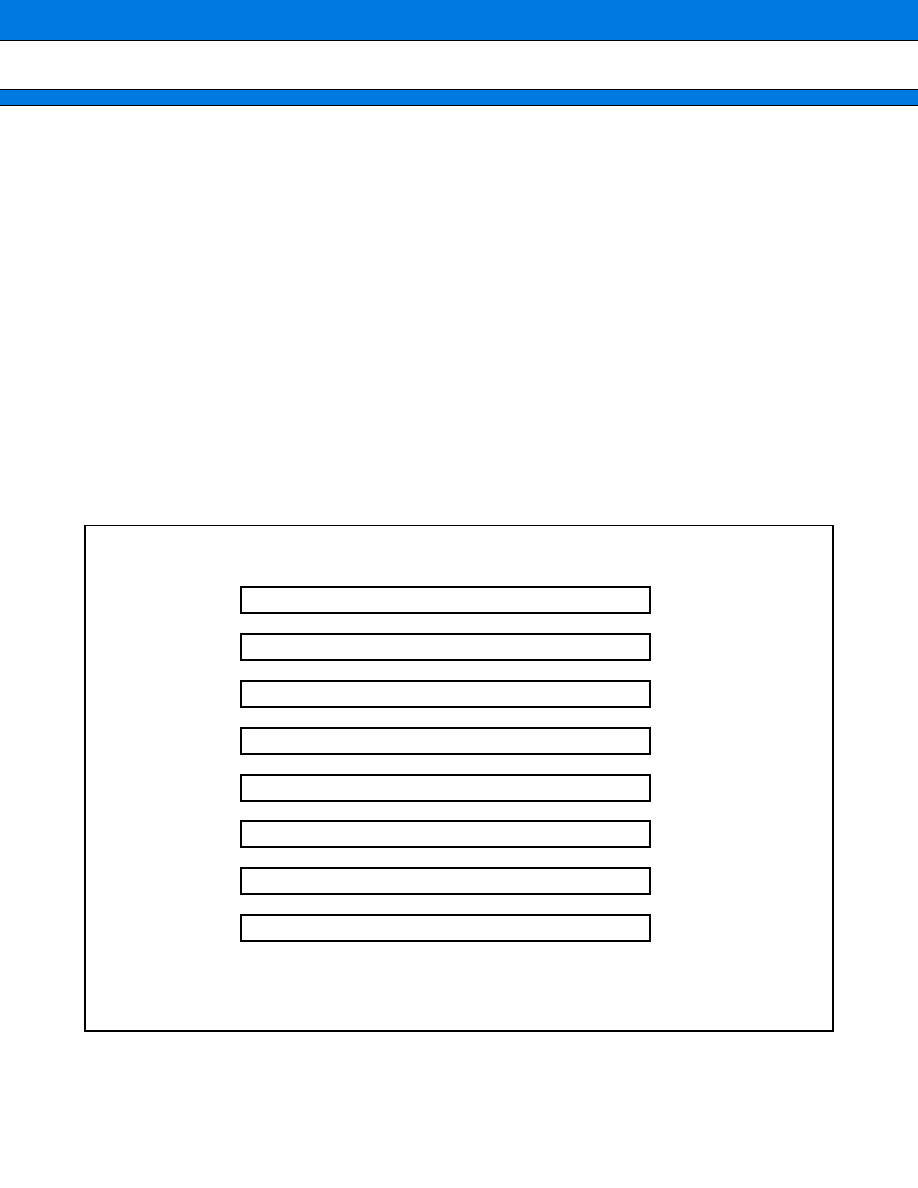

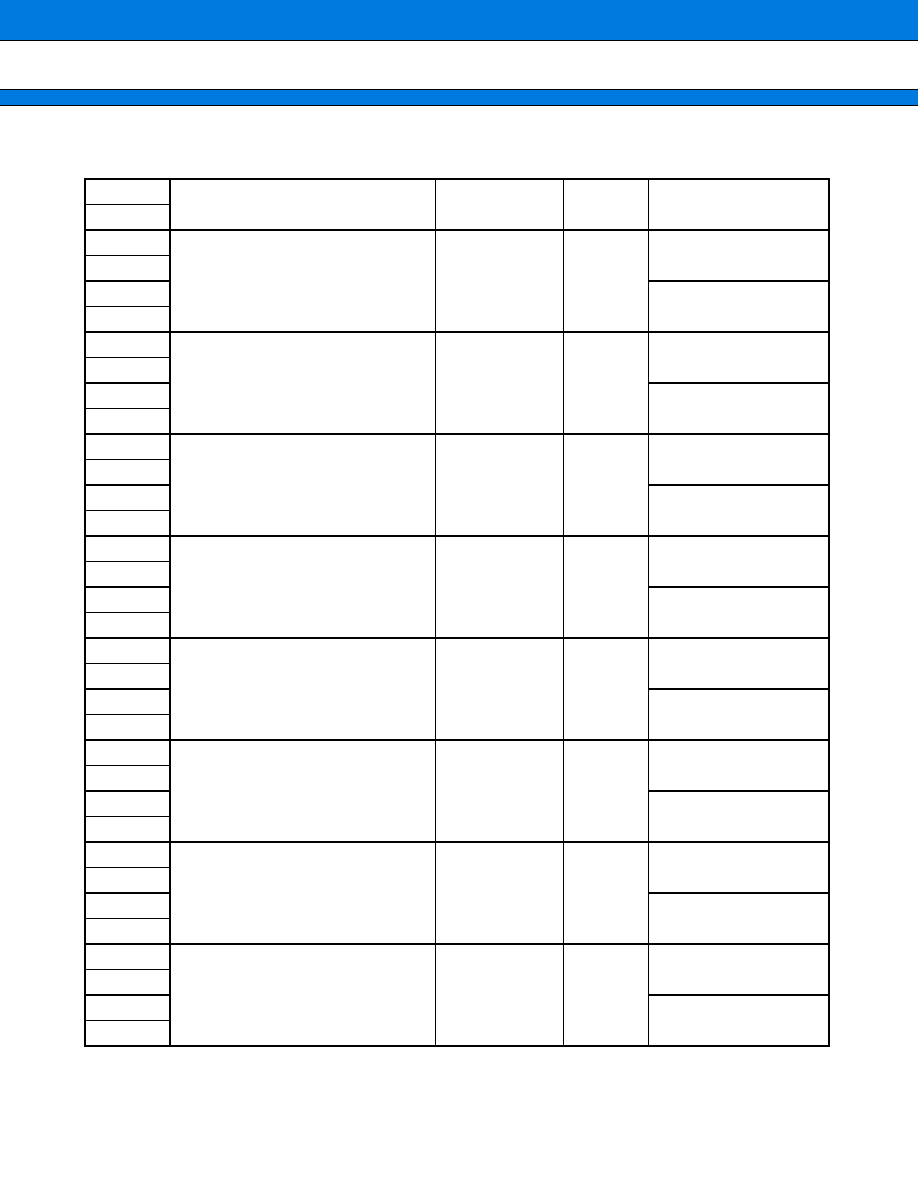

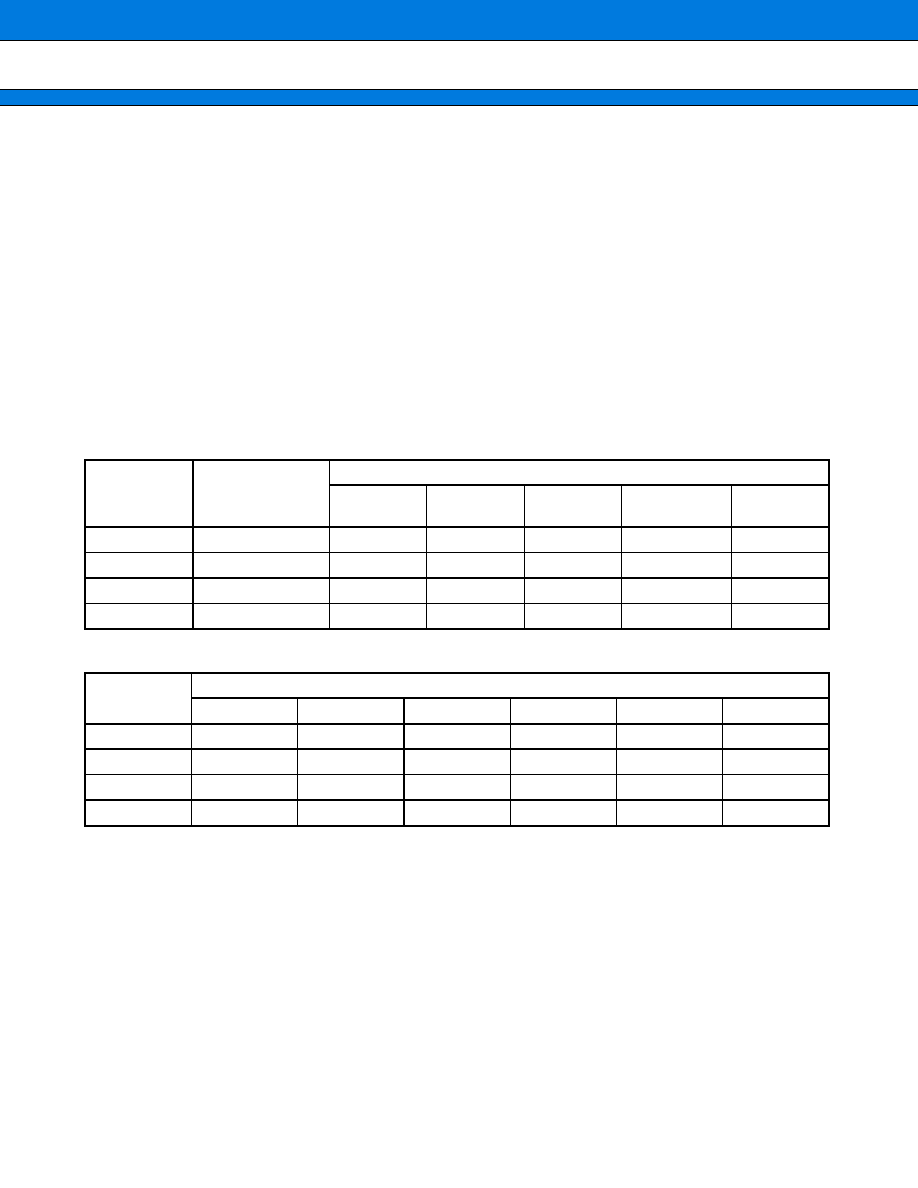

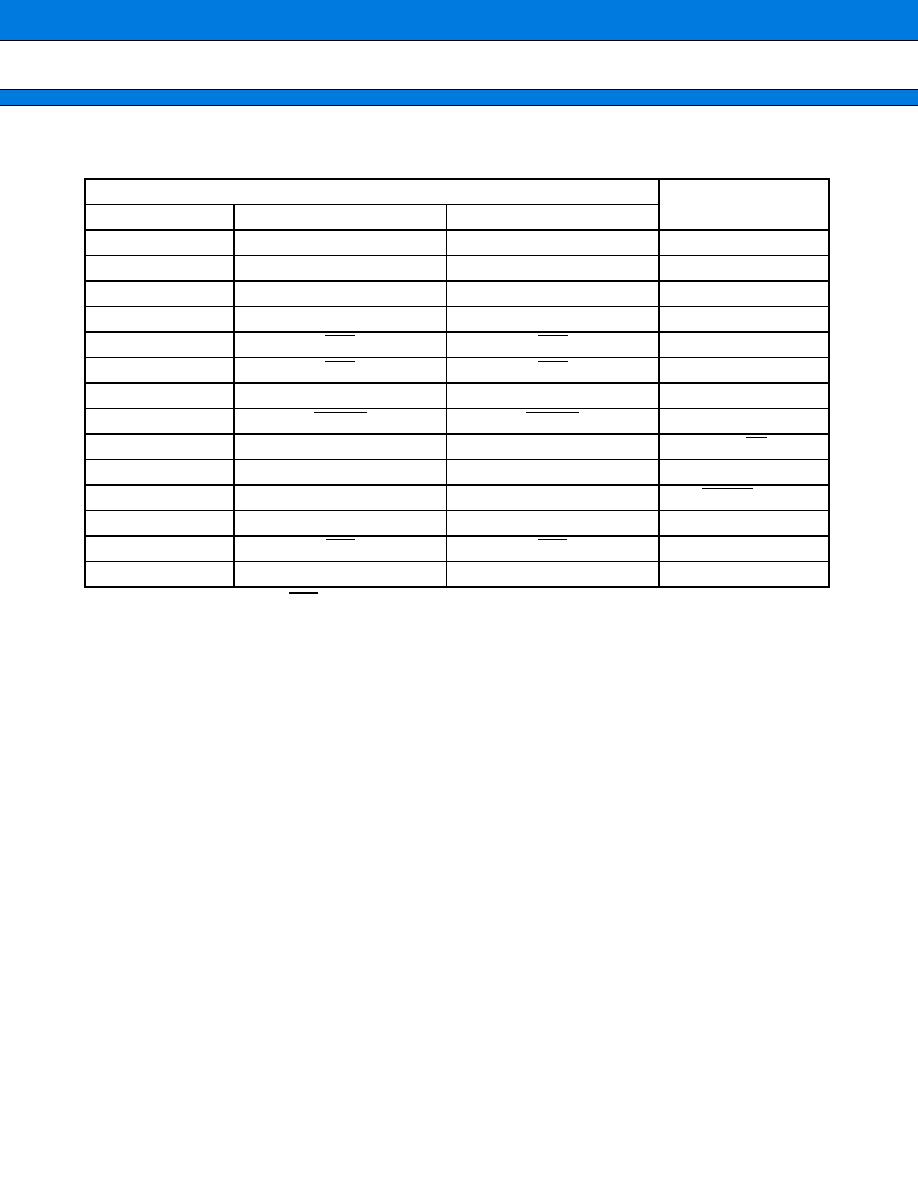

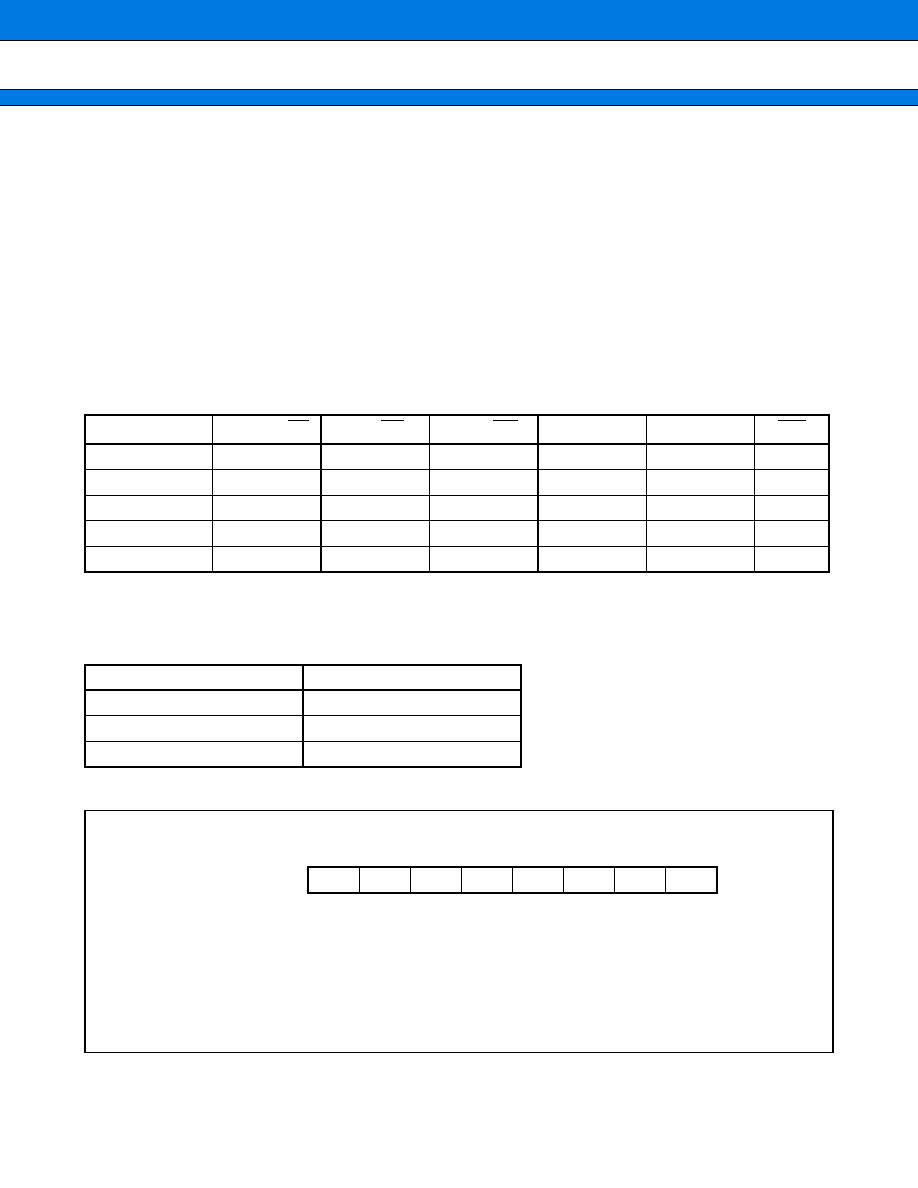

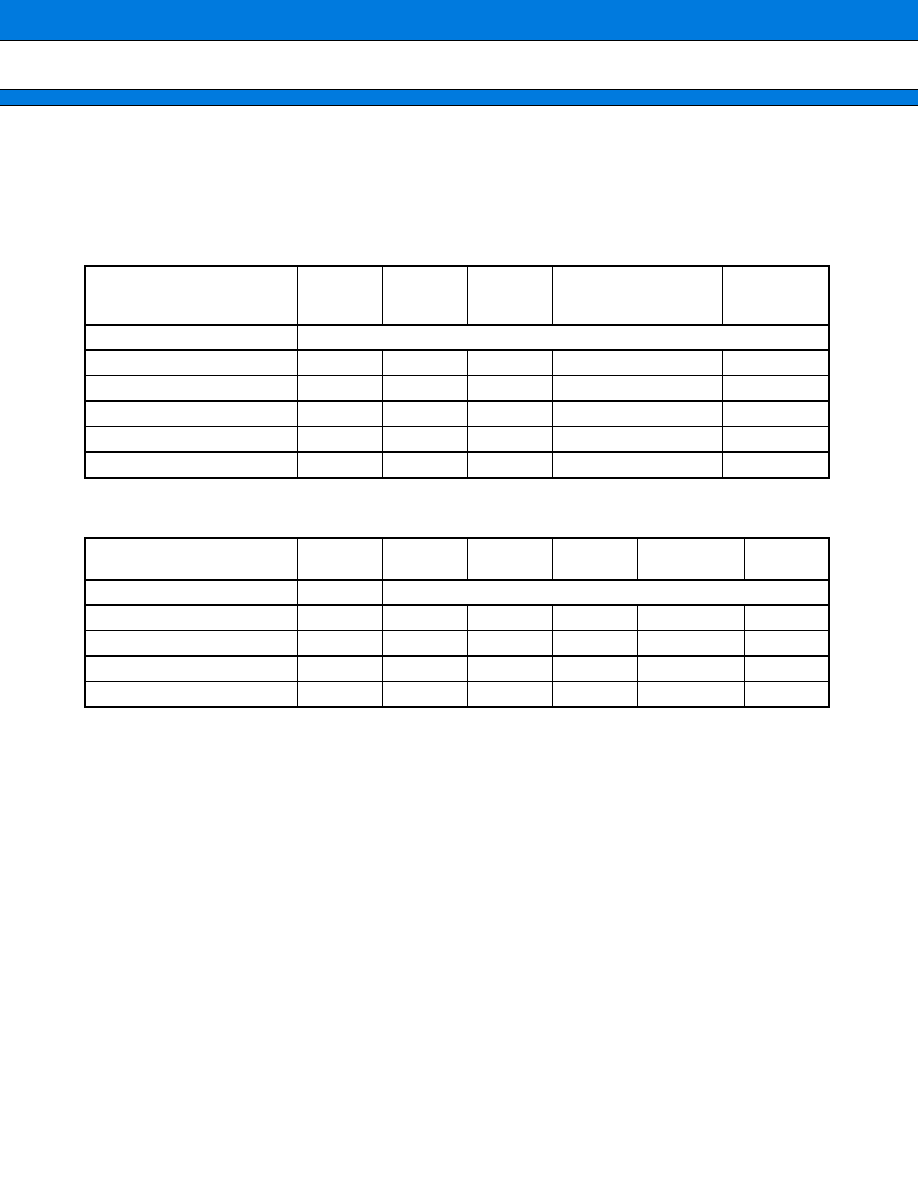

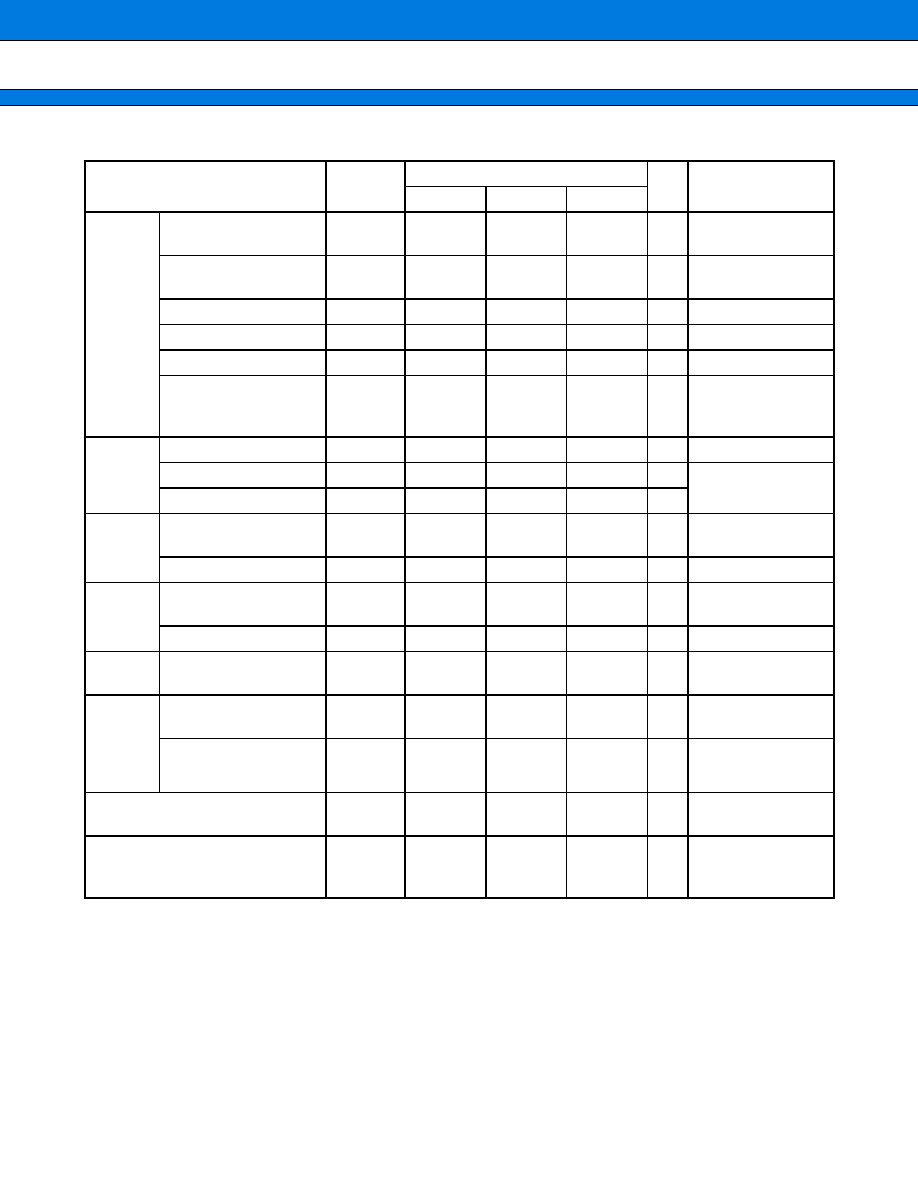

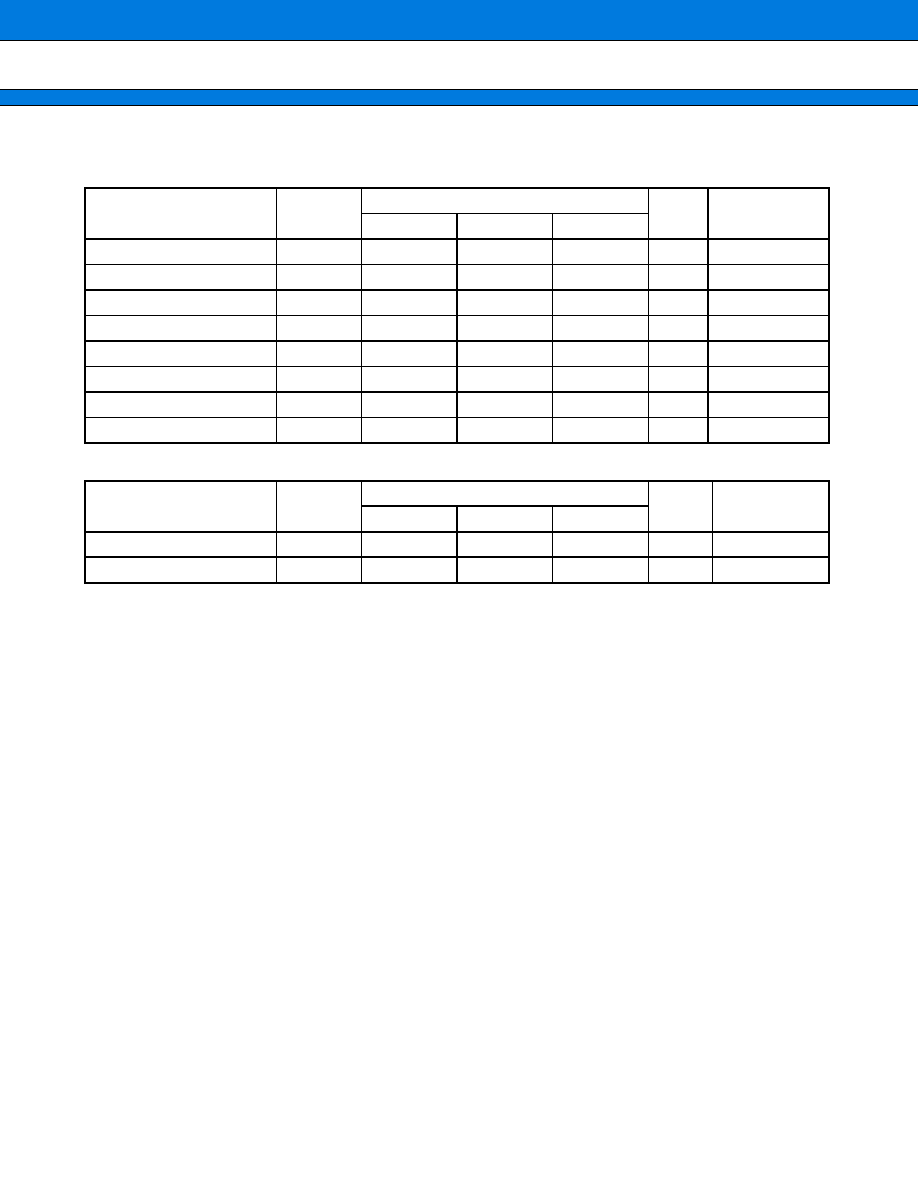

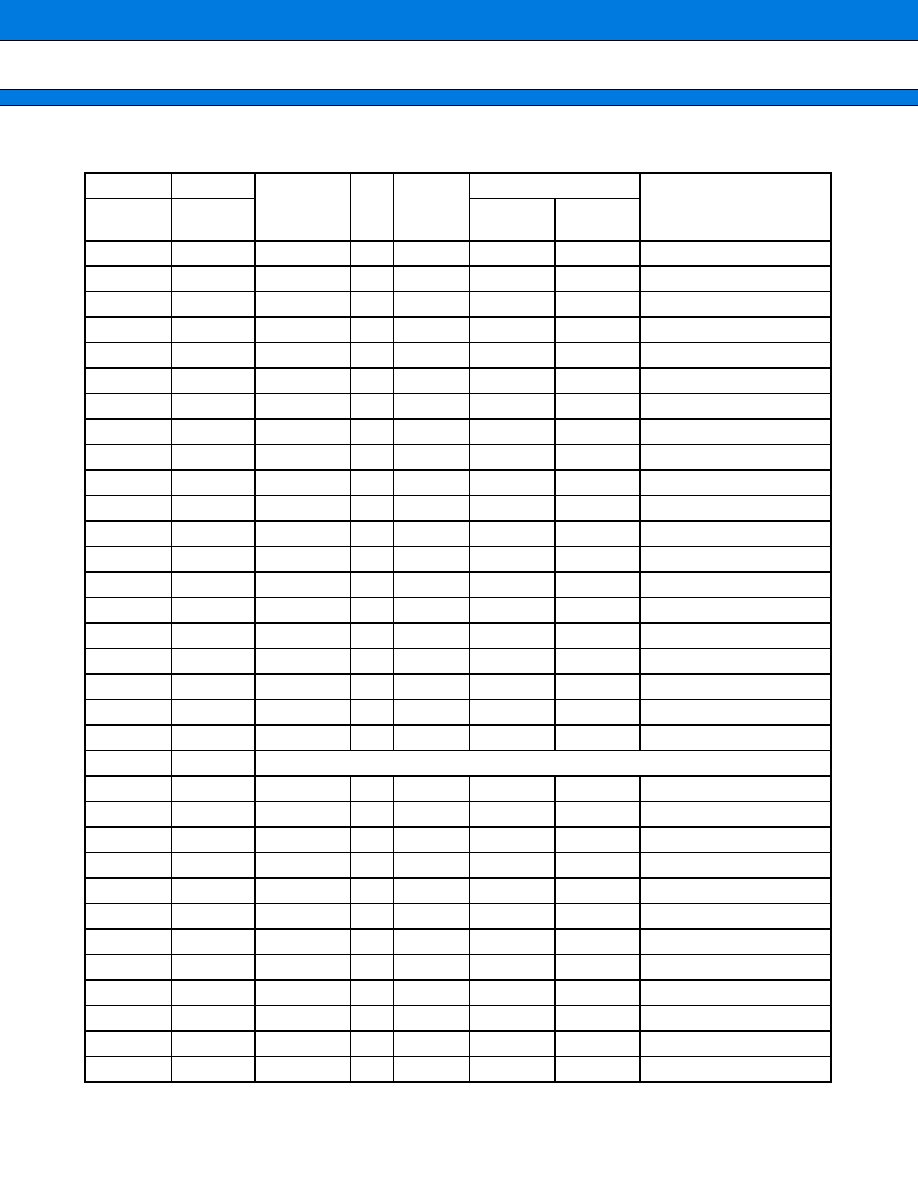

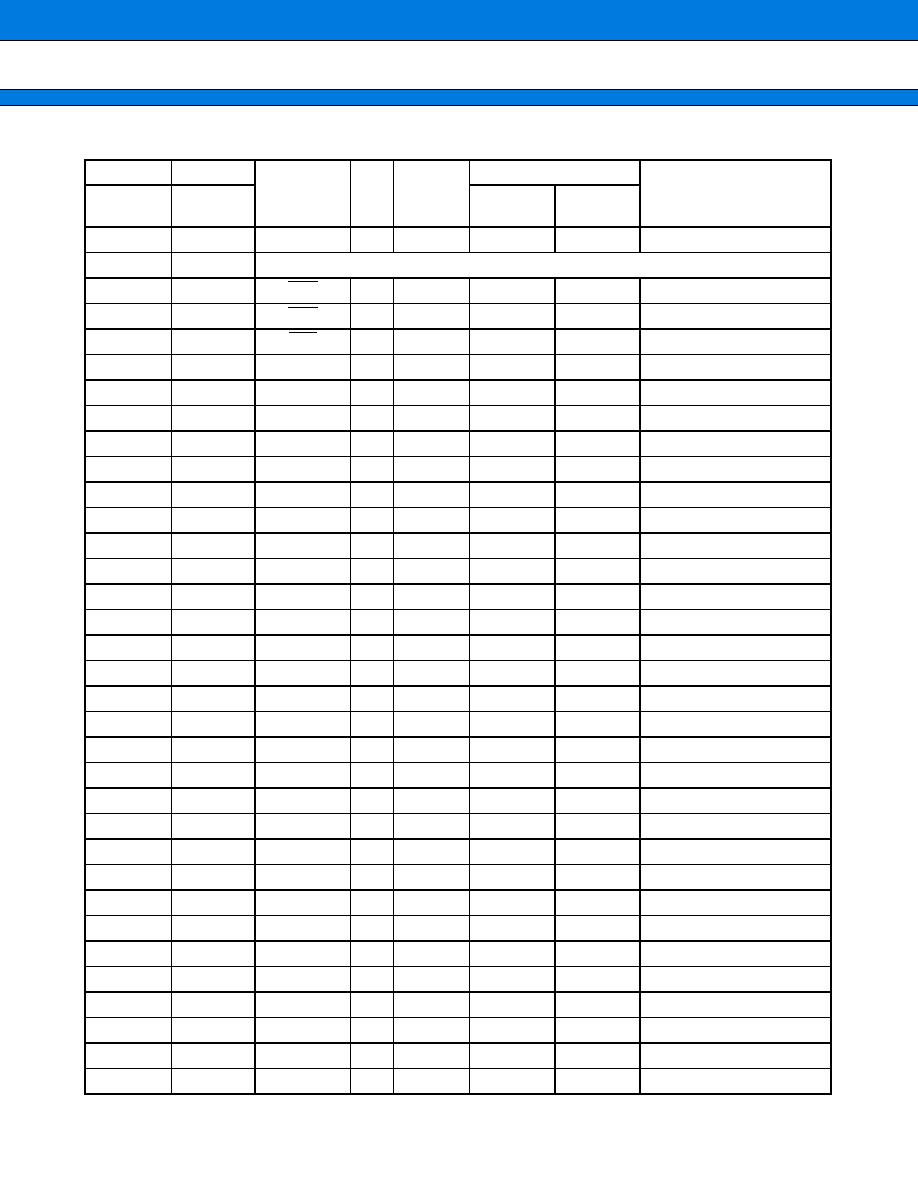

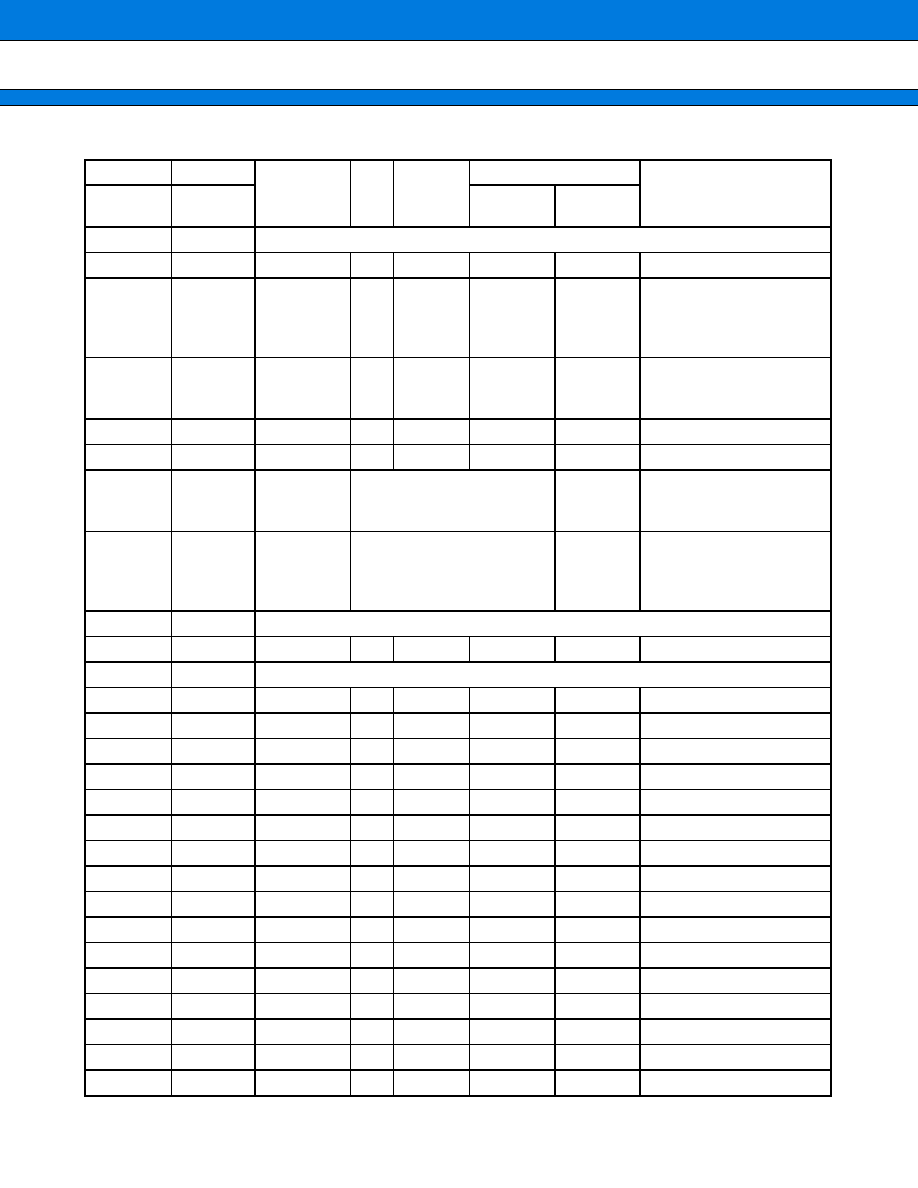

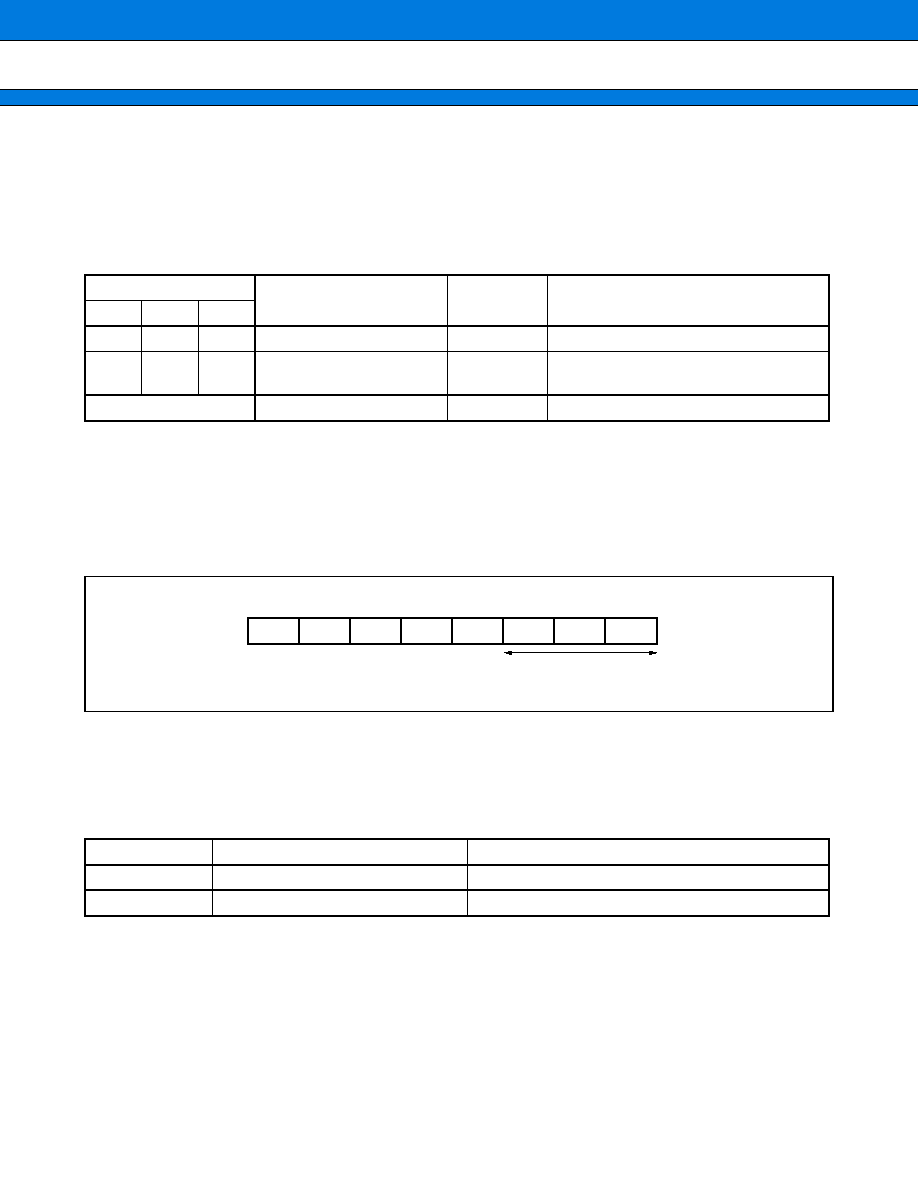

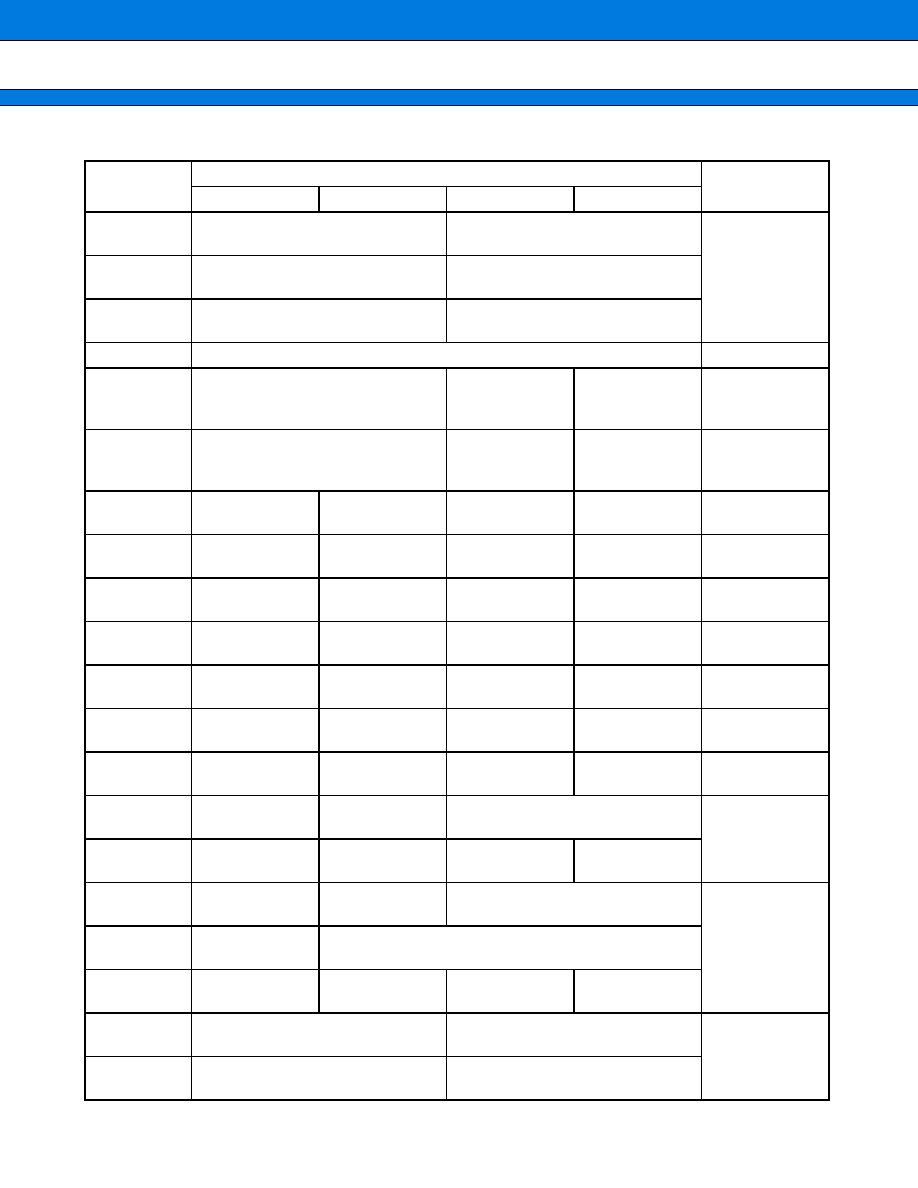

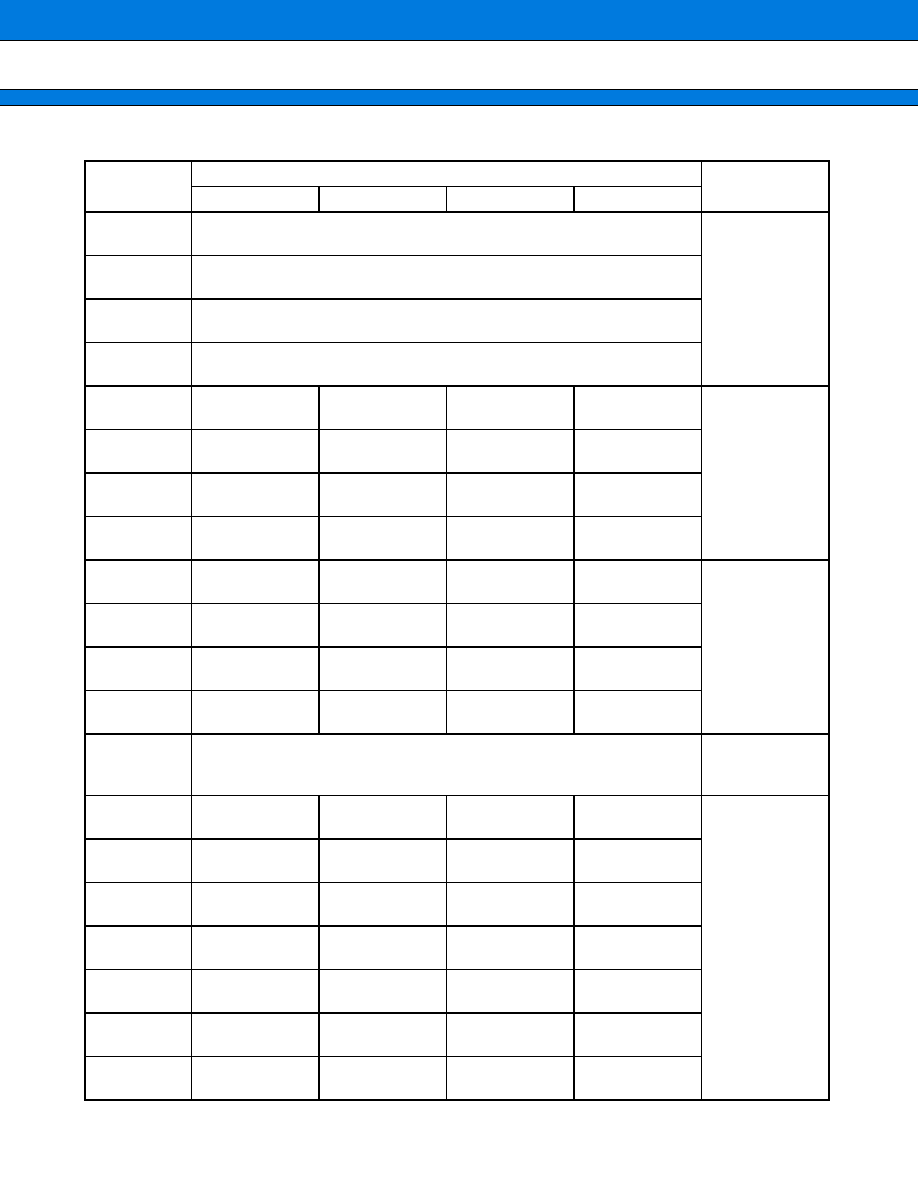

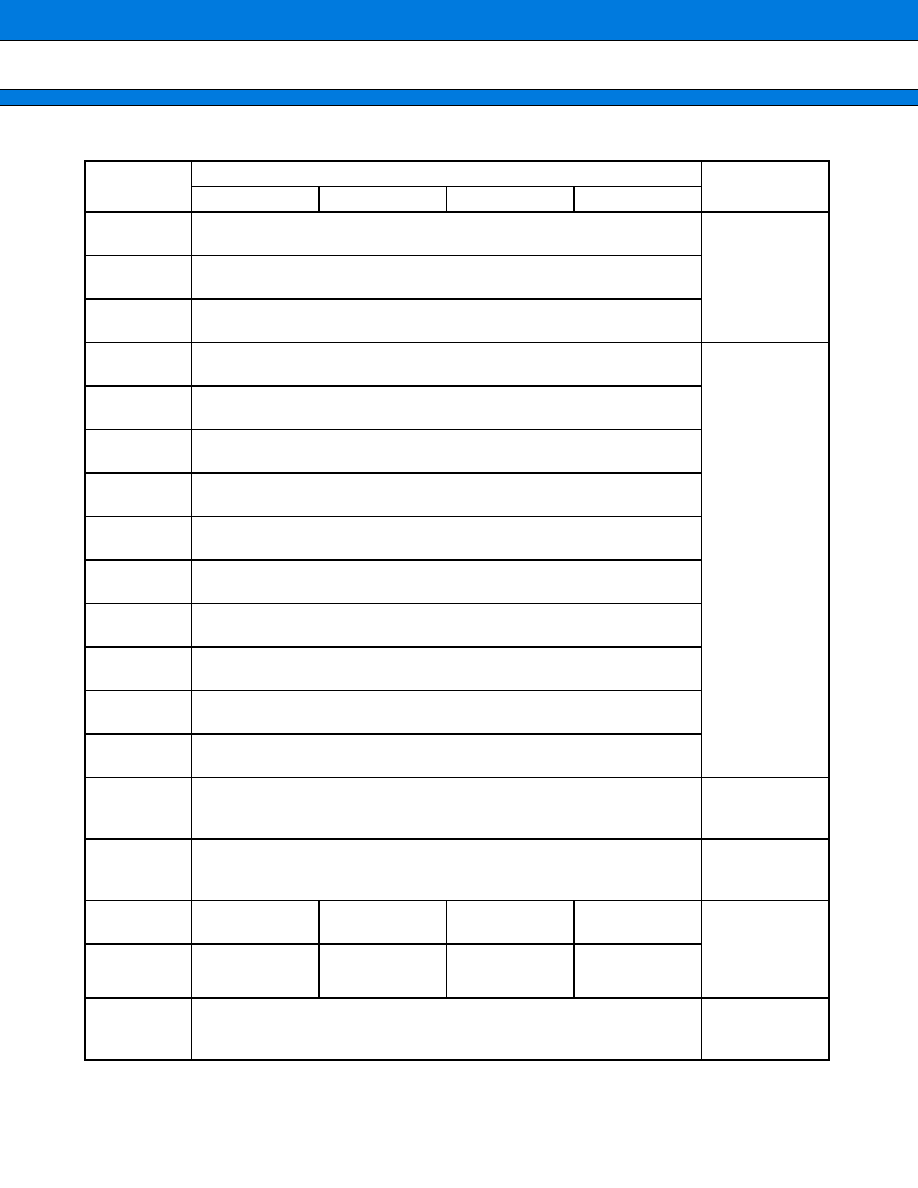

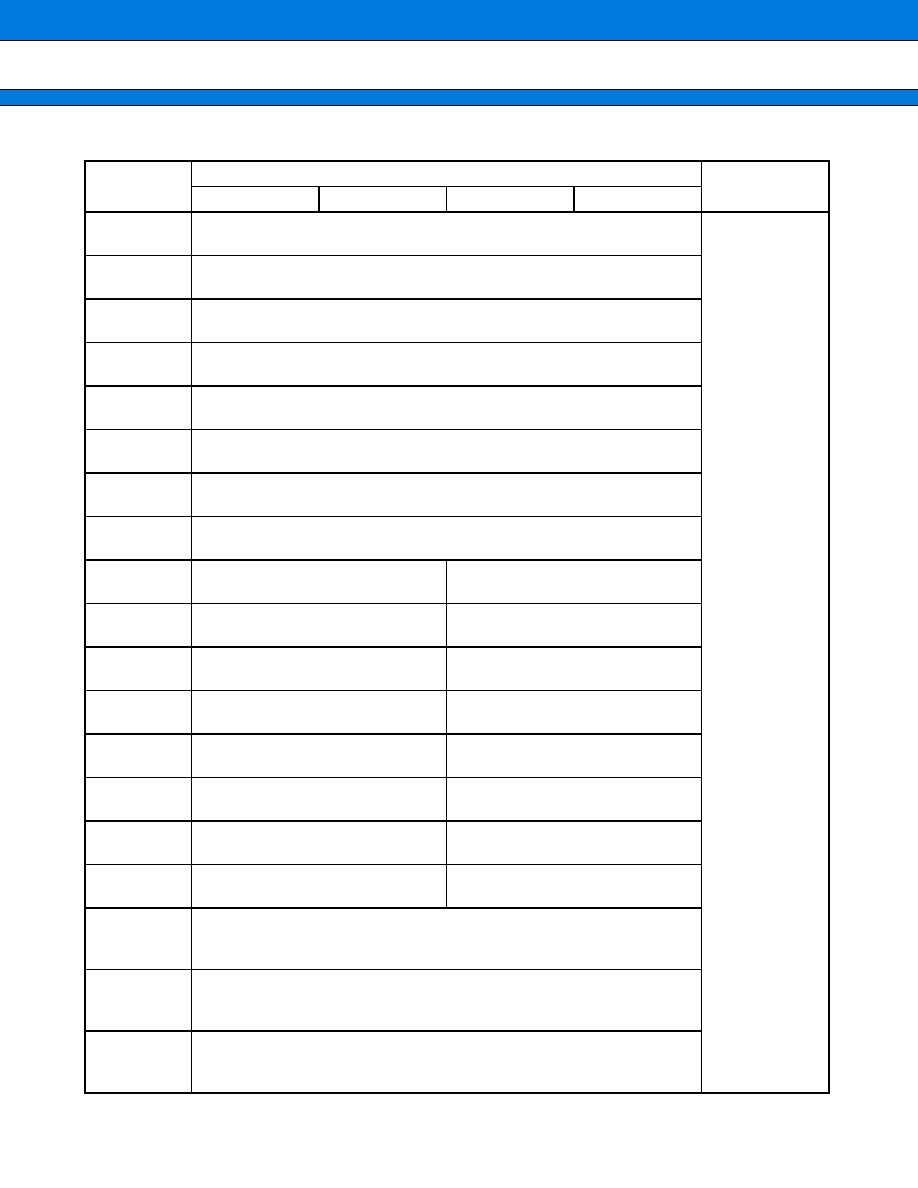

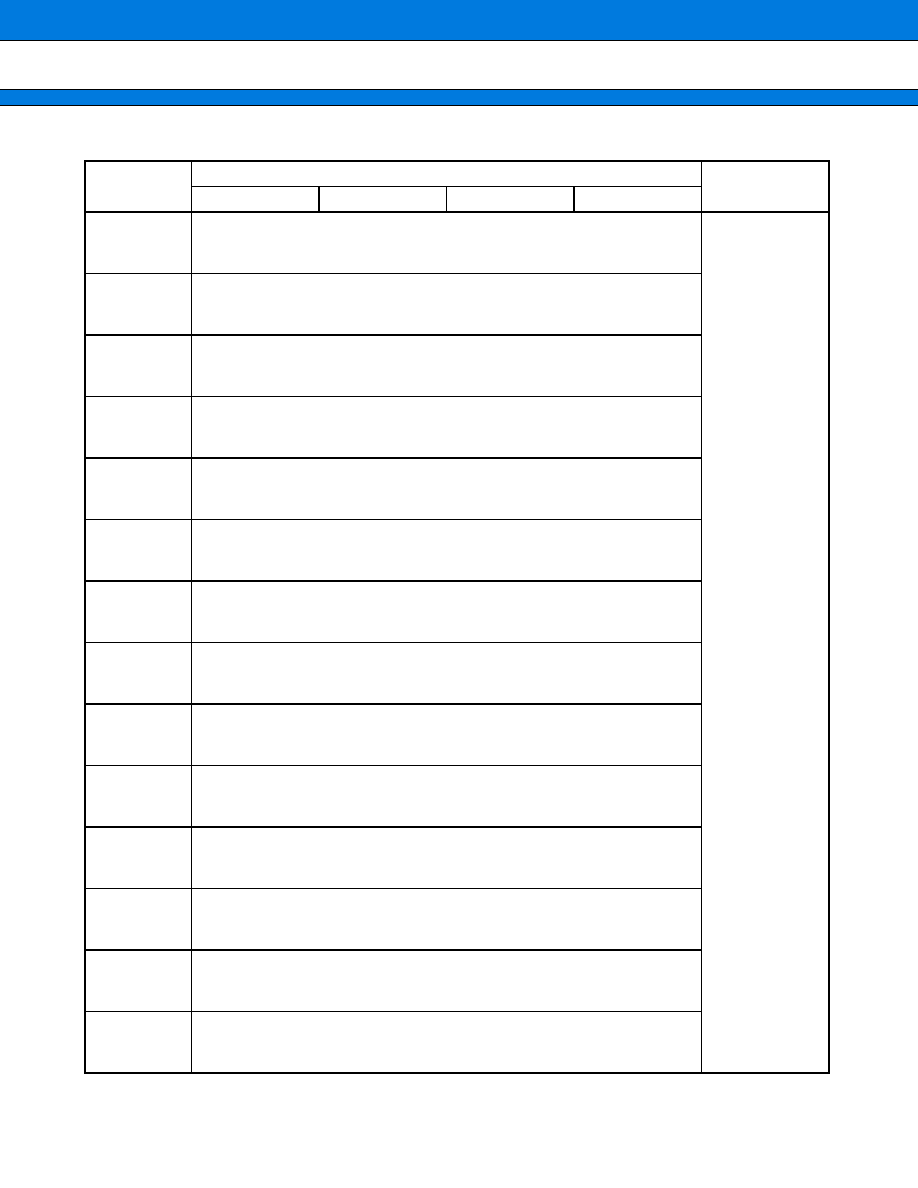

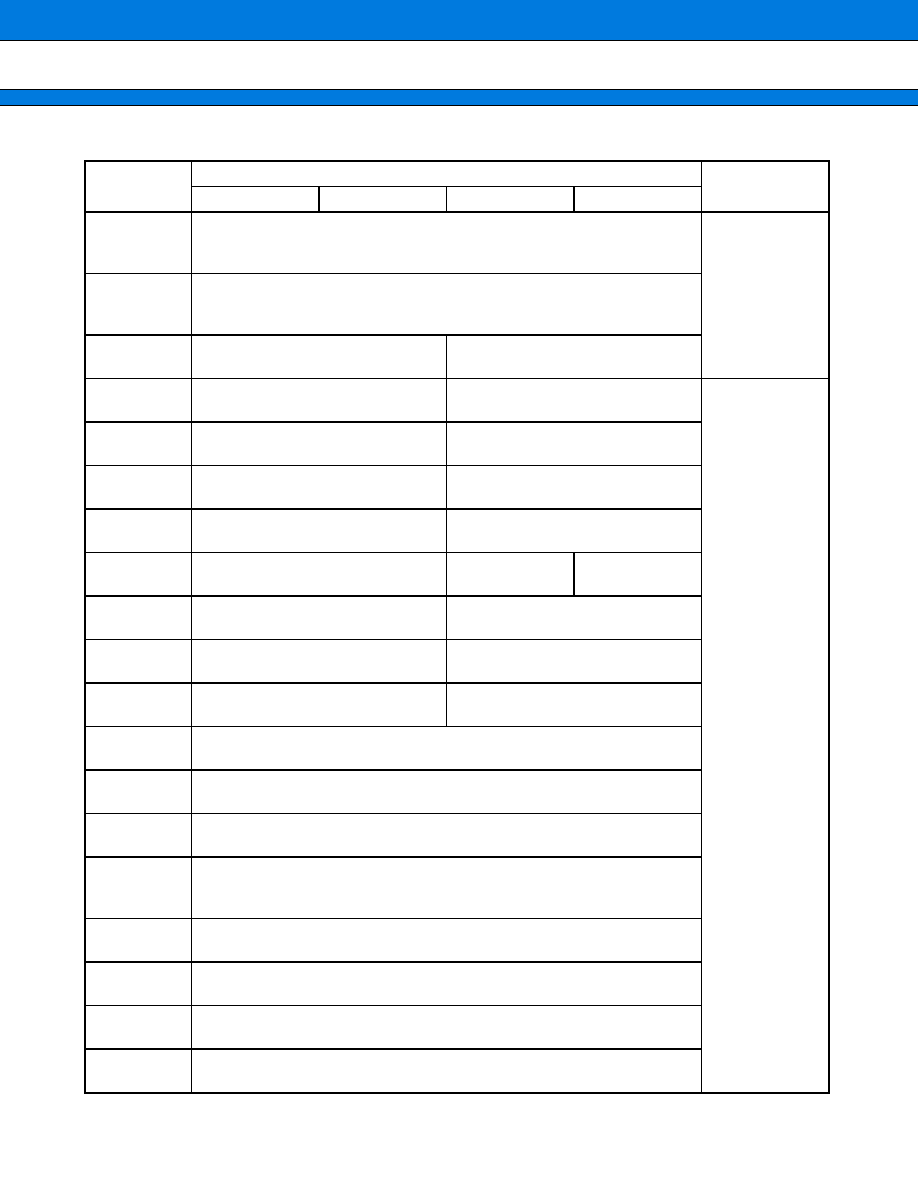

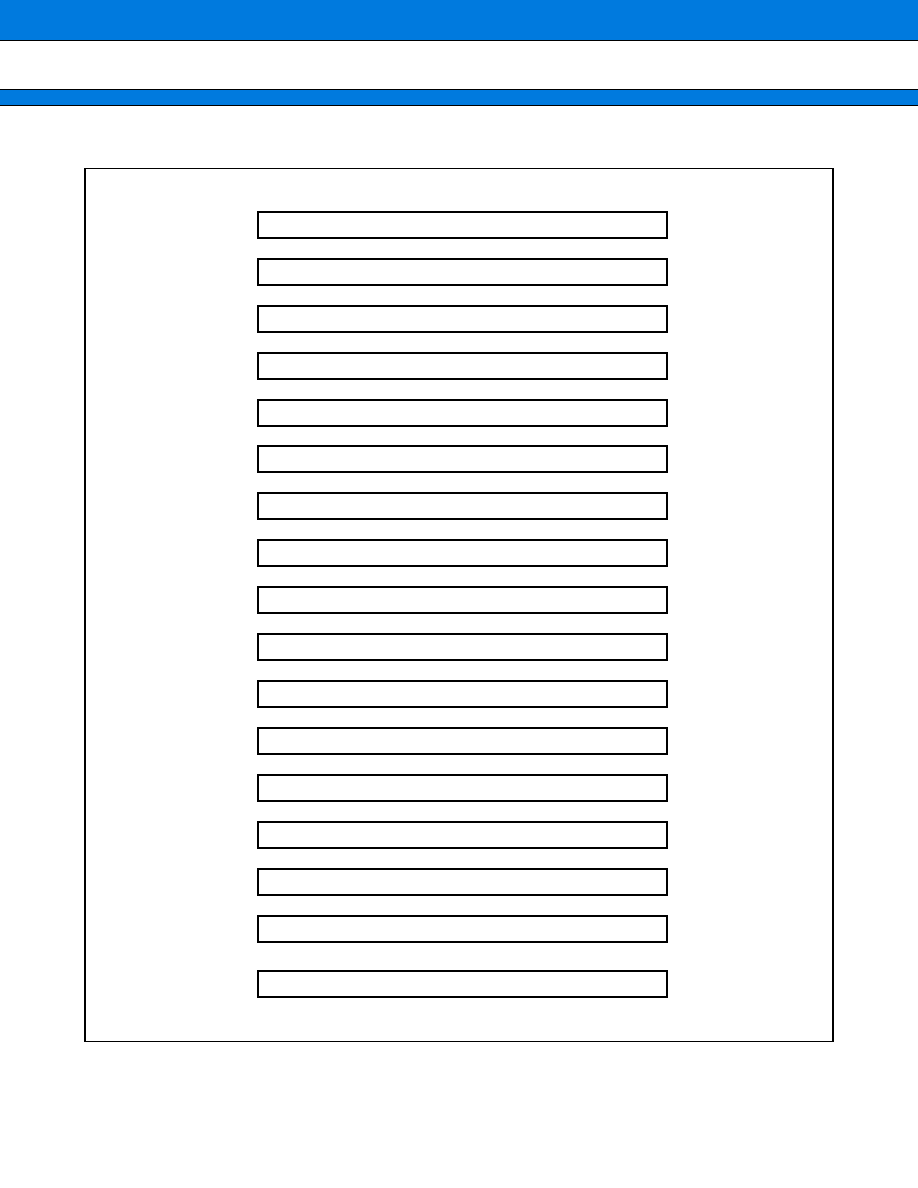

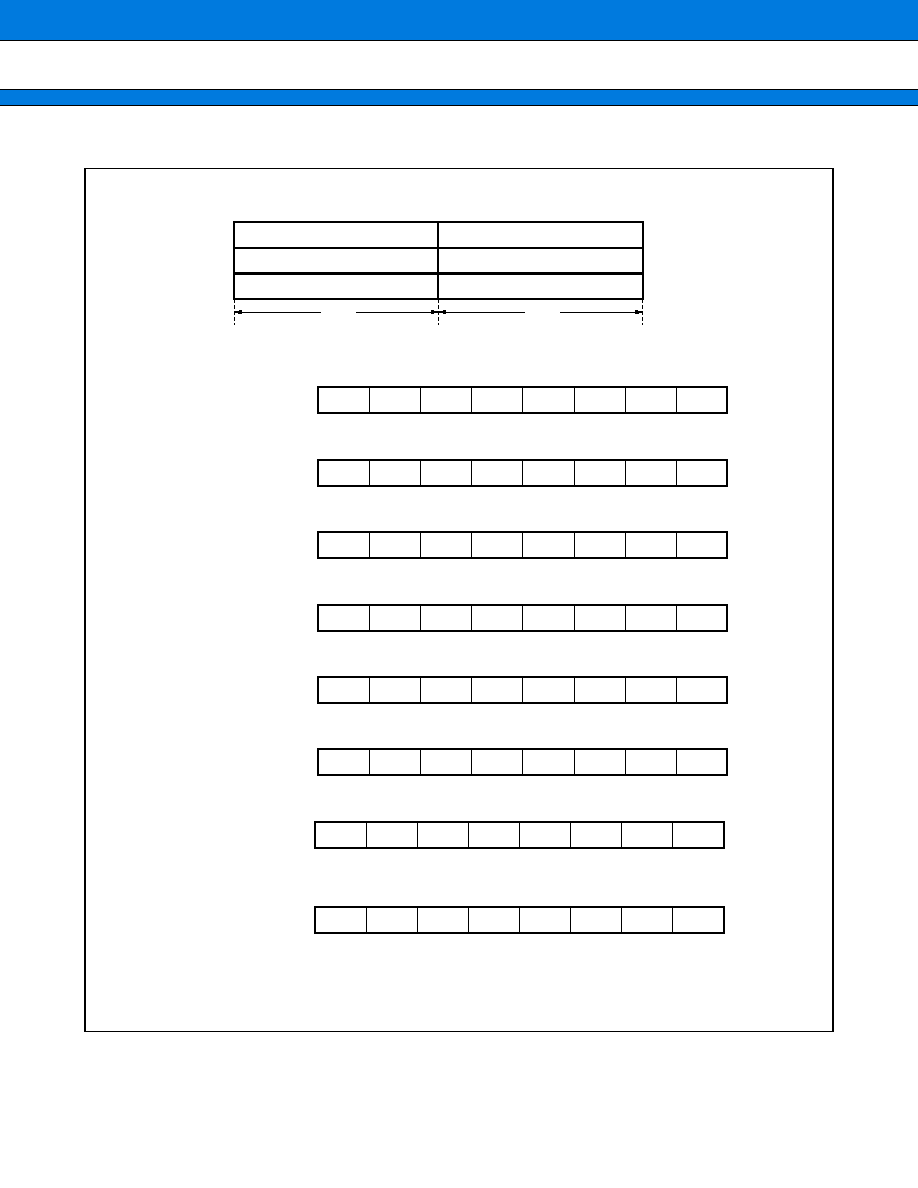

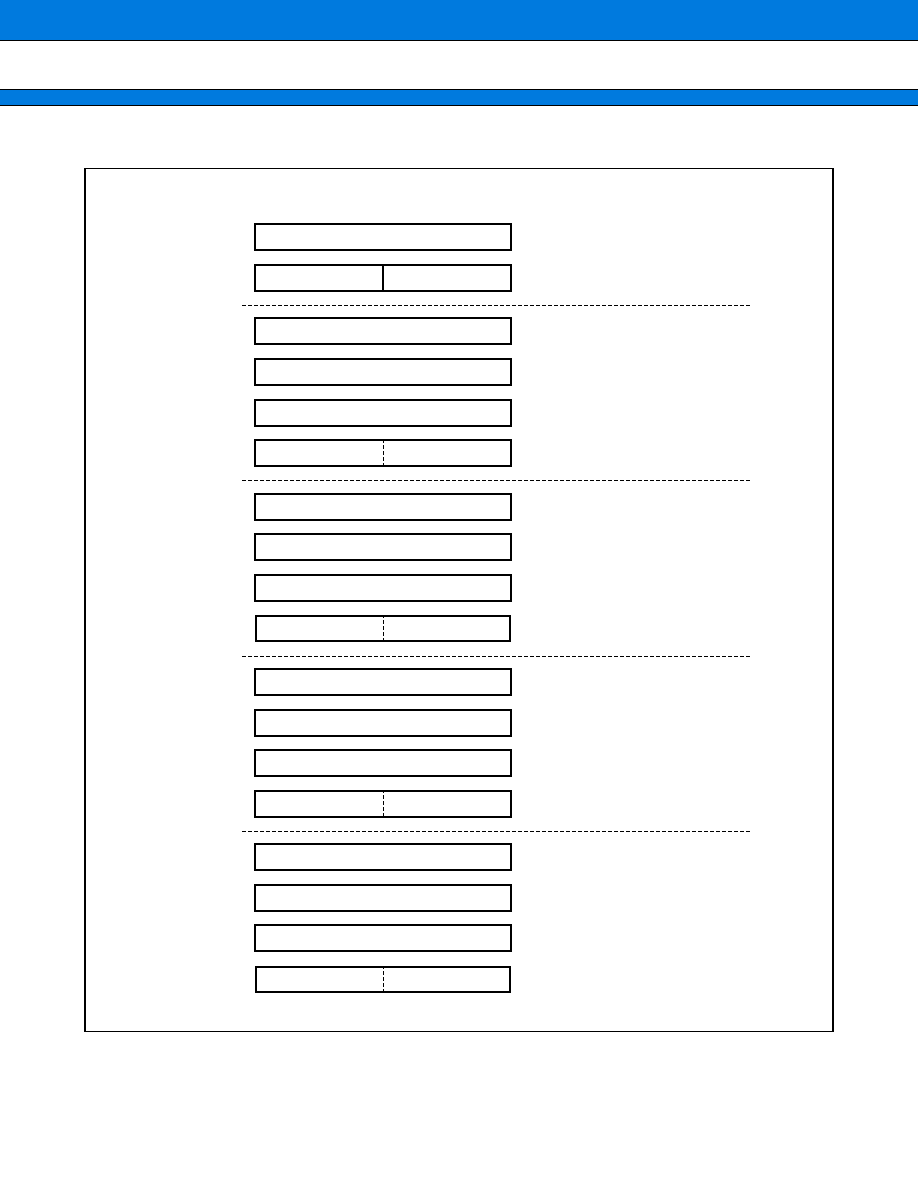

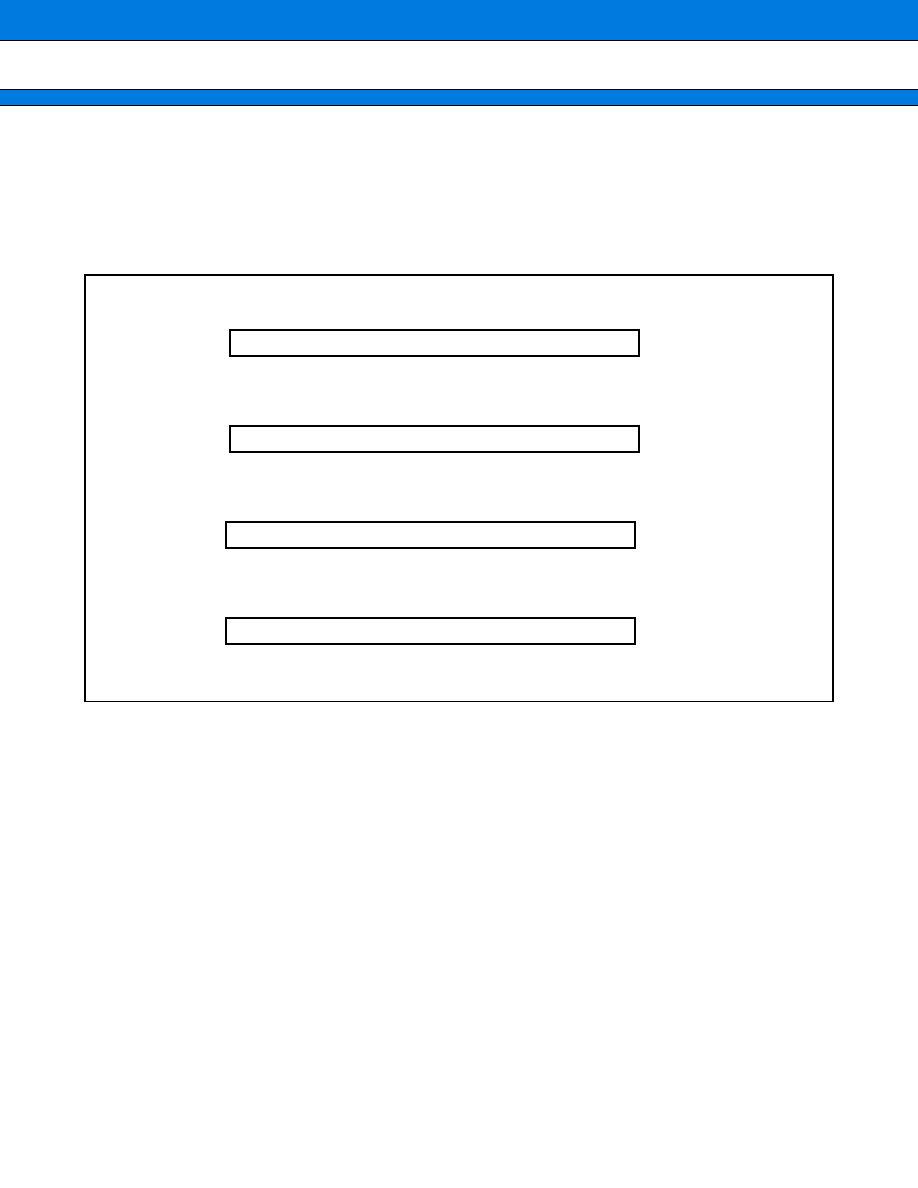

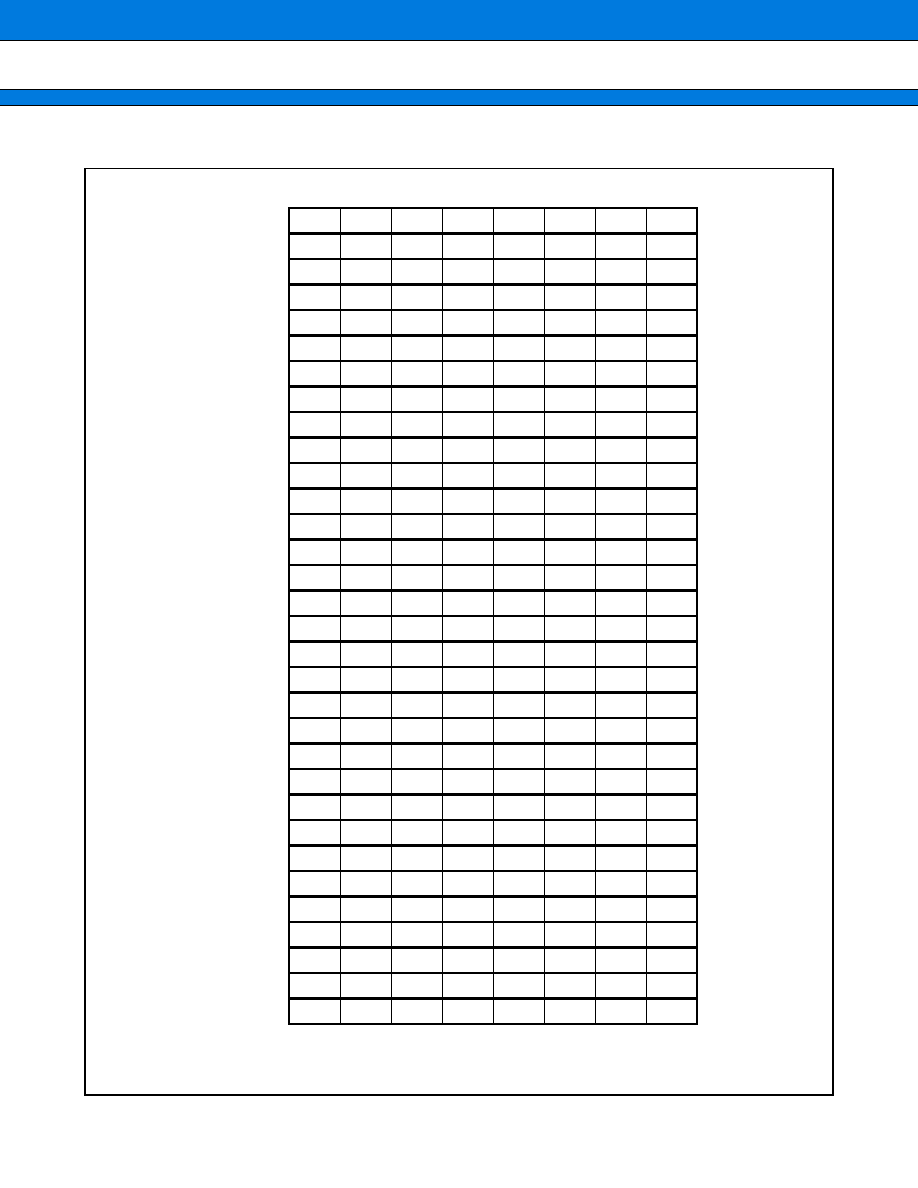

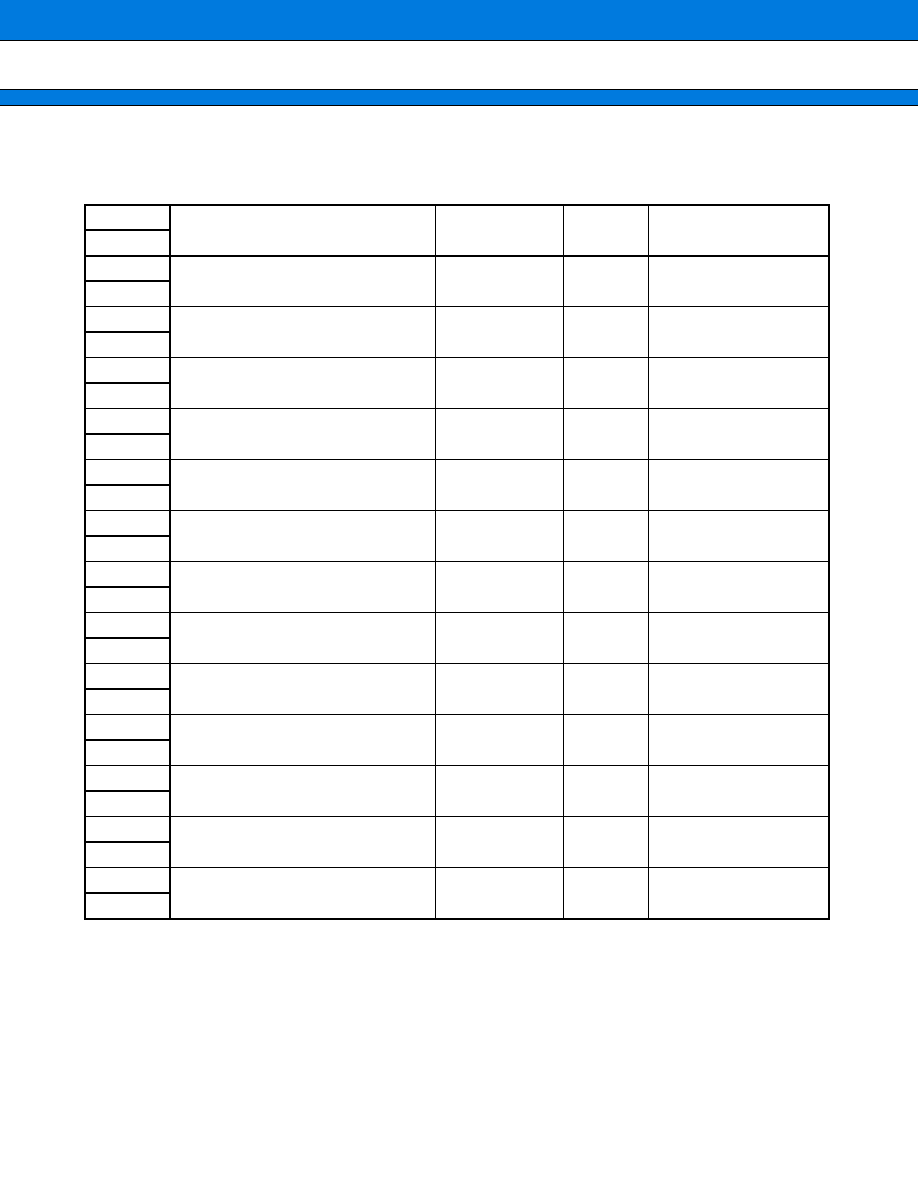

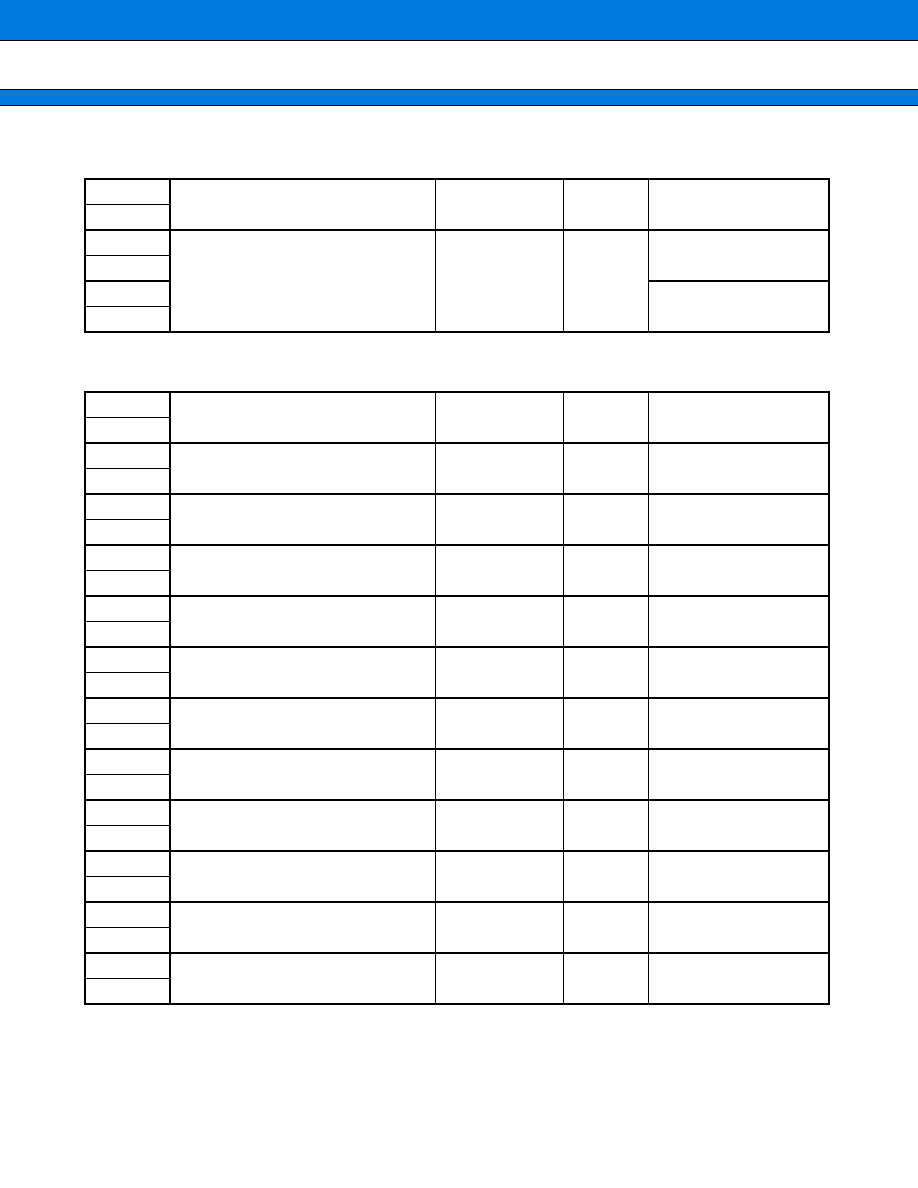

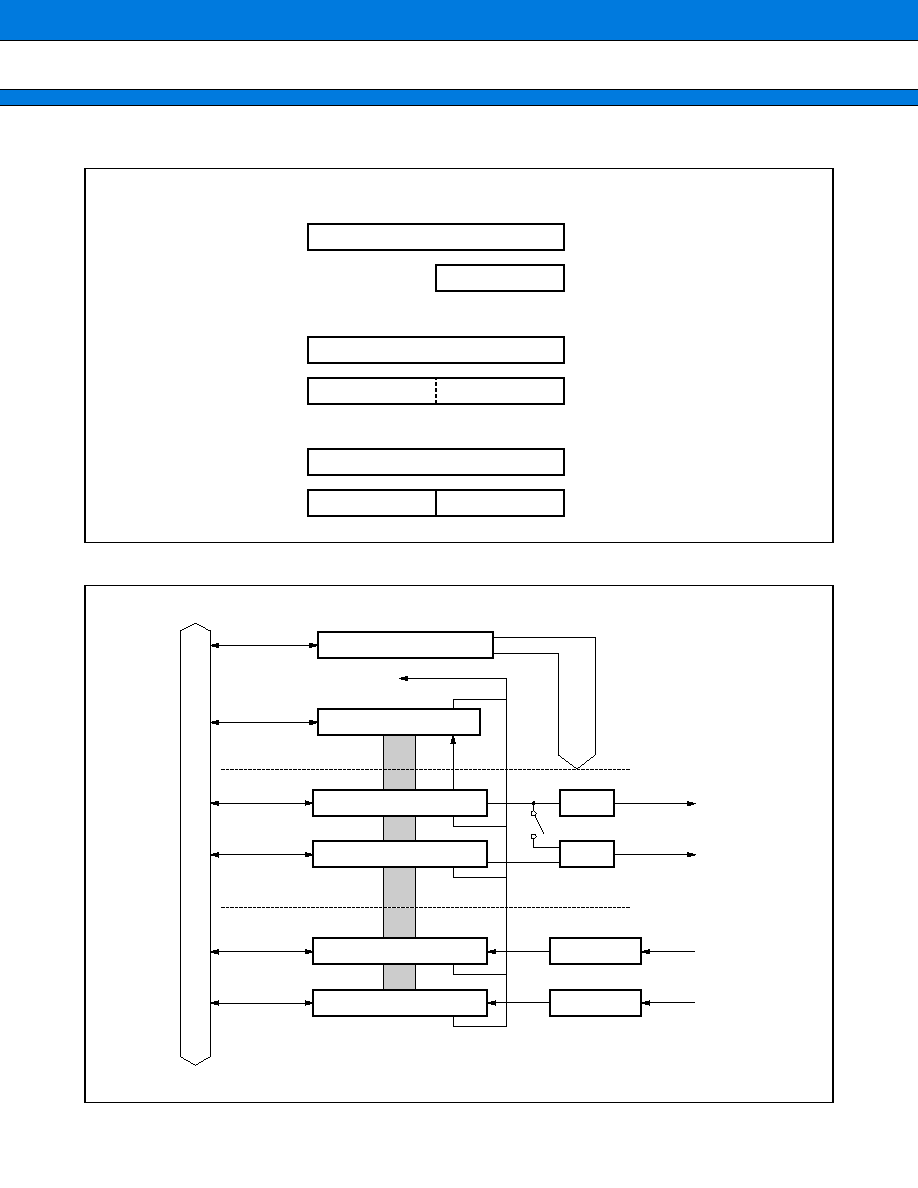

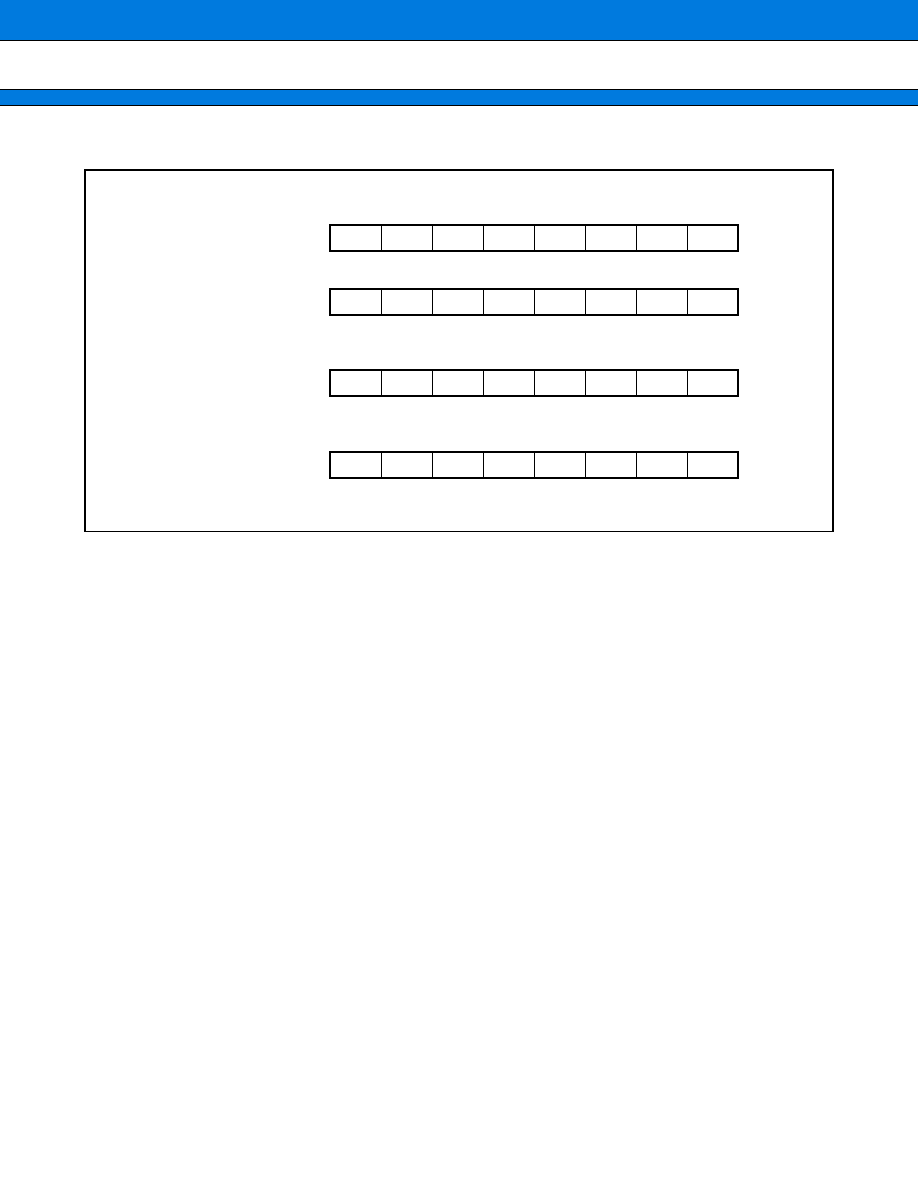

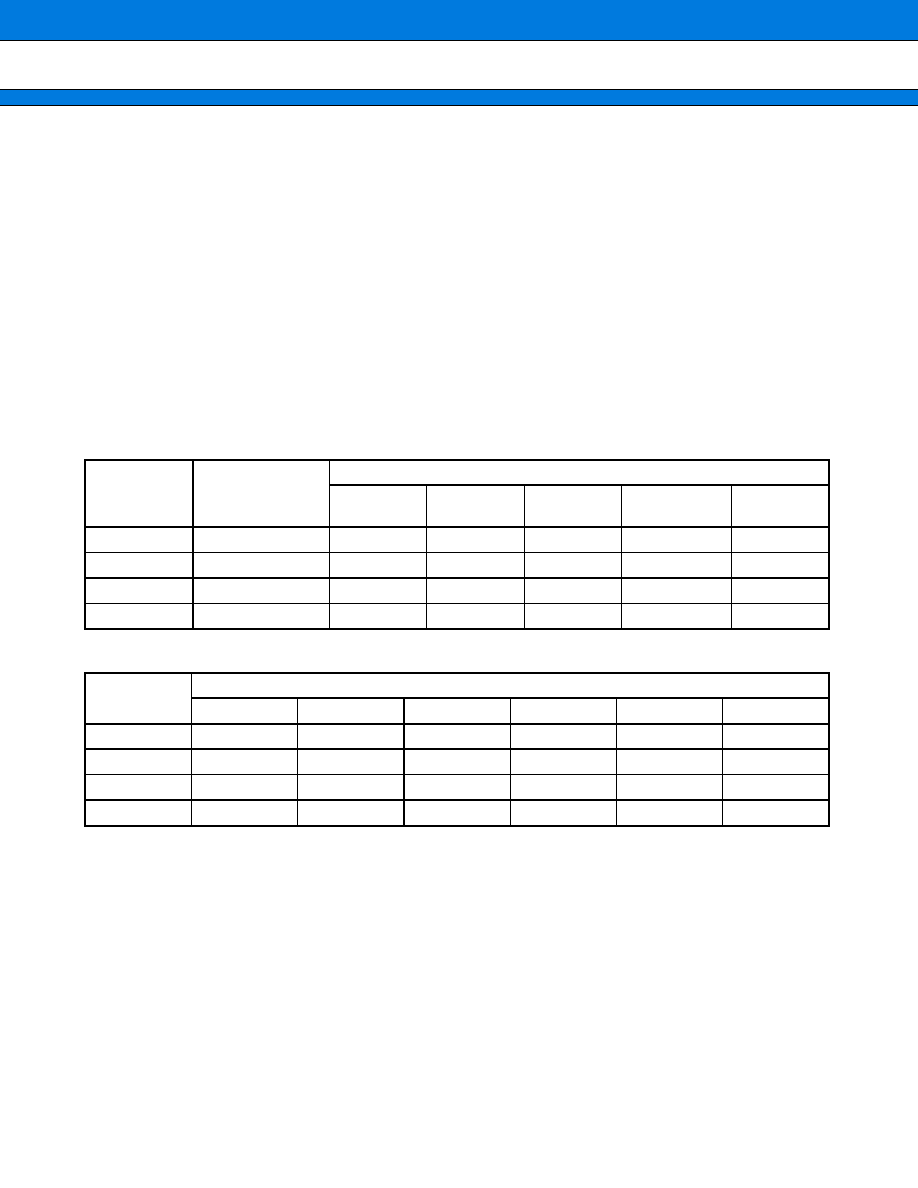

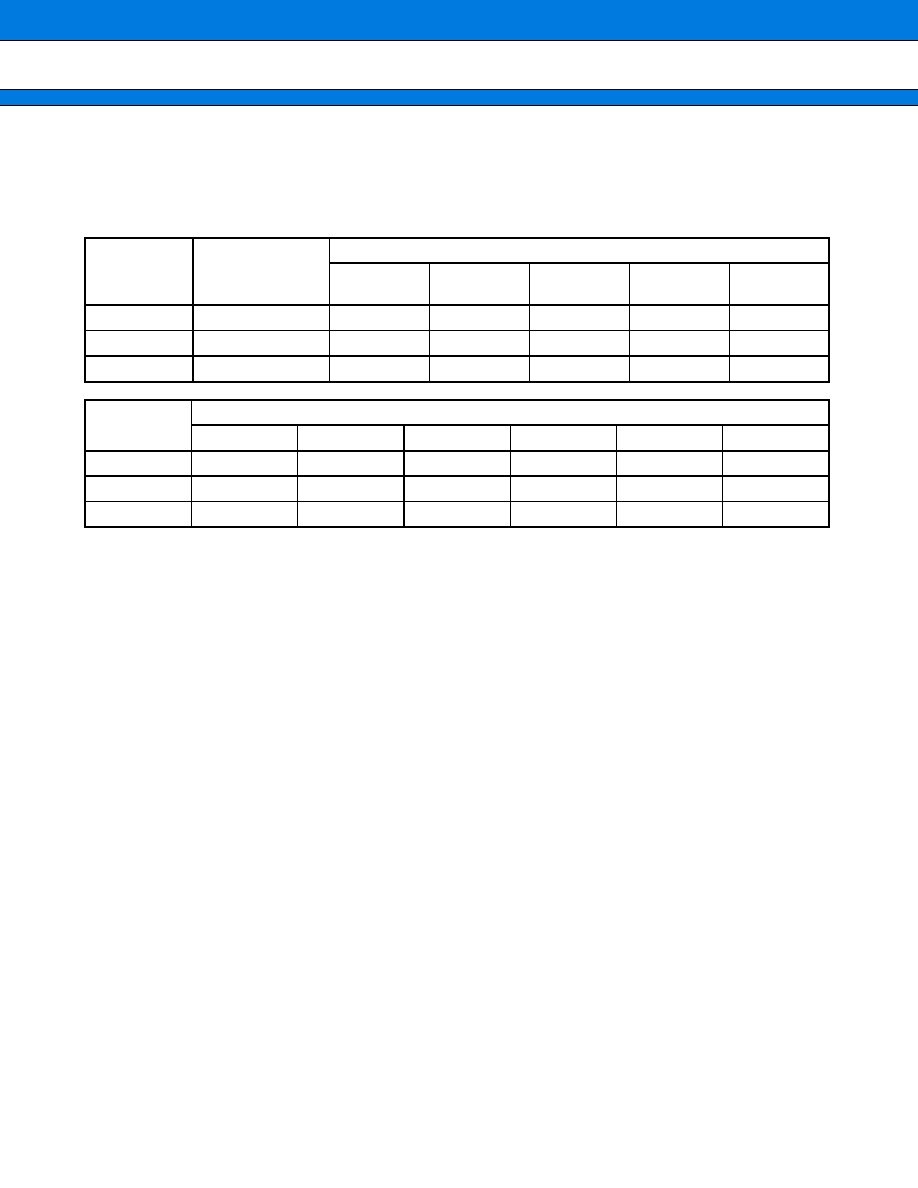

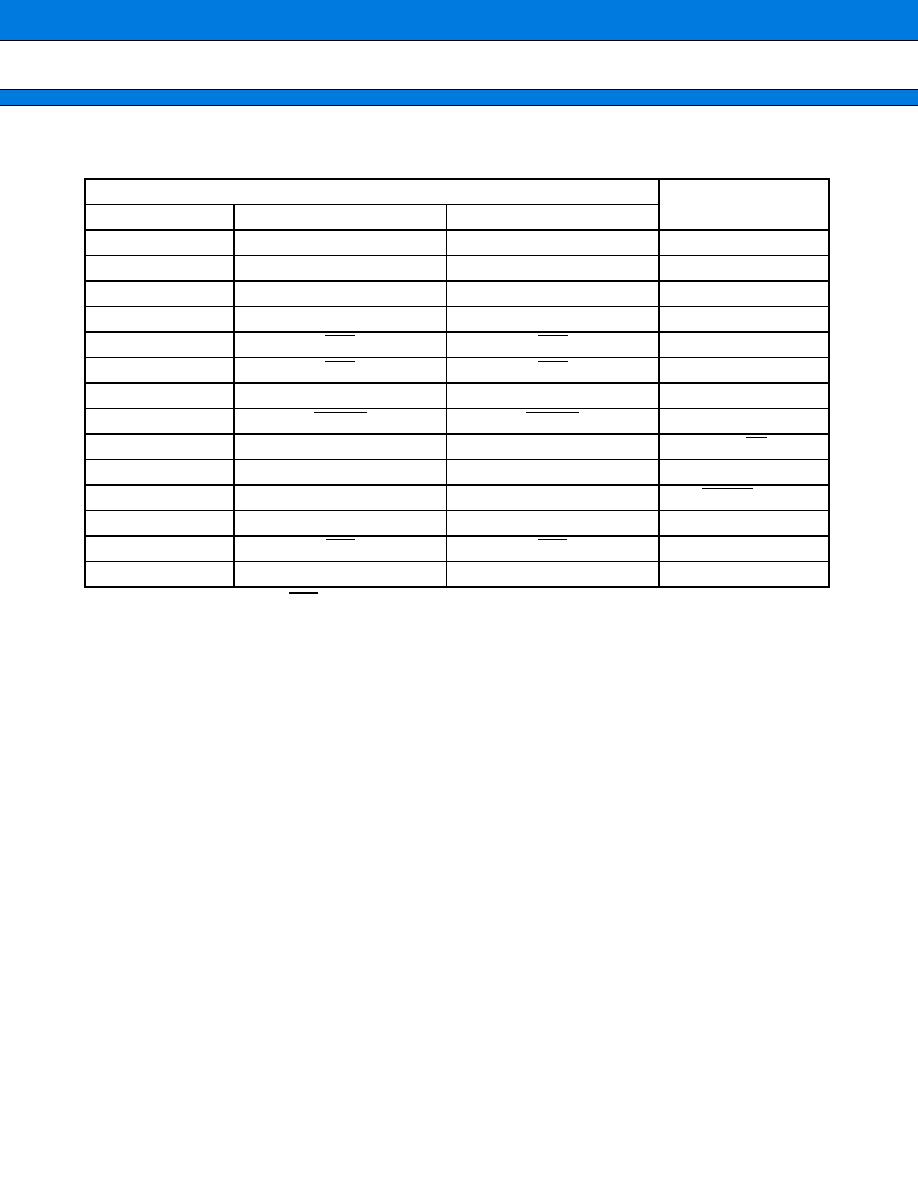

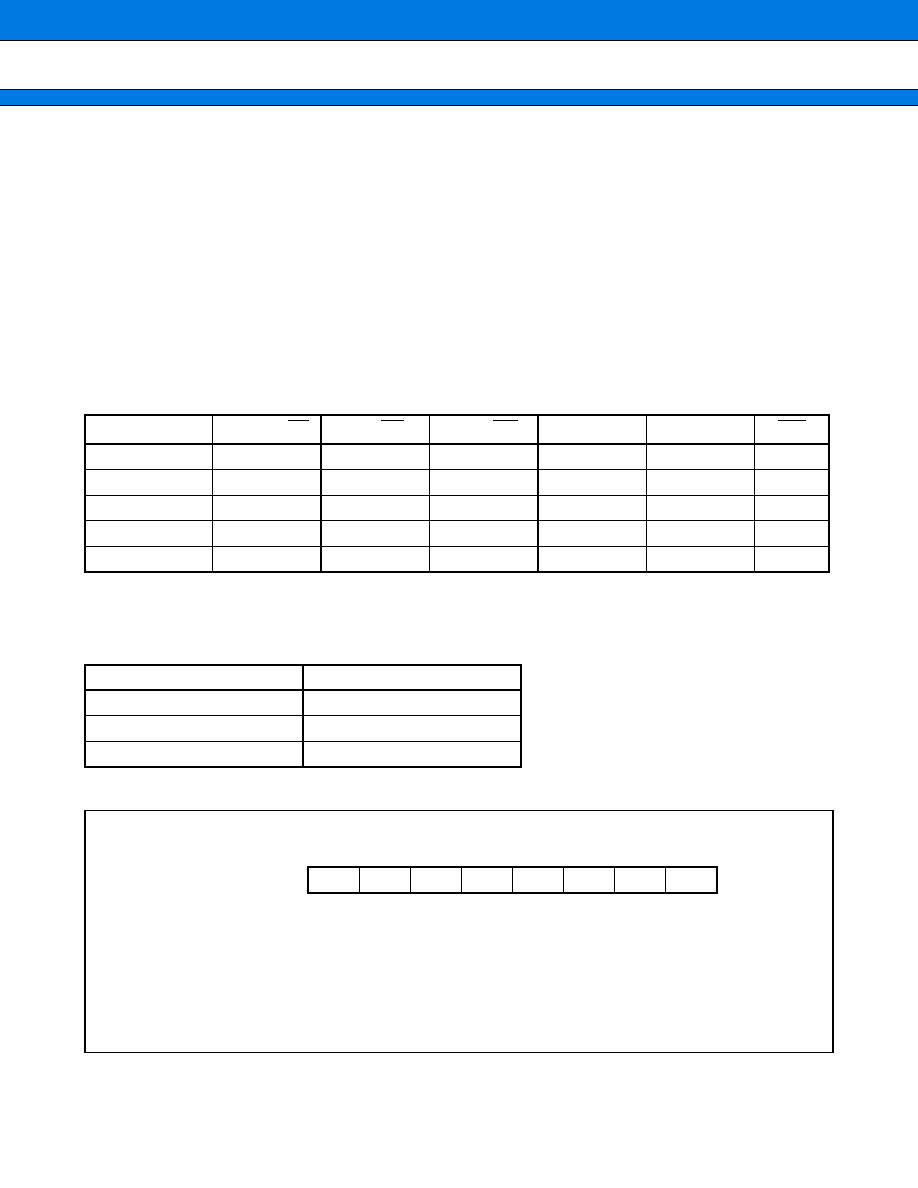

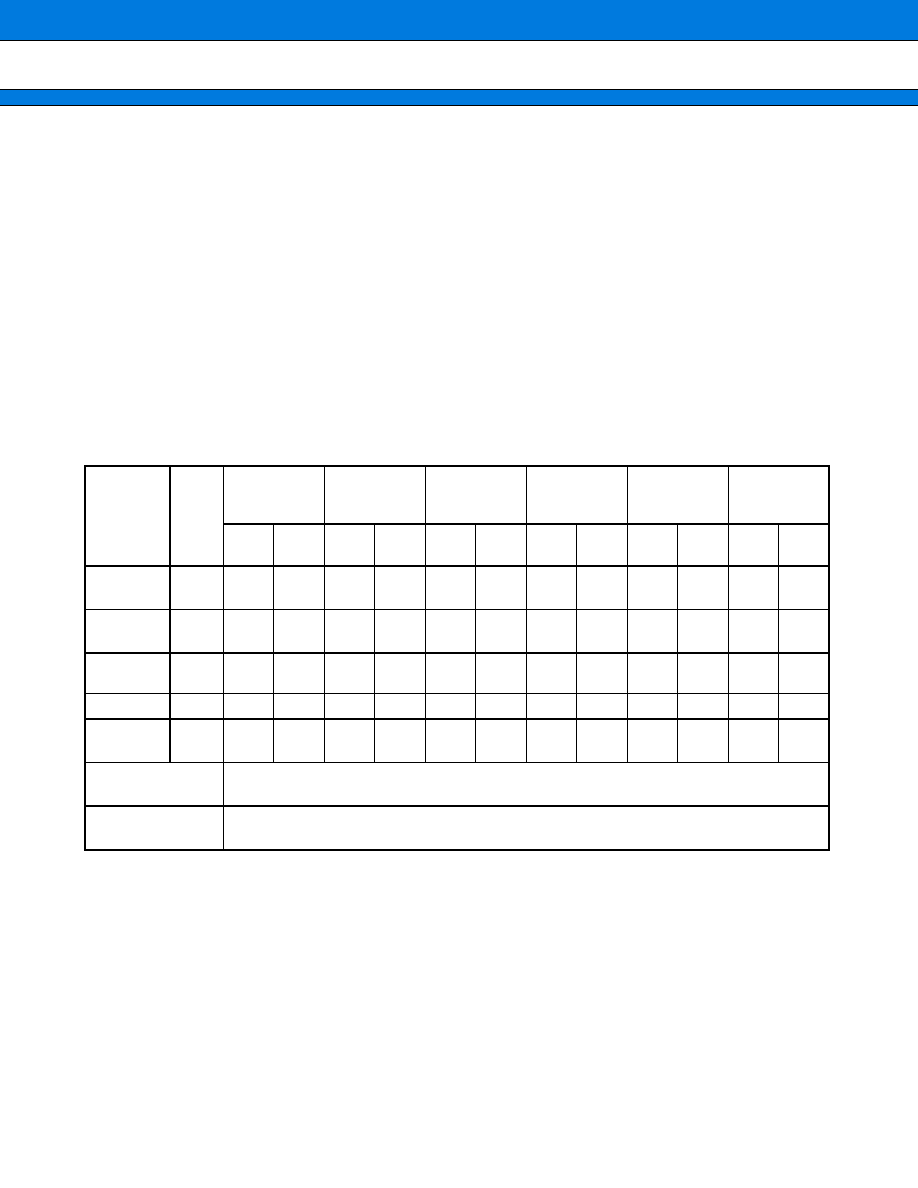

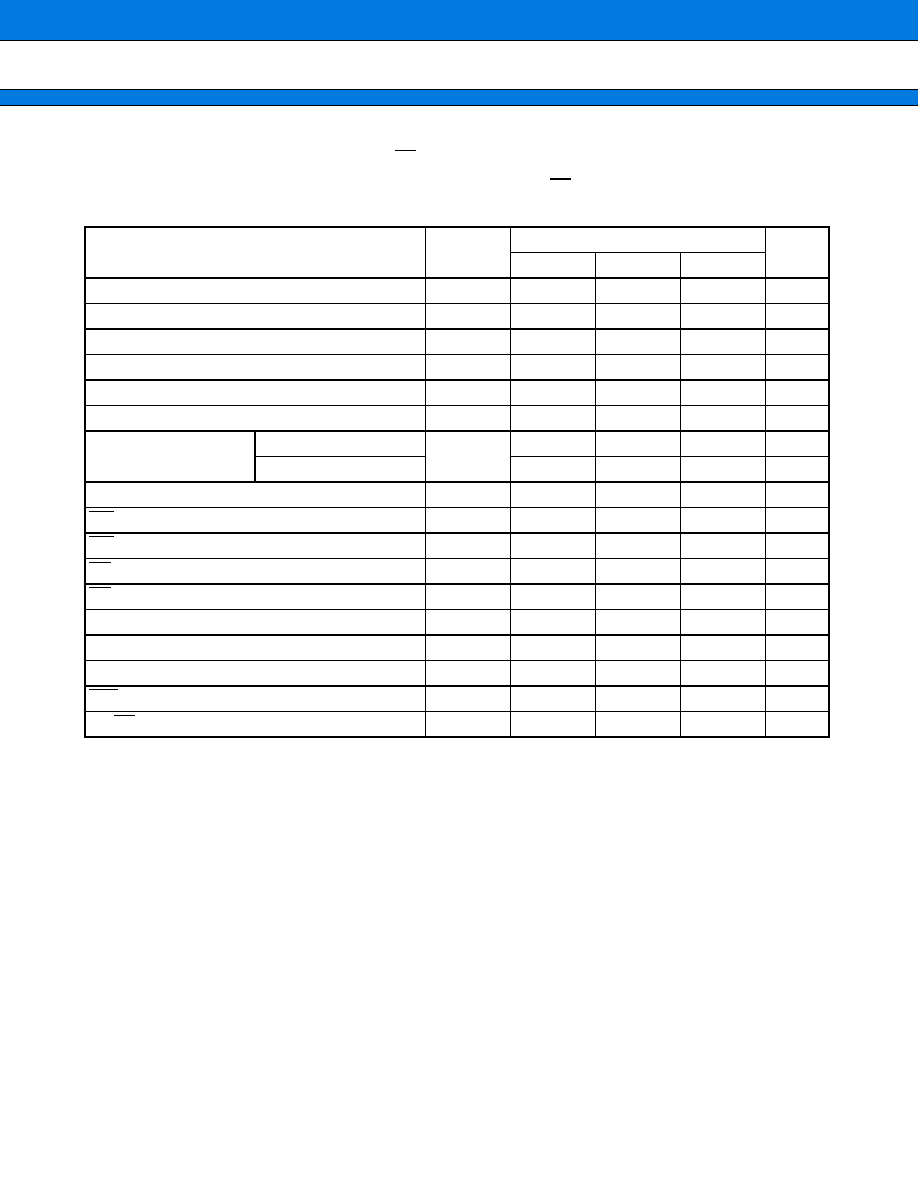

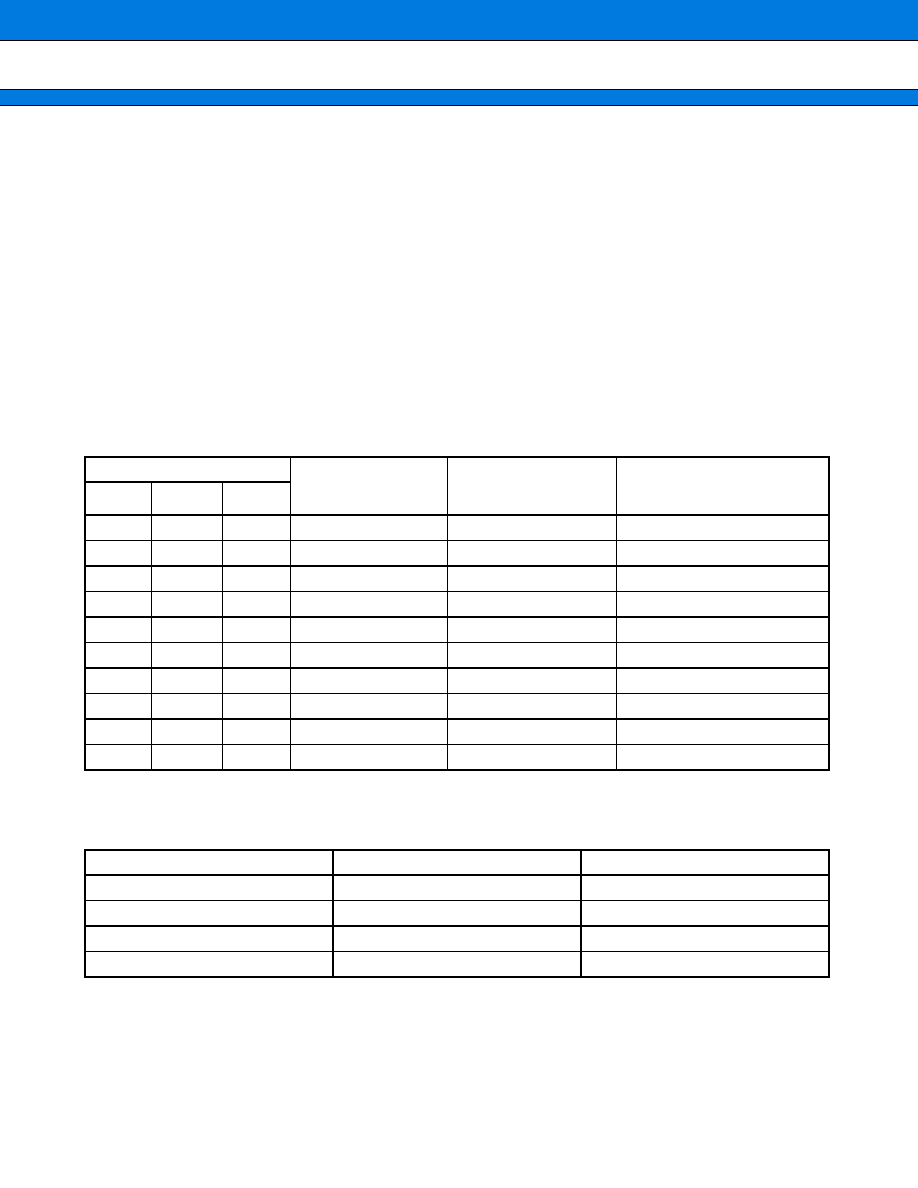

PRODUCT LINEUP

Resource Channels

Memory Size

MB91FV360GA

MB91F361GA

MB91F362GA

Cache/Instruction RAM

4 KB / 4 KB

1 KB / 1 KB

- / 4 KB

D-bus RAM

16 KB

12 KB

12 KB

F-bus RAM

16 KB

4 KB

4 KB

Flash/ROM

512 KB on F-bus

512 KB on ext. bus

512 KB on F-bus

Boot ROM

2 KB

2 KB

2 KB

CAN

4 ch

3 ch

3 ch

Stepper Motor Control

4 ch

4 ch

4 ch

Sound Generator

1 ch

1 ch

1 ch

PPG

8 ch

8 ch

8 ch

Input Capture

4 ch

4 ch

4 ch

Output Compare

4 ch

4 ch

4 ch

Free Running Timer

2 ch

2 ch

2 ch

D/A Converter

2 ch

2 ch

2 ch

A/D Converter

16 ch

16 ch

16 ch

I

2

C 100 kHz

I

2

C 400 kHz

1 ch

1 ch

1 ch

Alarm Comparator

1 ch

1 ch

1 ch

SIO/SIO prescaler

2 ch

2 ch

2 ch

UART/U-Timer

3 ch

3 ch

3 ch

16-bit Reload Timer

6 ch

6 ch

6 ch

Ext. Interrupt

8 ch

8 ch

8 ch

Non maskable Interrupt

1

Real Time Clock

1

1

1

32 kHz subclock option for RTC

yes

no

no

subclock calibration

yes

no

no

LED port

8 bit

8 bit

8 bit

Power down Reset

1

1

1

Bit search Module

1

1

1

Watchdog timer

1

1

1

Ext. Address Bus

32 bit

21 bit

21 bit

Ext. Data Bus

32 bit

32 bit

32 bit

Ext. DMA

3 ch

1 ch

1 ch

Max. operating frequency

64 MHz

64 MHz

64 MHz

MB91360G Series

4

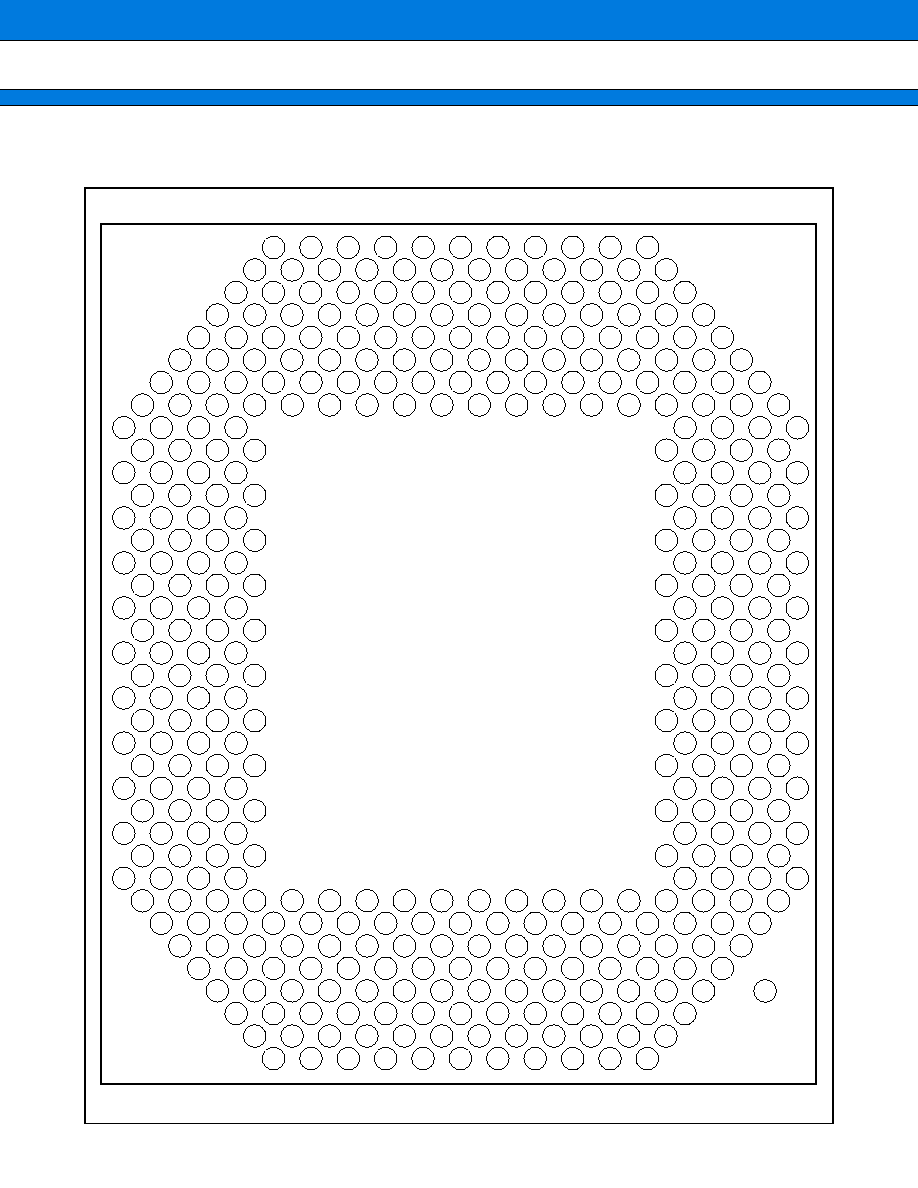

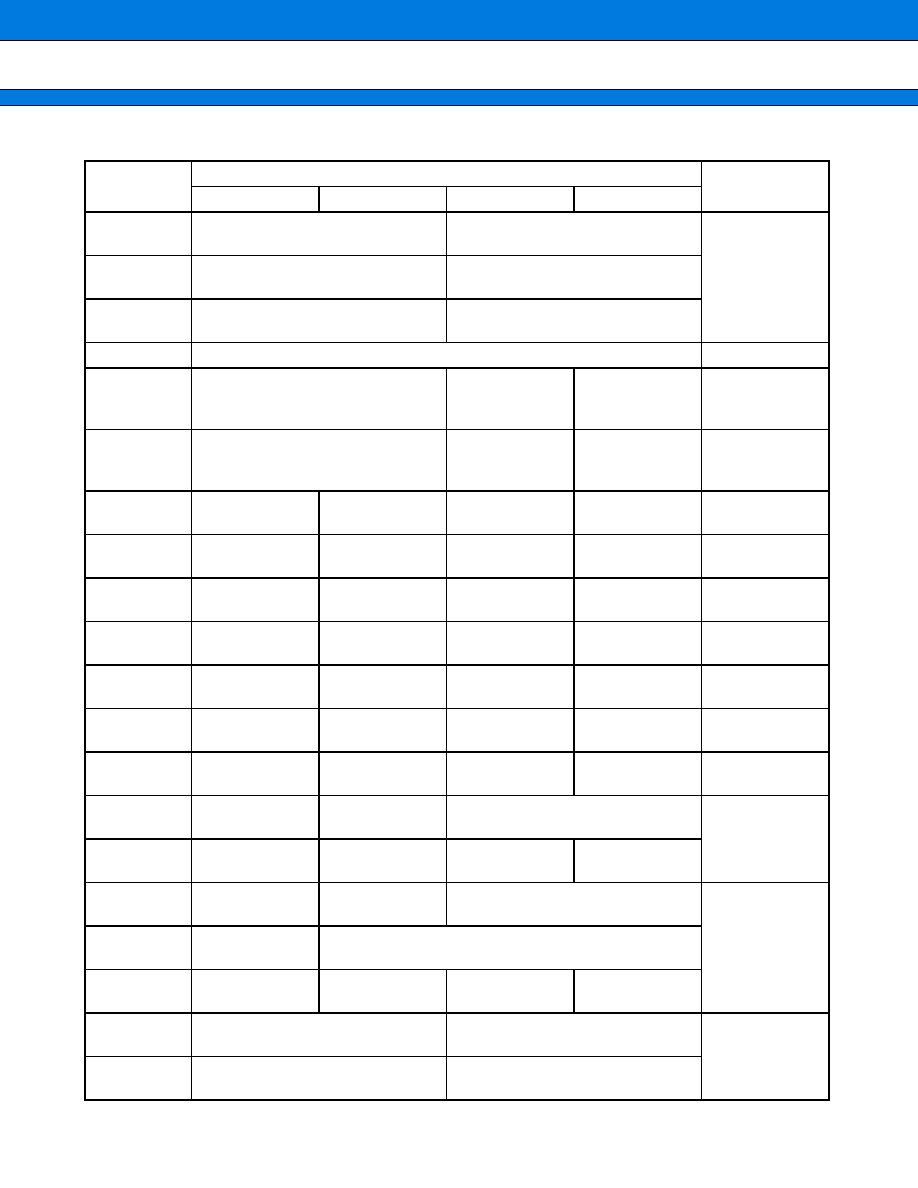

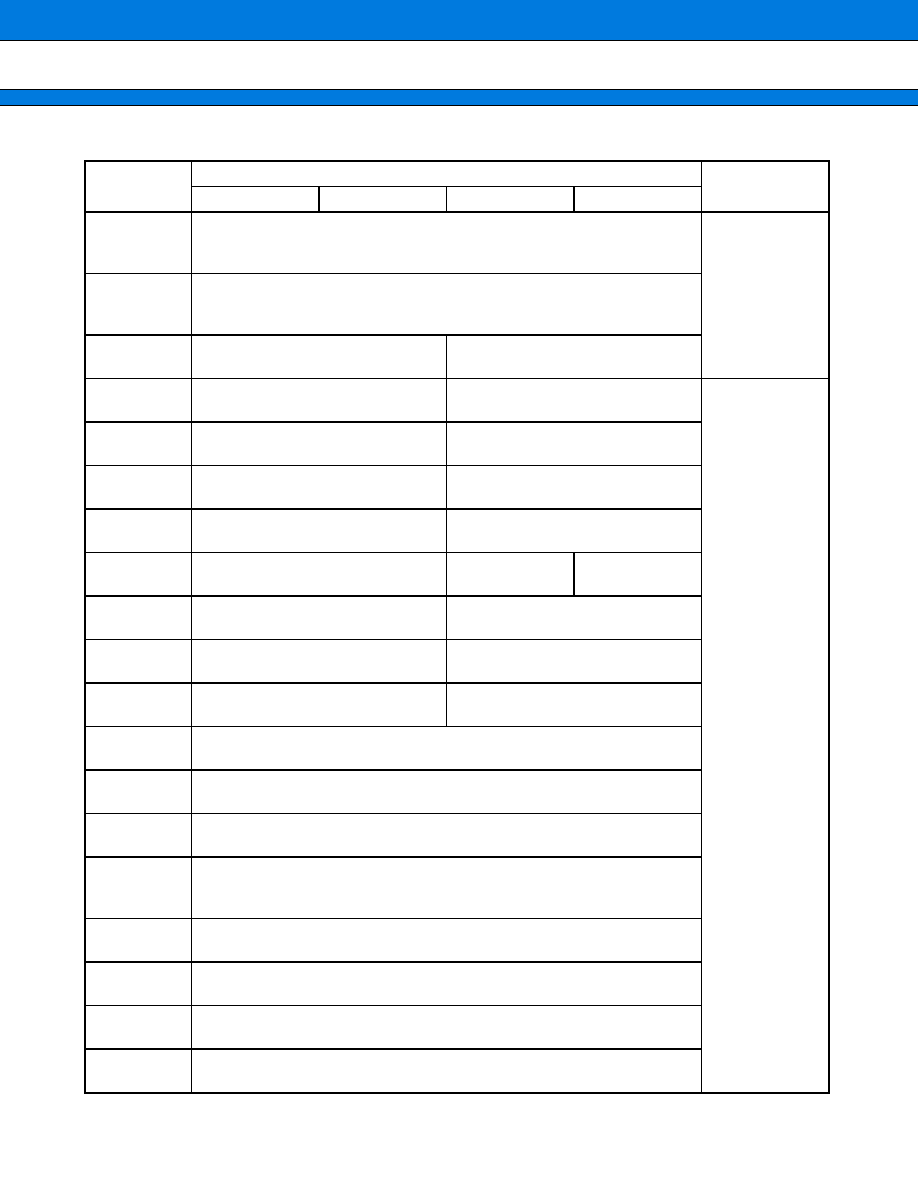

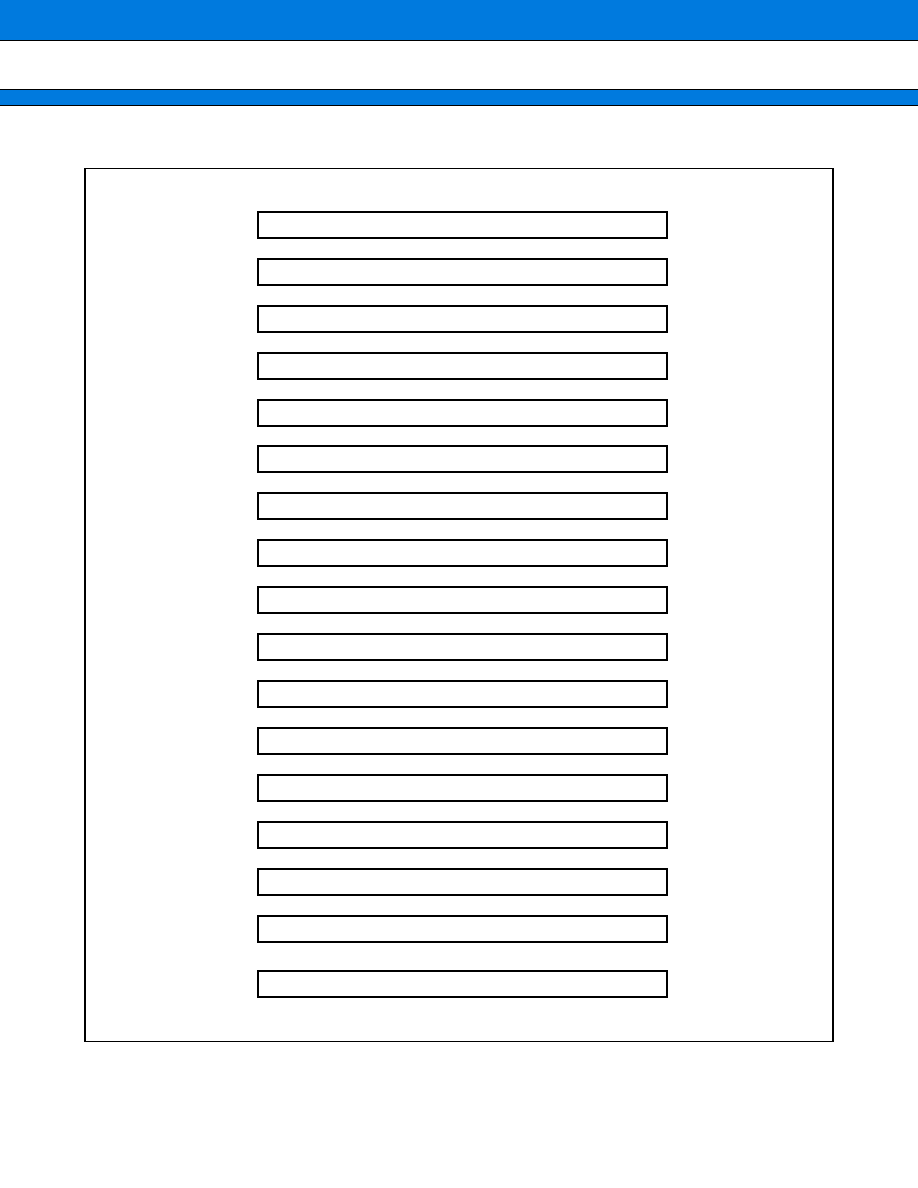

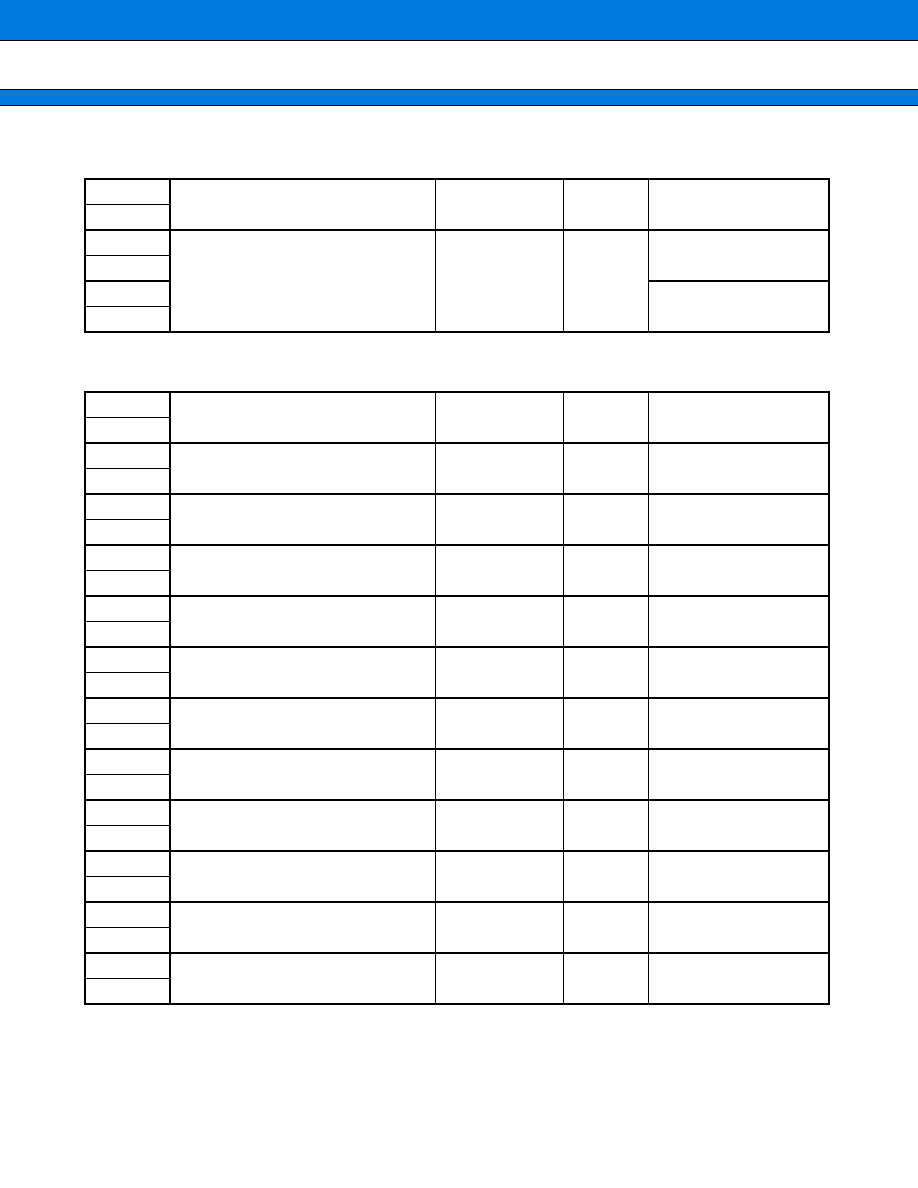

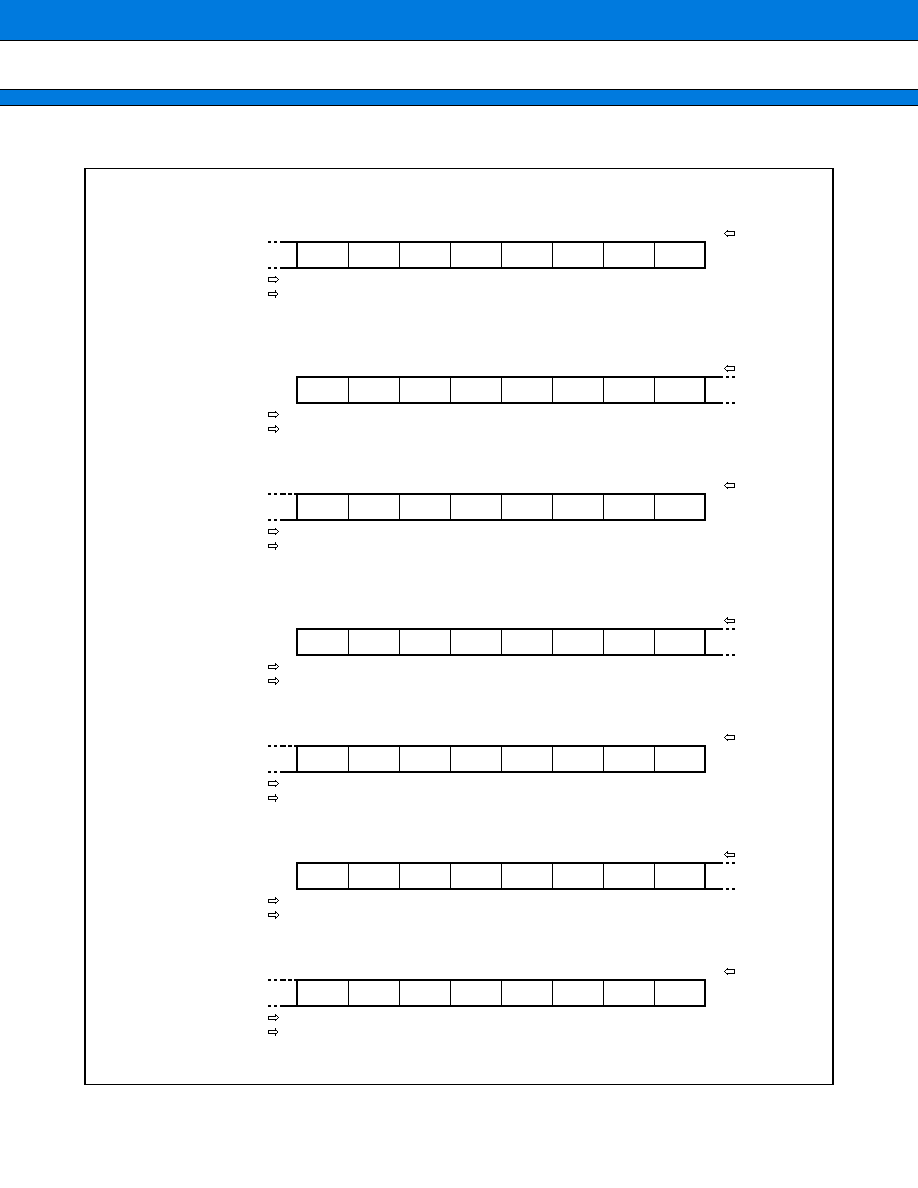

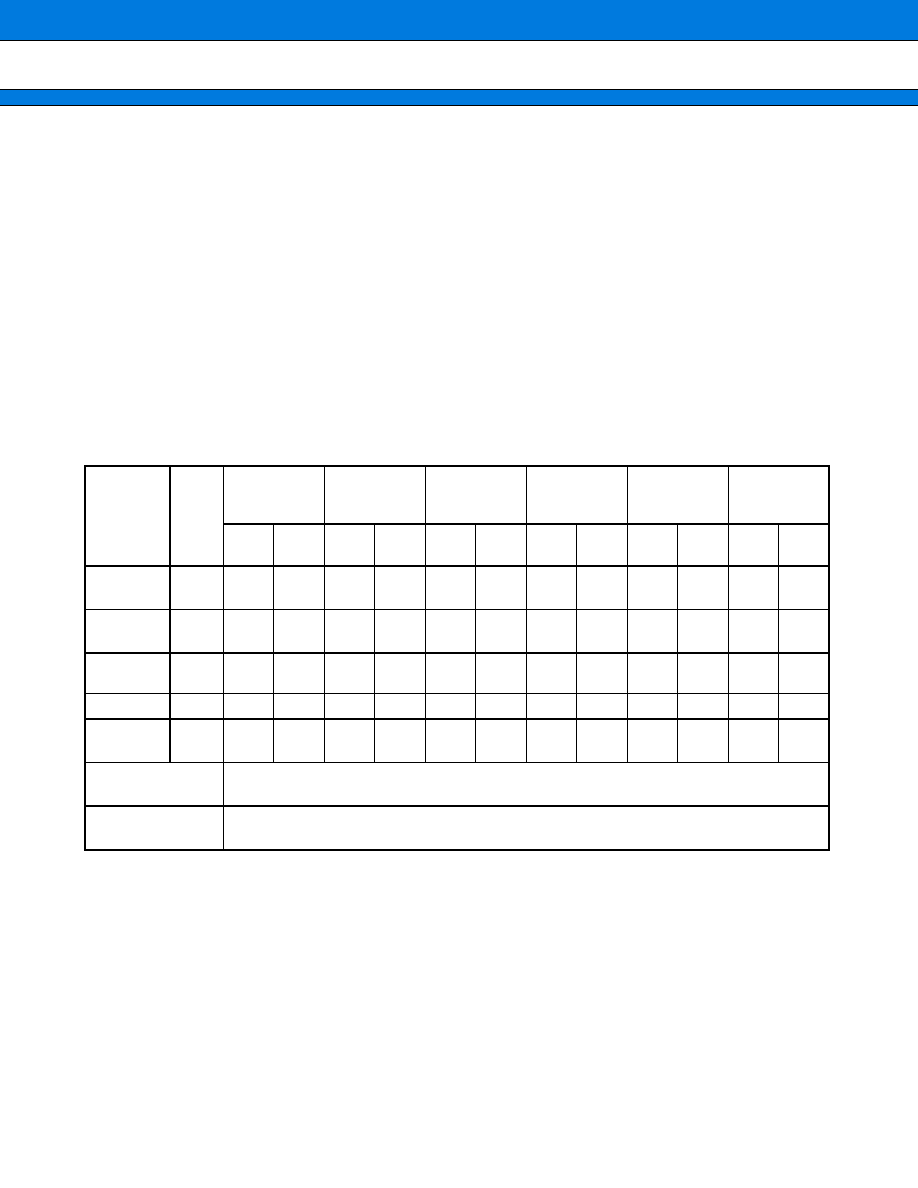

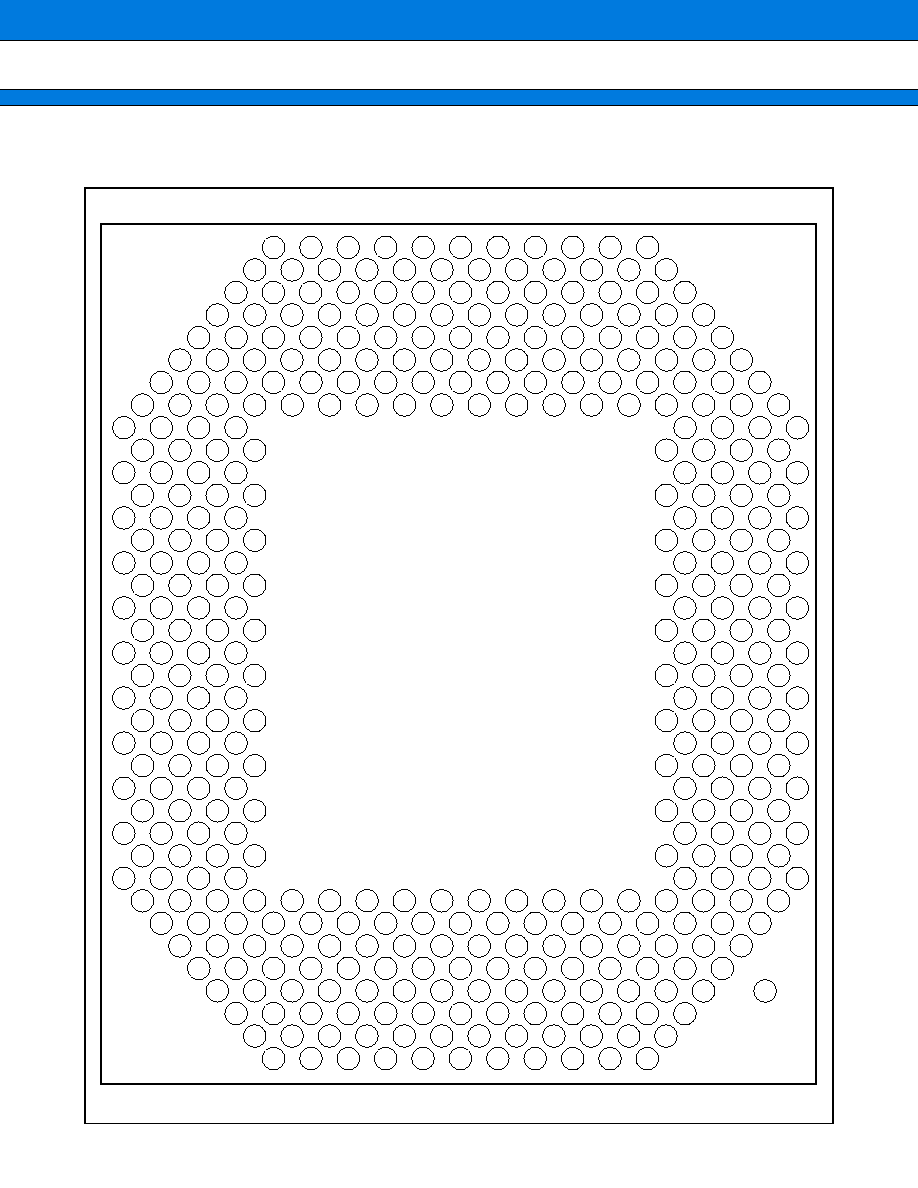

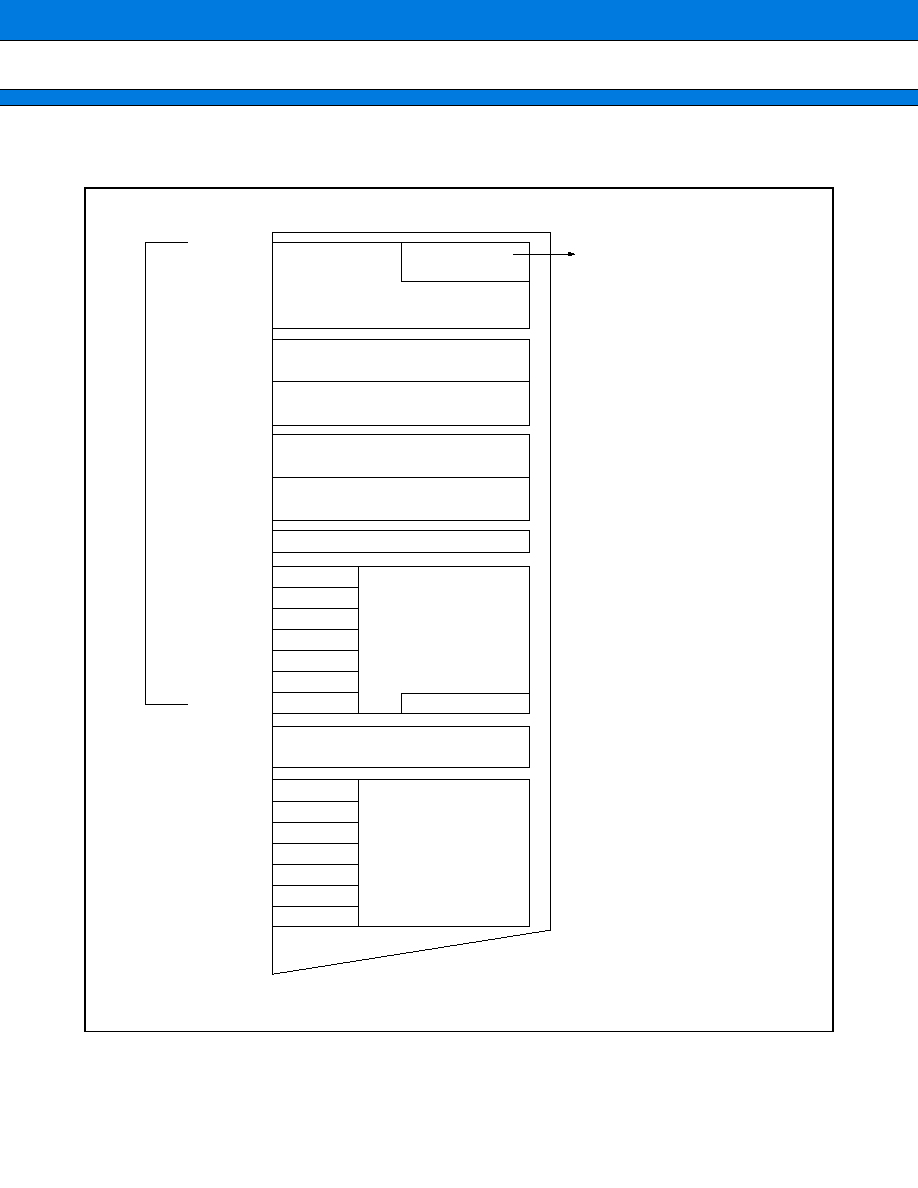

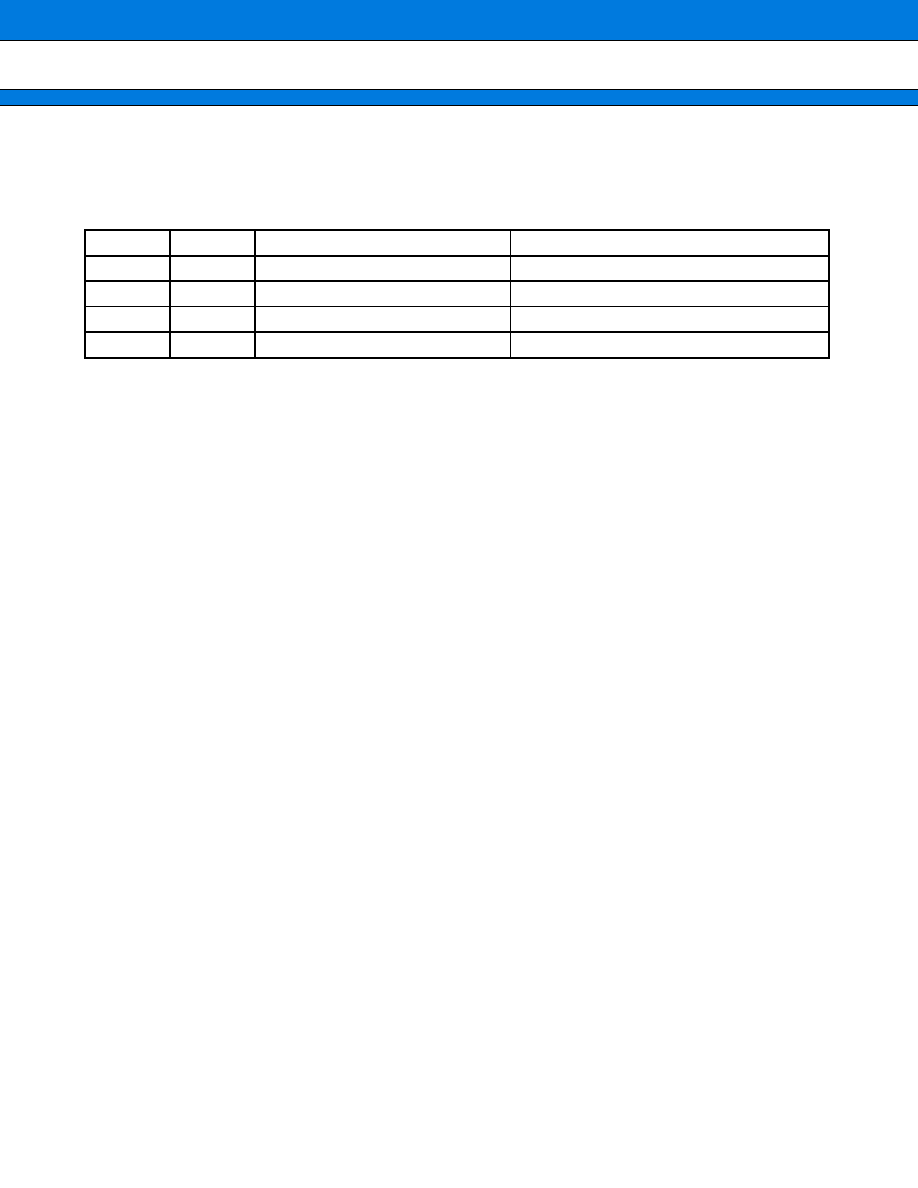

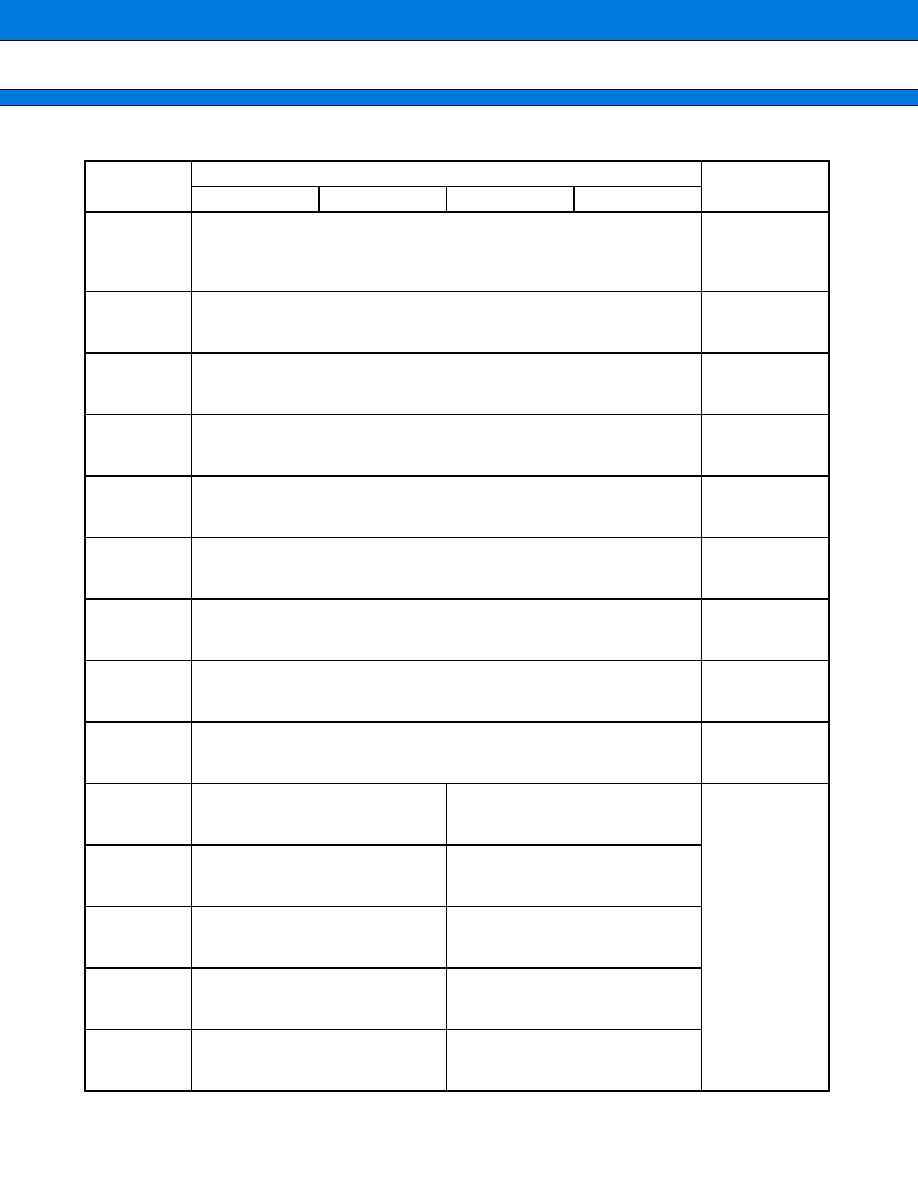

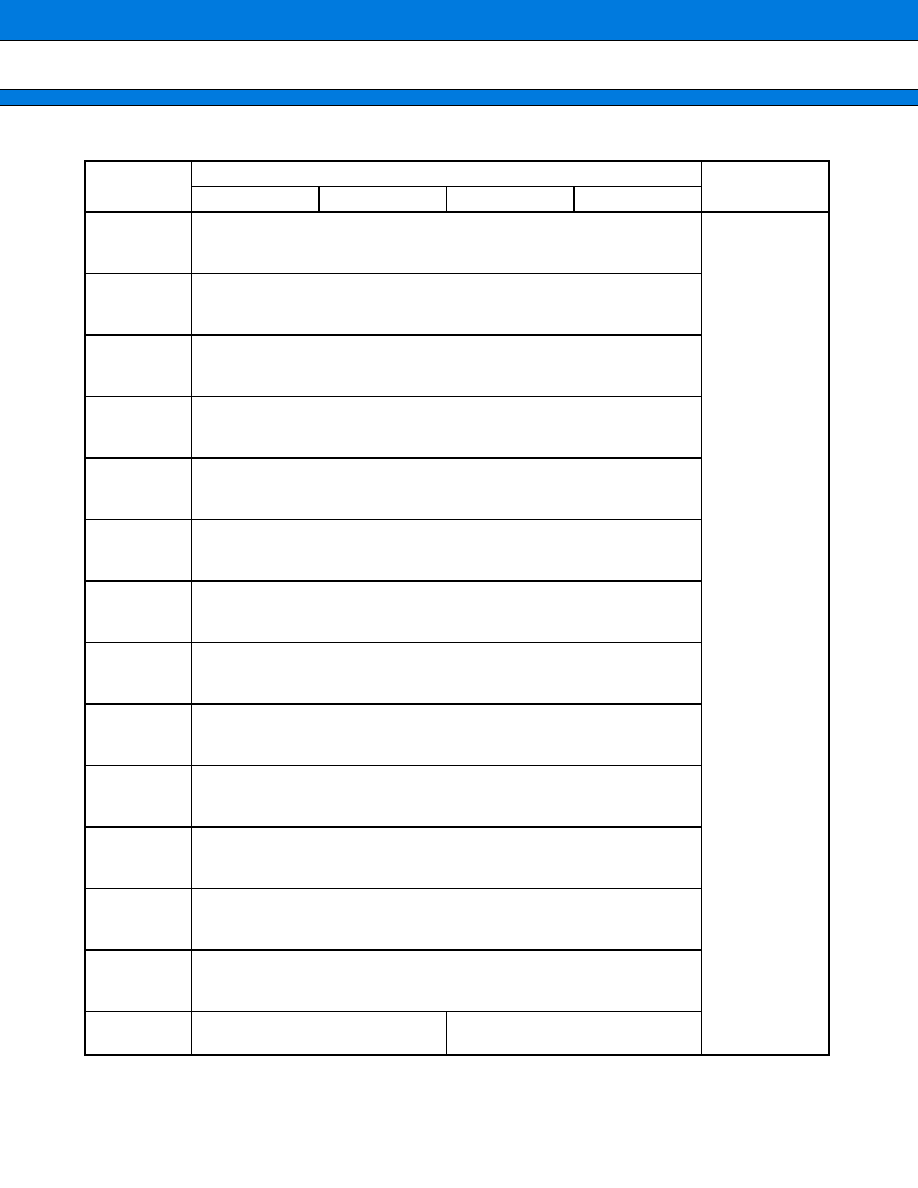

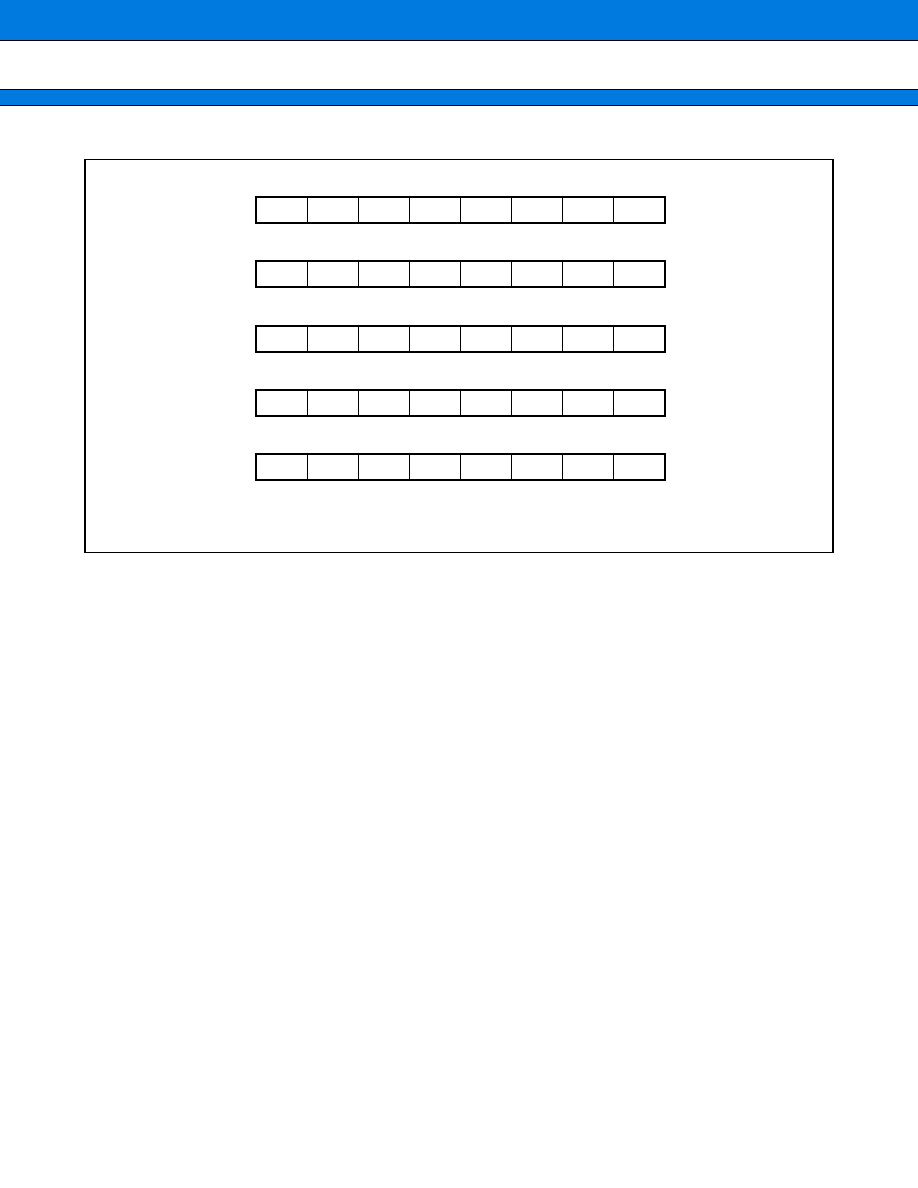

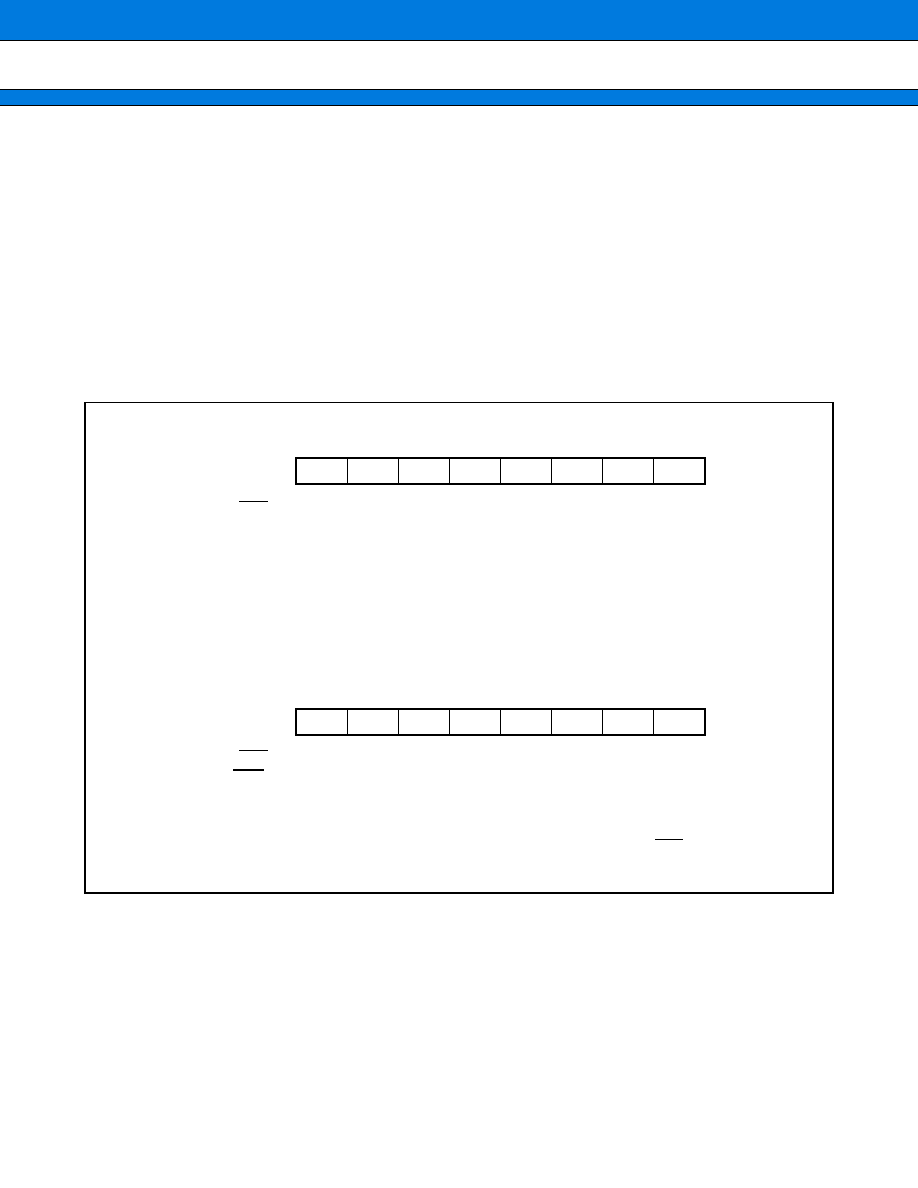

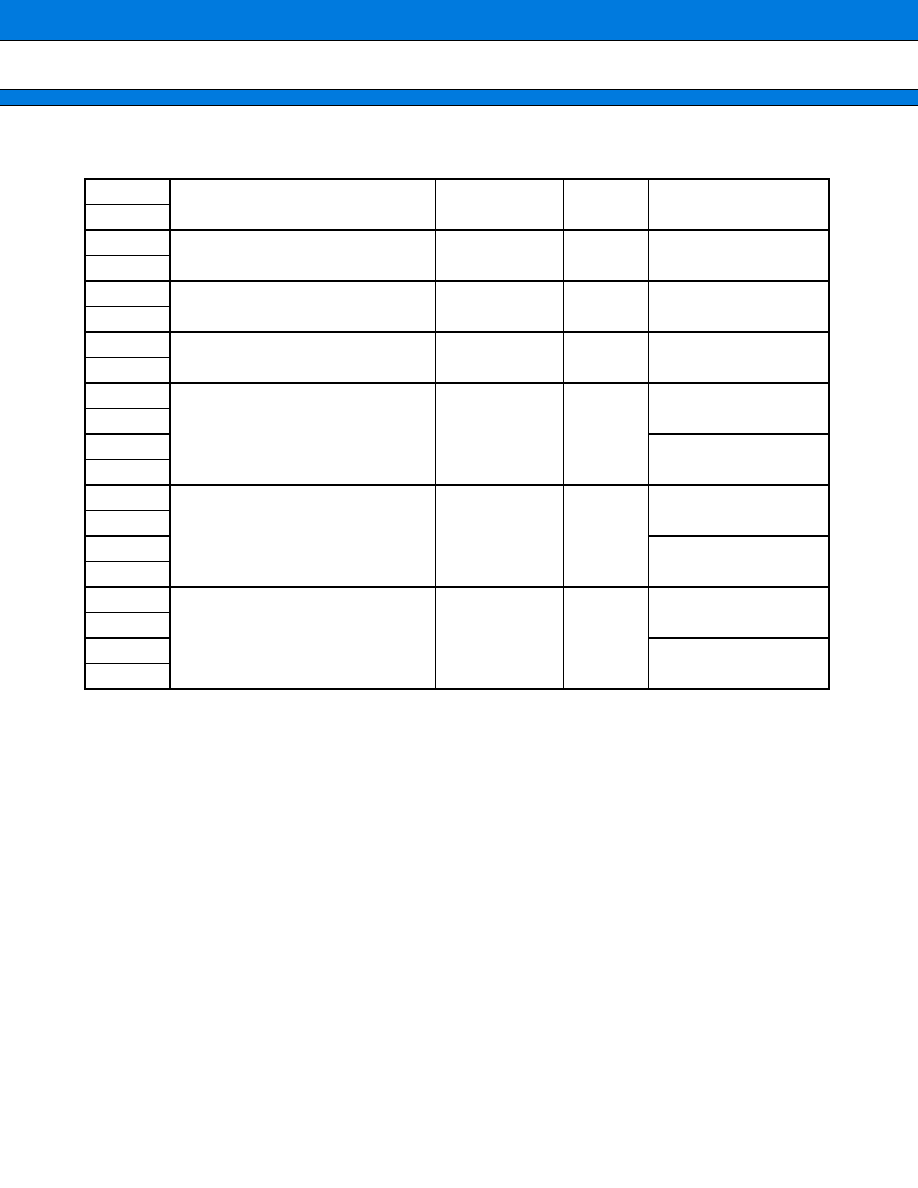

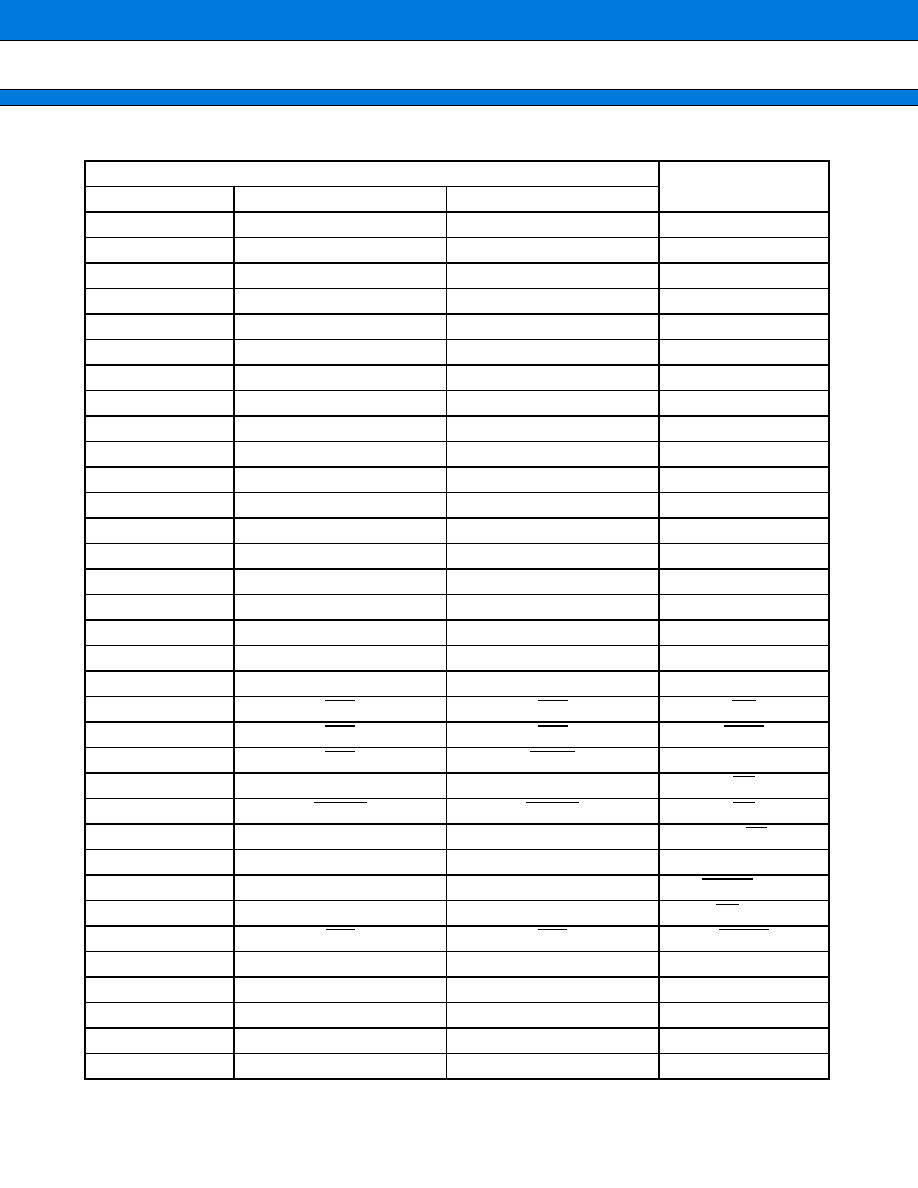

s

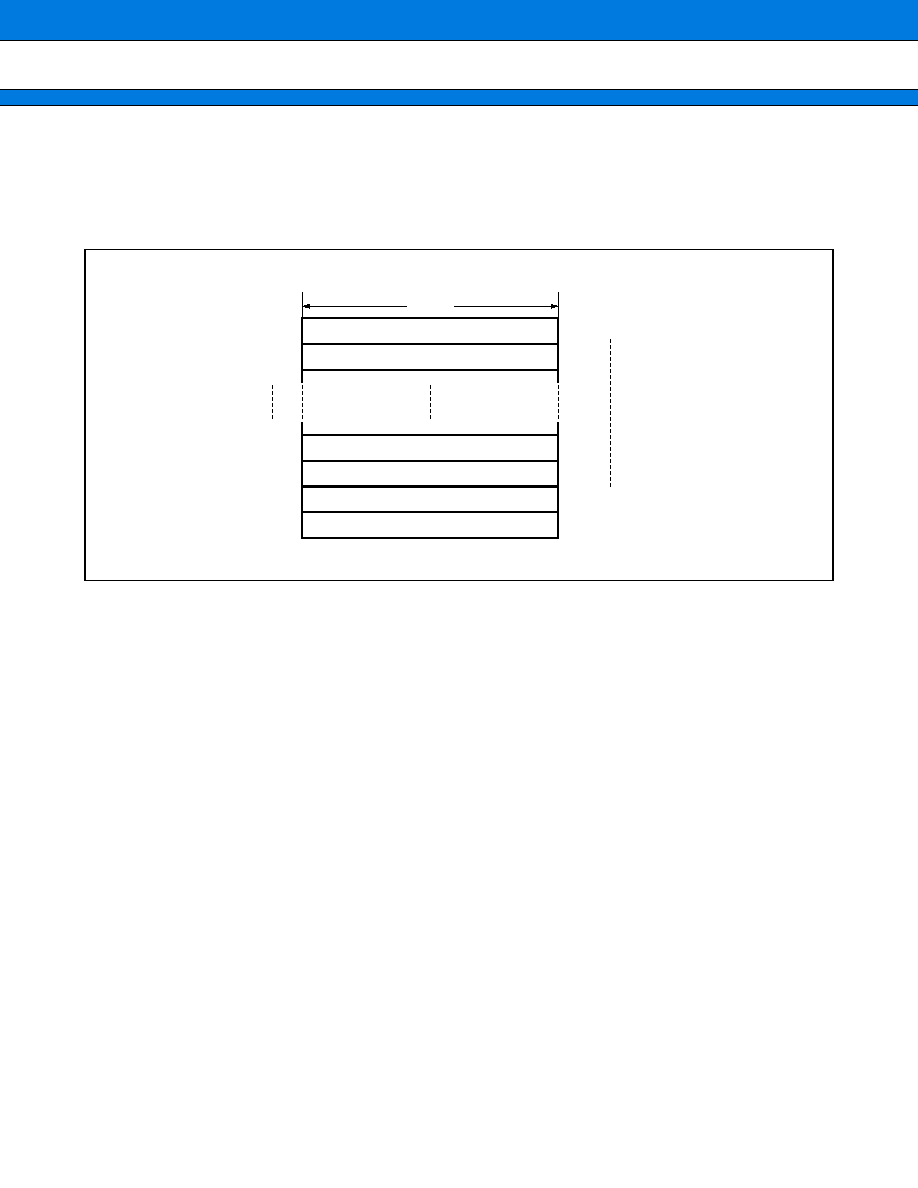

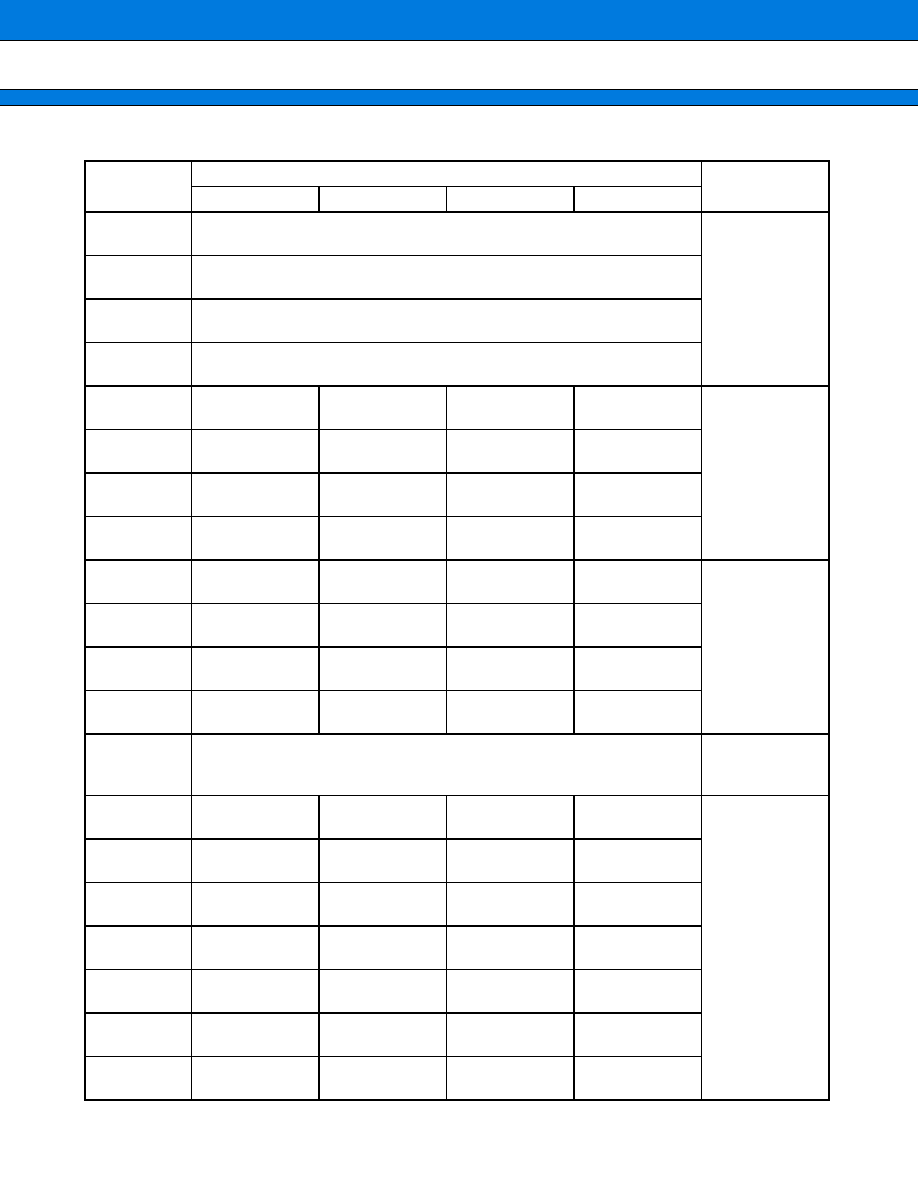

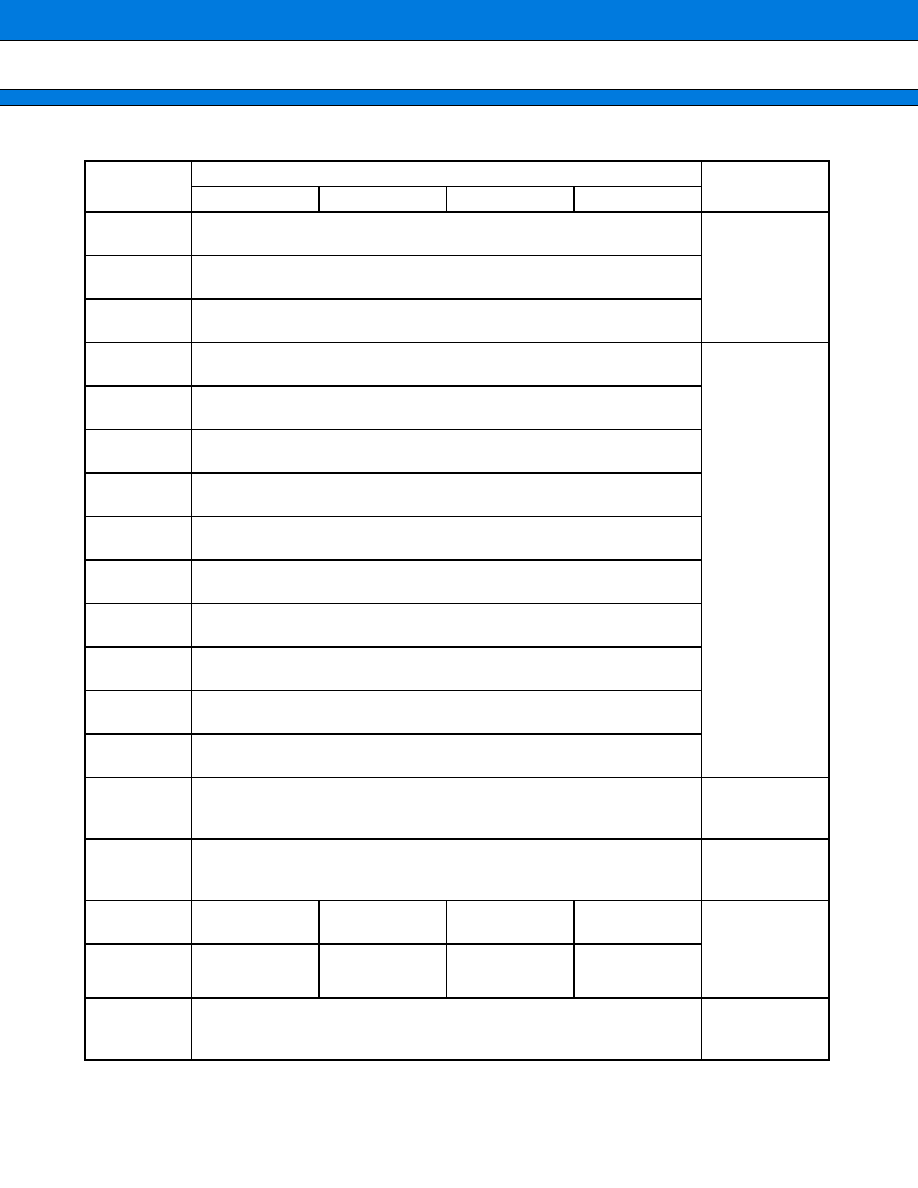

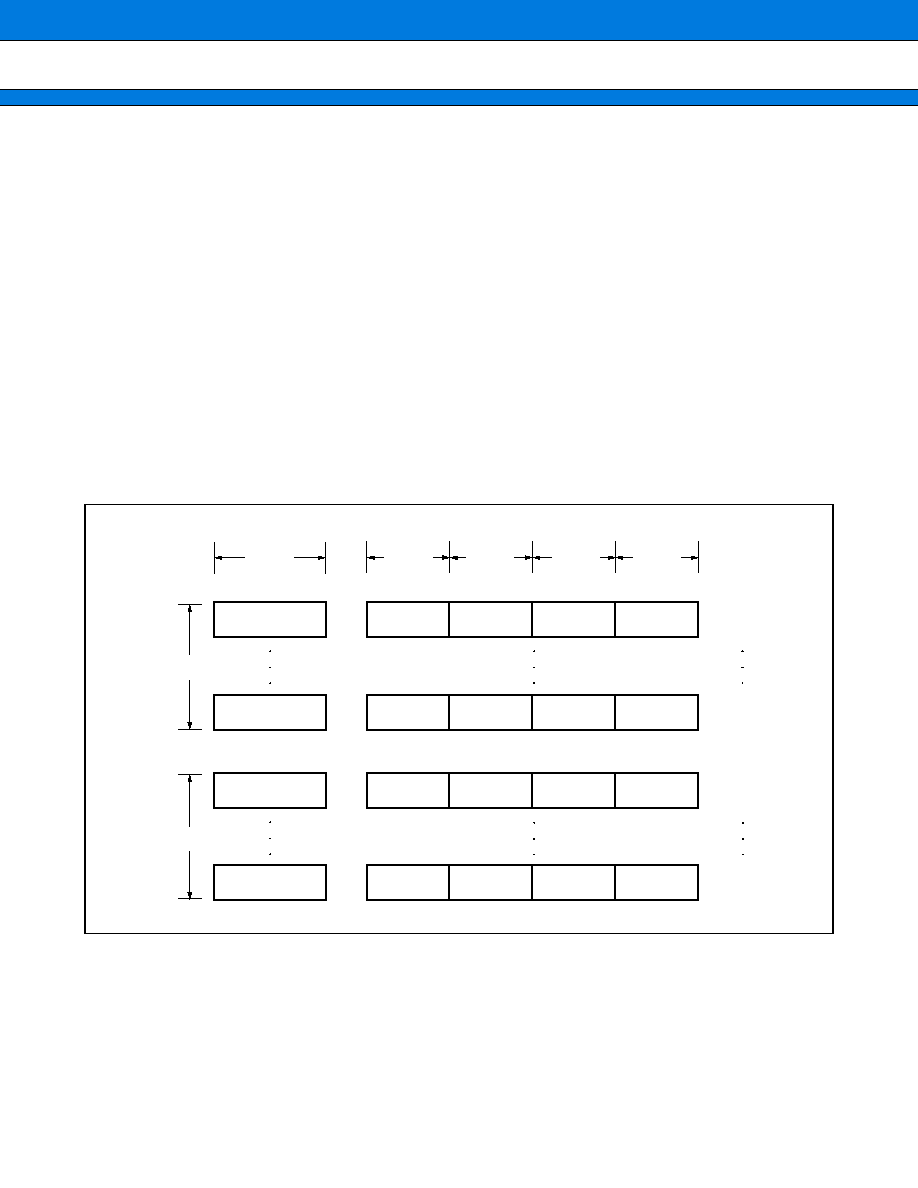

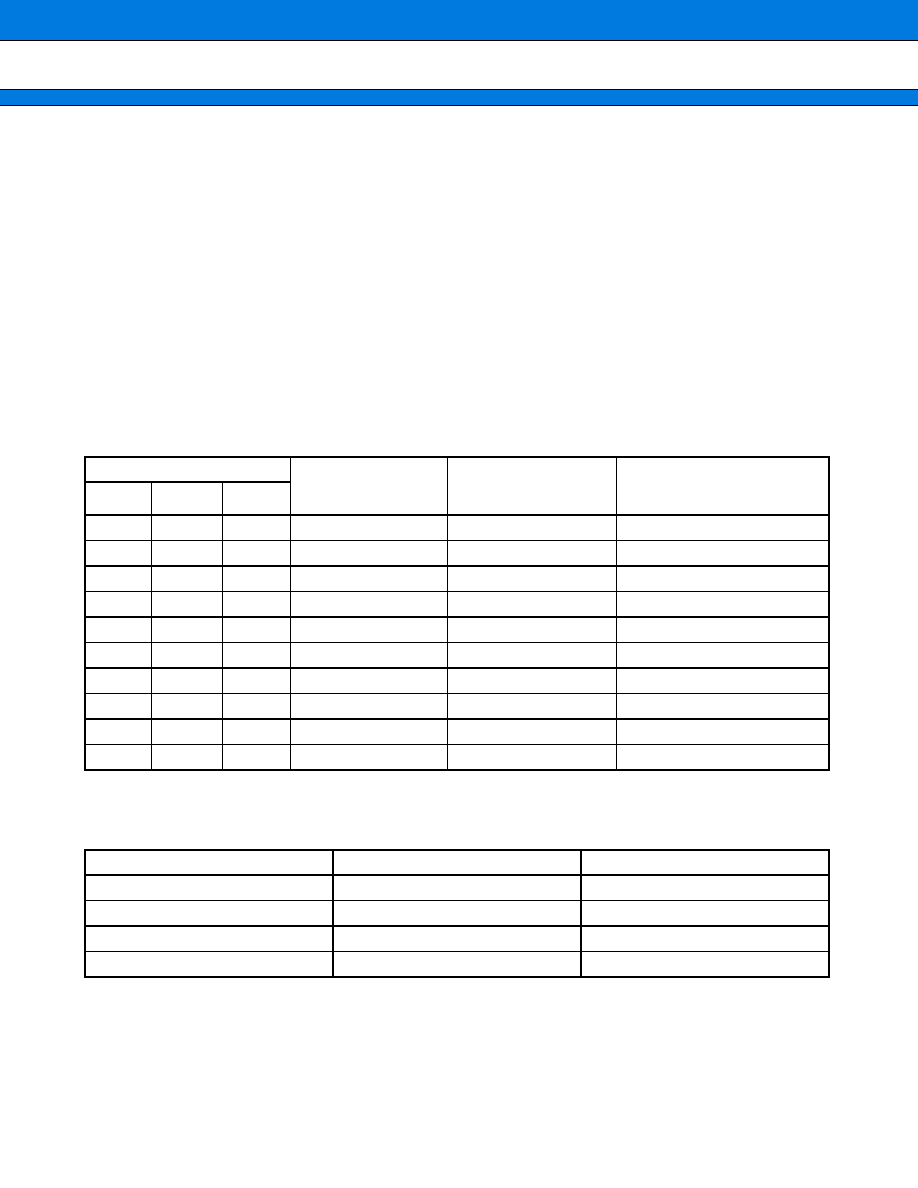

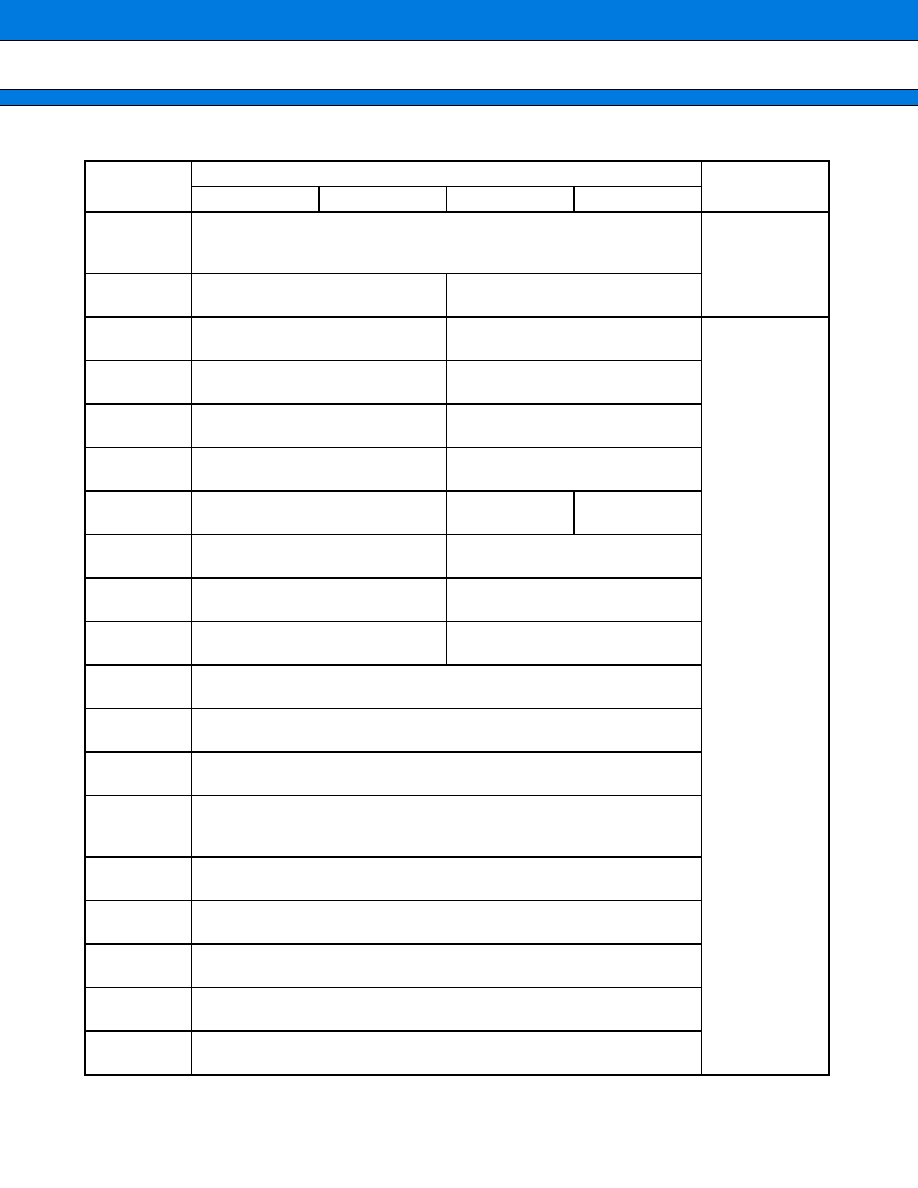

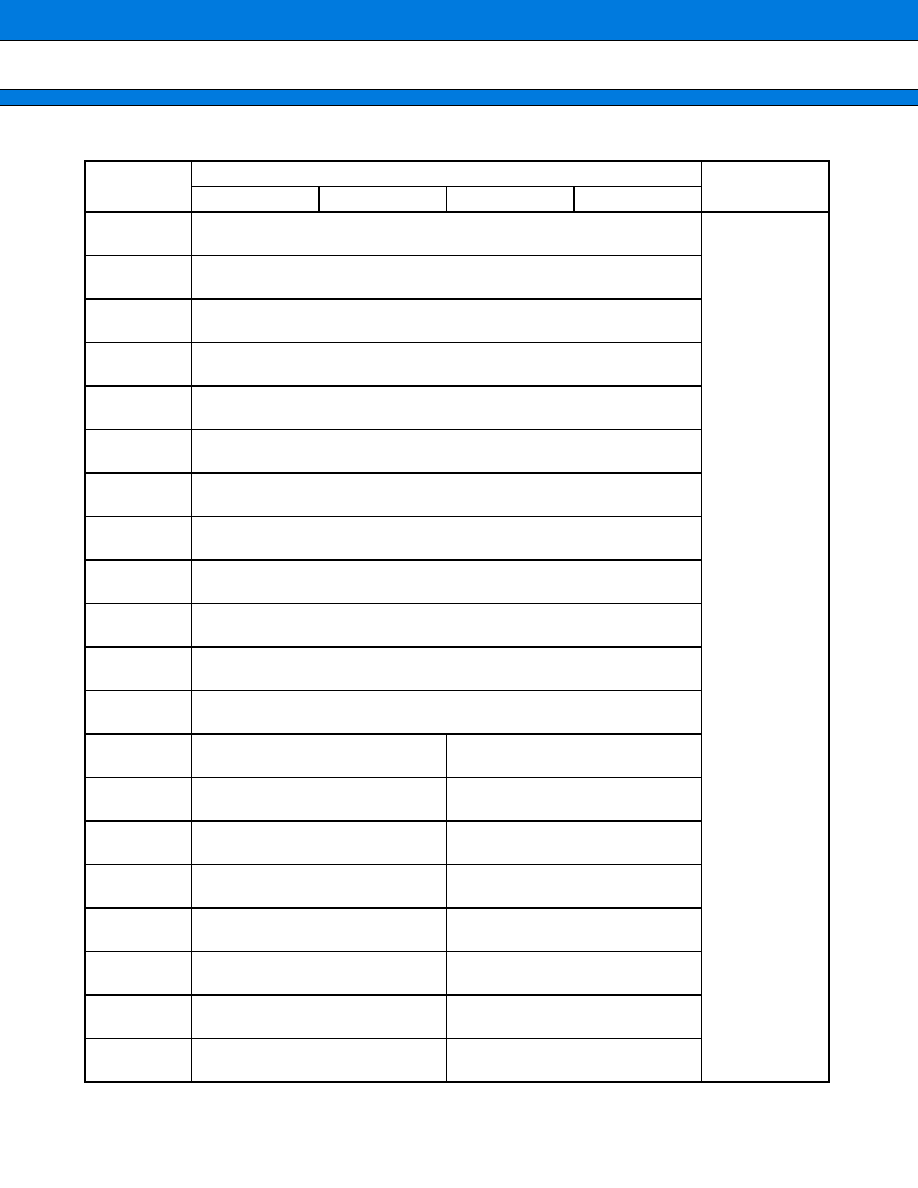

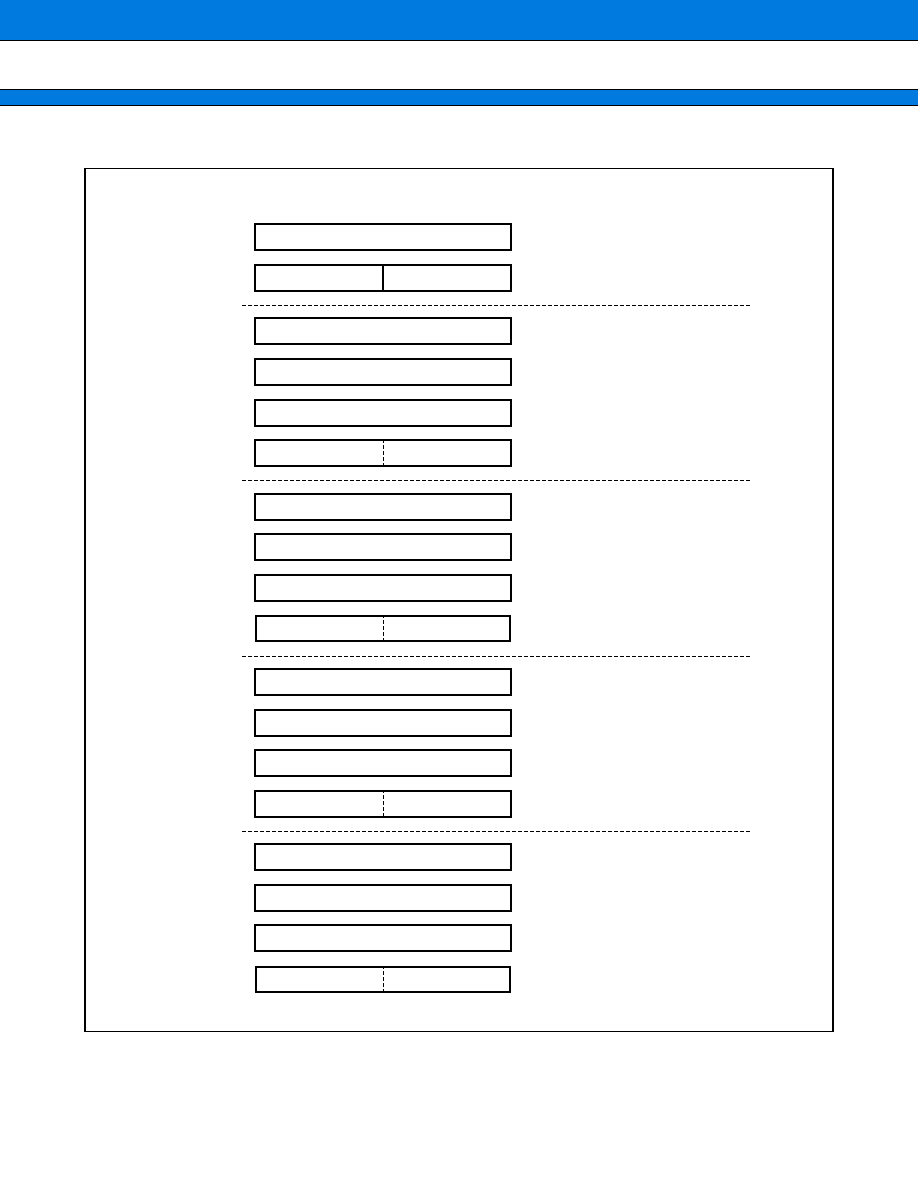

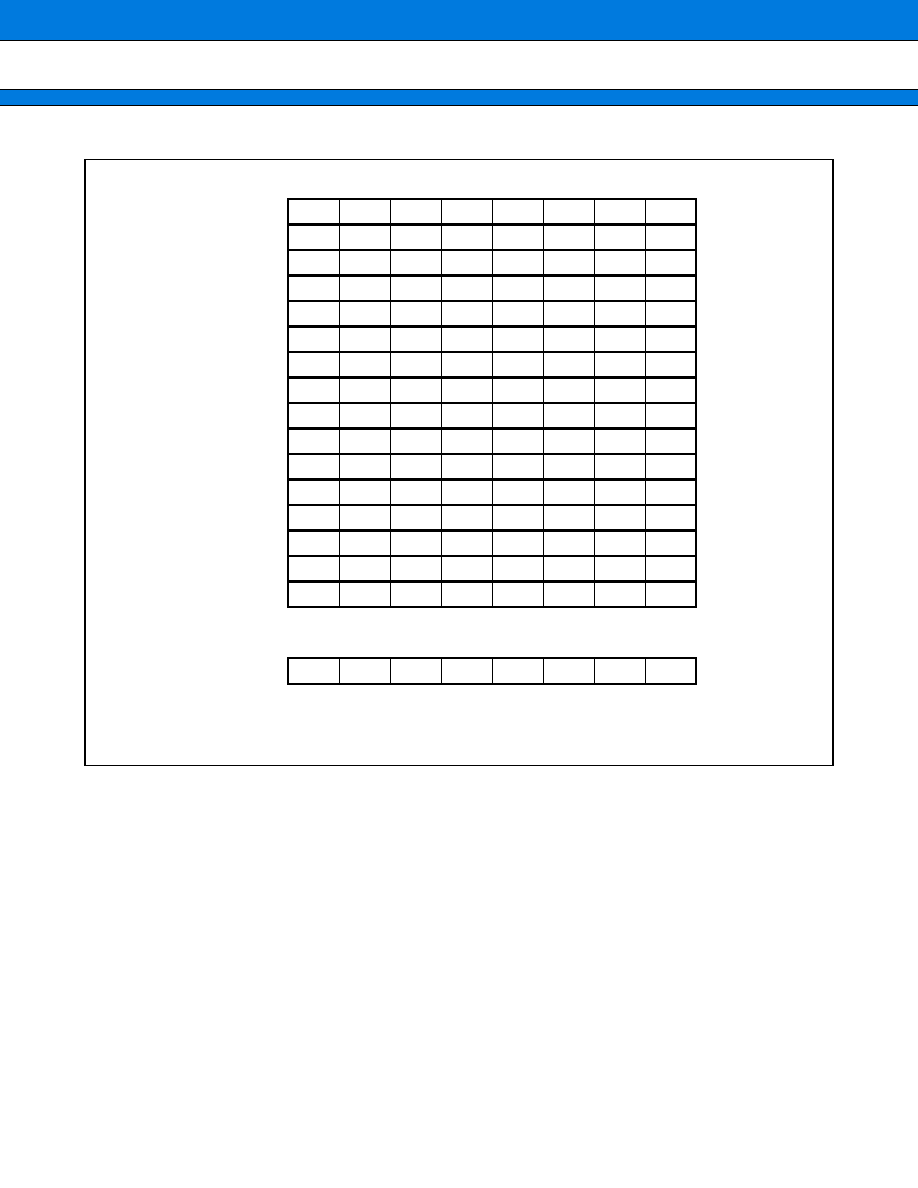

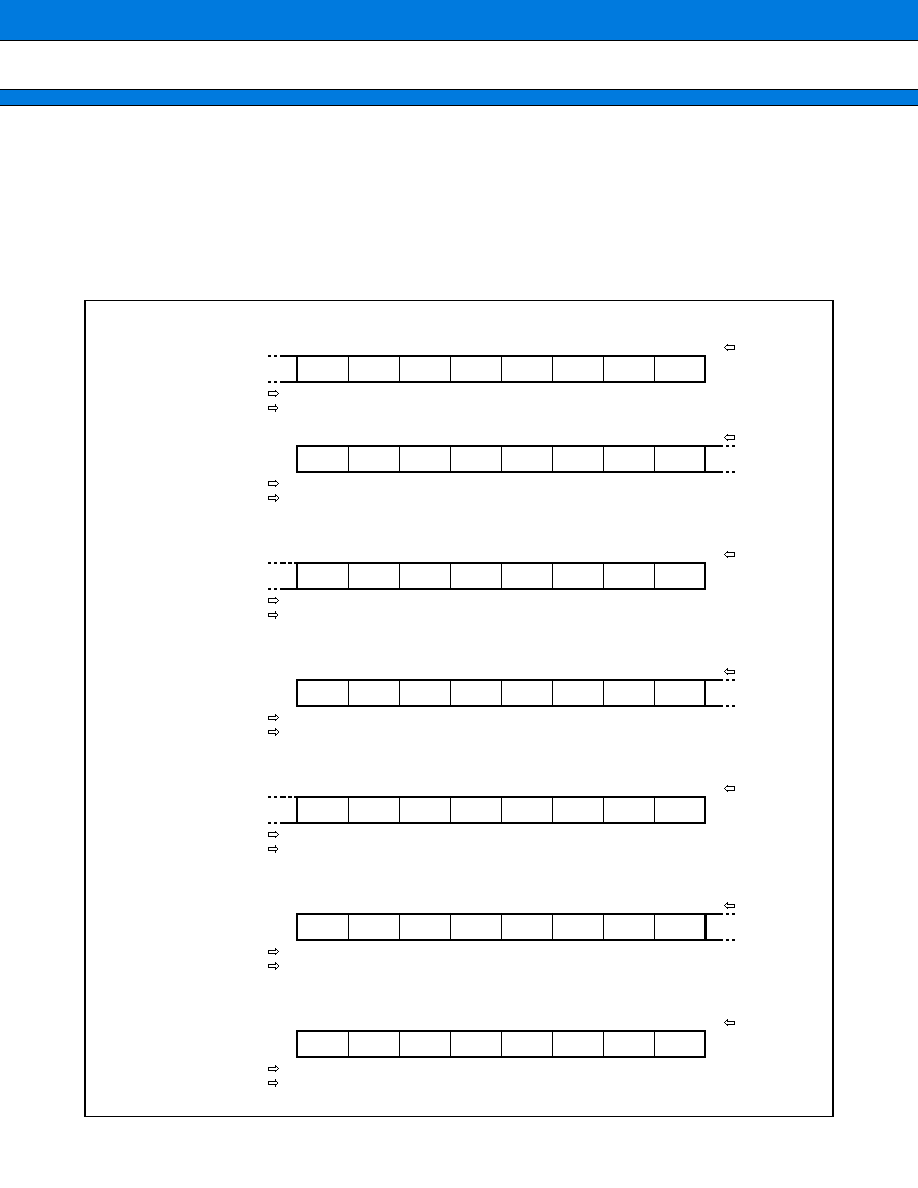

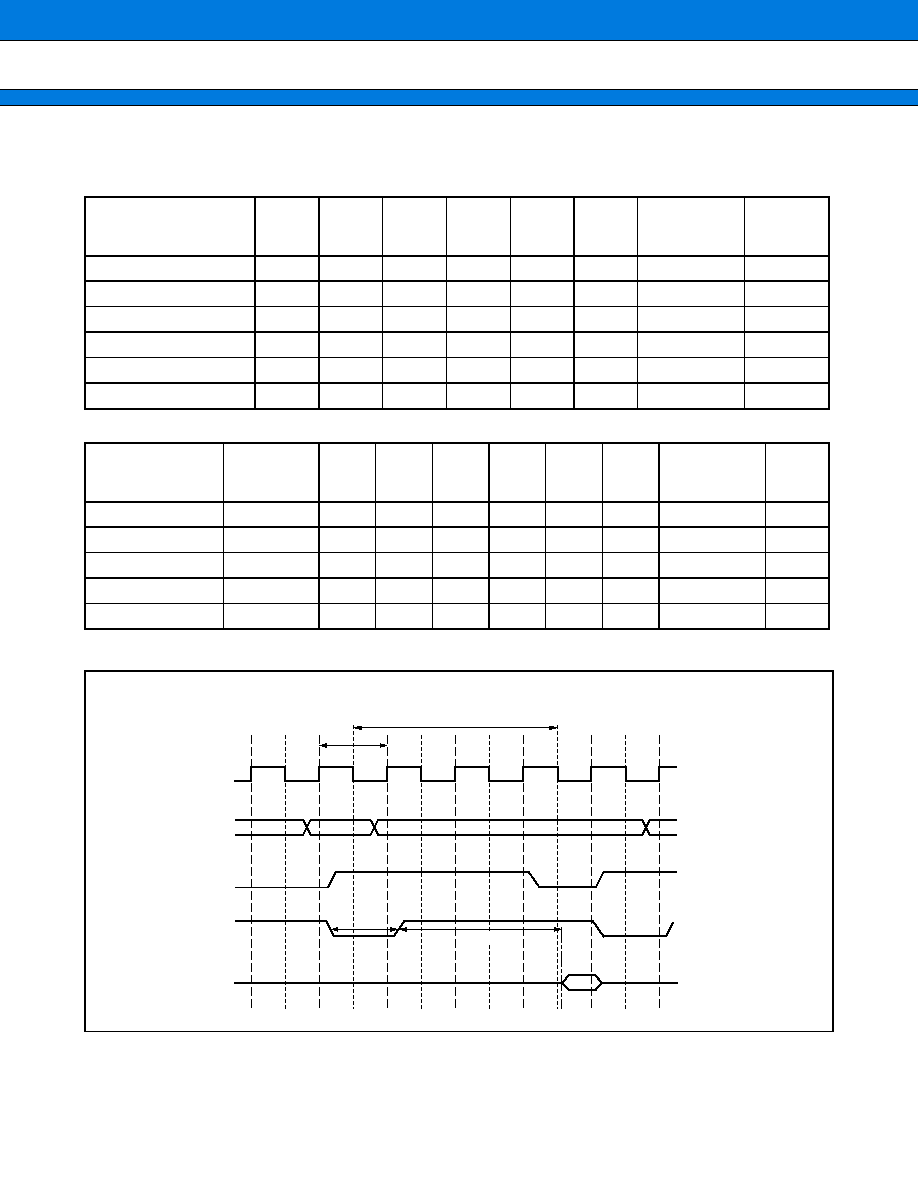

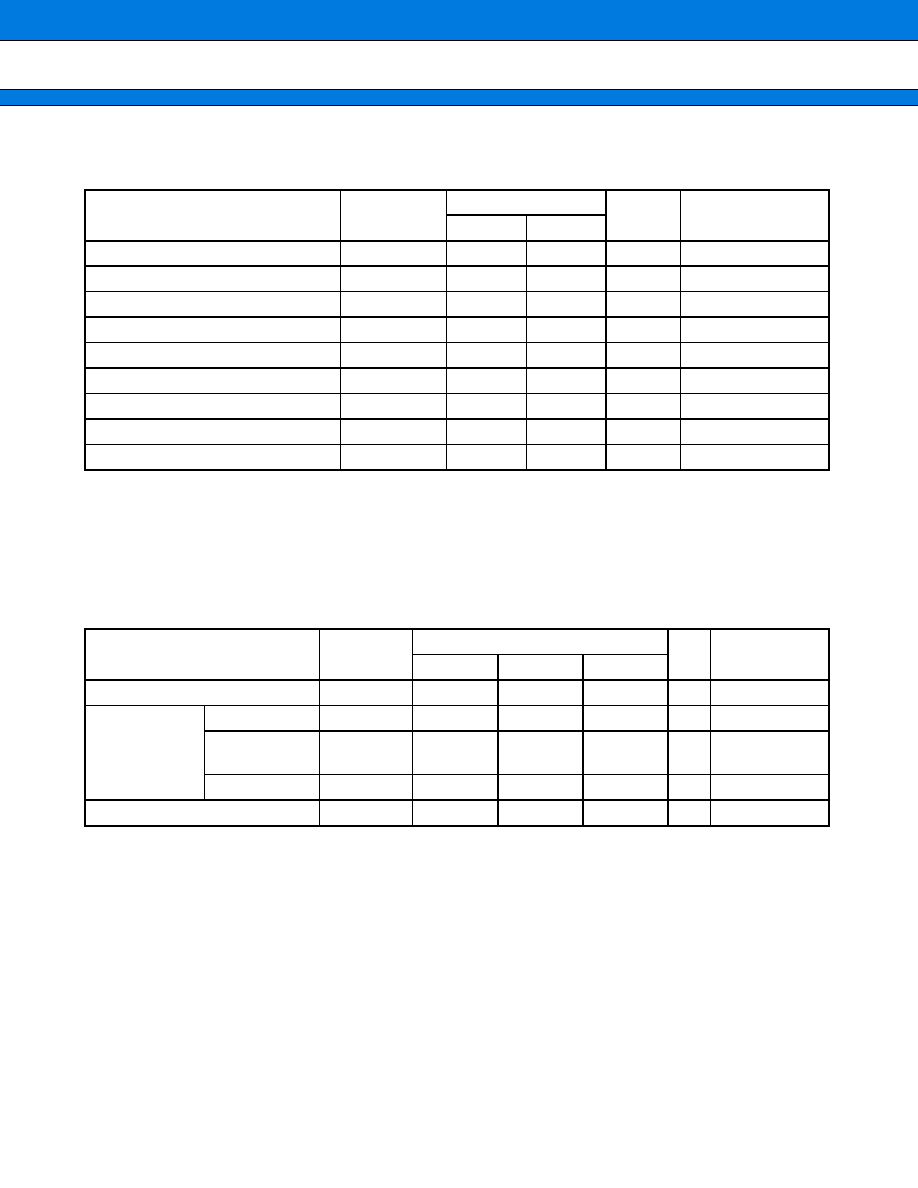

PIN ASSIGNMENTS

∑

MB91FV360GA

(BOTTOM VIEW)

(PGA-401C-A02)

24

23

25

26

27

28

29

30

31

32

33

70

69

71

72

73

74

75

76

77

78

79

80

120

119

121

122

123

124

125

126

127

128

129

130

131

175

174

176

177

178

179

180

181

182

183

184

185

186

187

231

230

232

233

234

235

236

237

238

239

240

241

242

243

244

284

173

285

286

287

288

289

290

291

292

293

294

295

296

297

188

229

118

334

335

336

337

338

339

340

341

342

343

344

345

346

245

132

172

68

22

117

228

333

67

171

282

379

21

116

227

332

66

170

281

378

20

115

226

331

65

169

280

377

19

114

225

330

64

168

279

376

18

113

224

329

63

167

278

375

17

112

223

328

62

166

277

374

16

111

222

327

61

165

276

373

15

110

221

326

60

164

275

372

14

109

220

325

59

163

274

371

13

108

219

324

58

162

273

370

12

107

218

323

57

161

272

369

368

367

366

365

364

363

362

361

360

359

358

320

319

318

317

316

315

314

313

312

311

310

257

144

201

268

267

266

265

264

263

262

261

260

259

258

212

211

210

209

208

207

206

205

204

203

202

155

154

153

152

151

150

149

148

147

146

145

101

100

99

98

97

96

95

94

93

52

51

50

49

48

47

46

45

7

6

5

4

3

2

1

309

200

92

106

217

322

321

160

271

270

269

216

215

214

213

159

158

157

156

105

104

103

102

56

55

54

53

11

10

9

8

283

380

381

382

383

384

385

386

387

388

389

390

391

298

189

81

347

246

133

34

392

299

190

82

348

247

134

35

393

300

191

83

349

248

135

36

394

301

192

84

350

249

136

37

395

302

193

85

351

250

137

38

396

303

194

86

352

251

138

39

397

304

195

87

353

252

139

40

398

305

196

88

354

253

140

41

399

306

197

89

355

254

141

42

400

307

198

90

356

255

142

43

401

308

199

91

357

256

143

44

INDEX

MB91360G Series

5

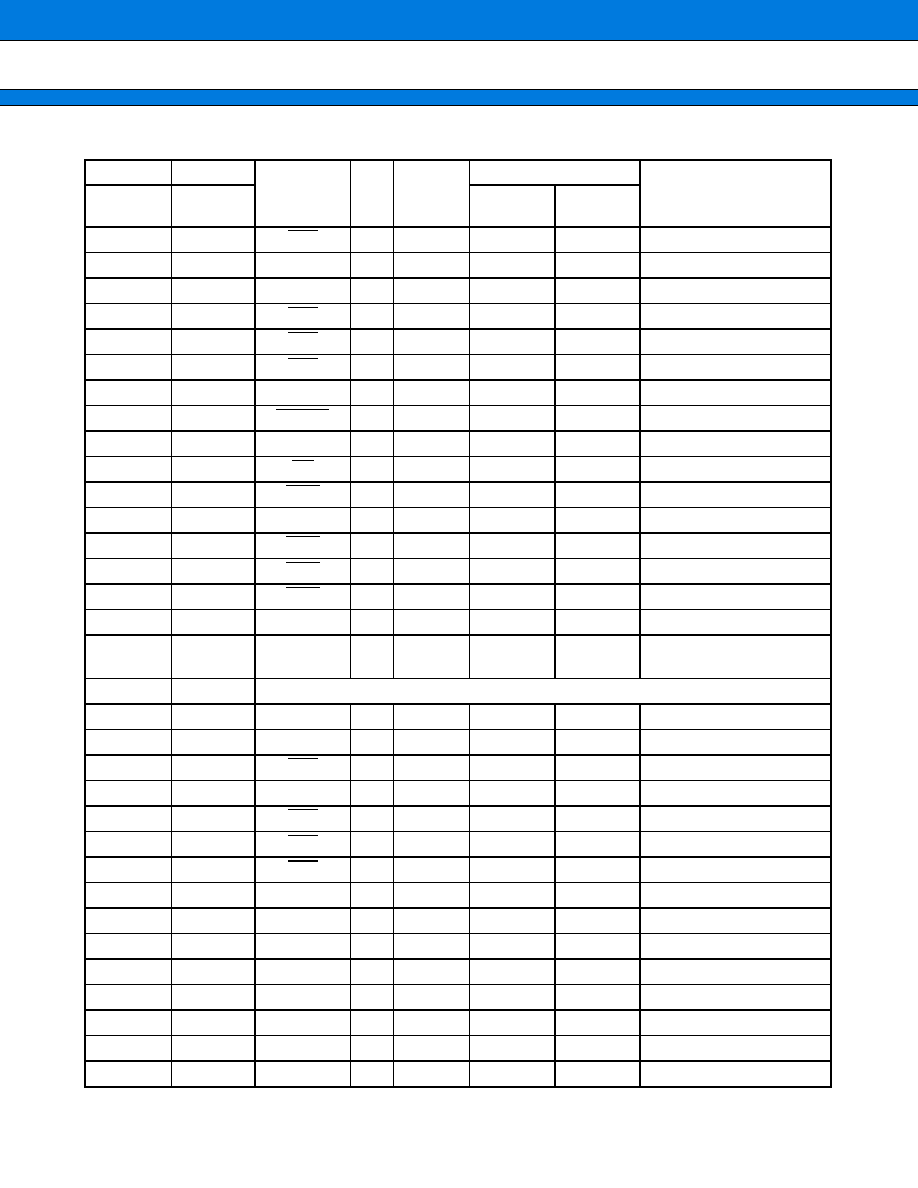

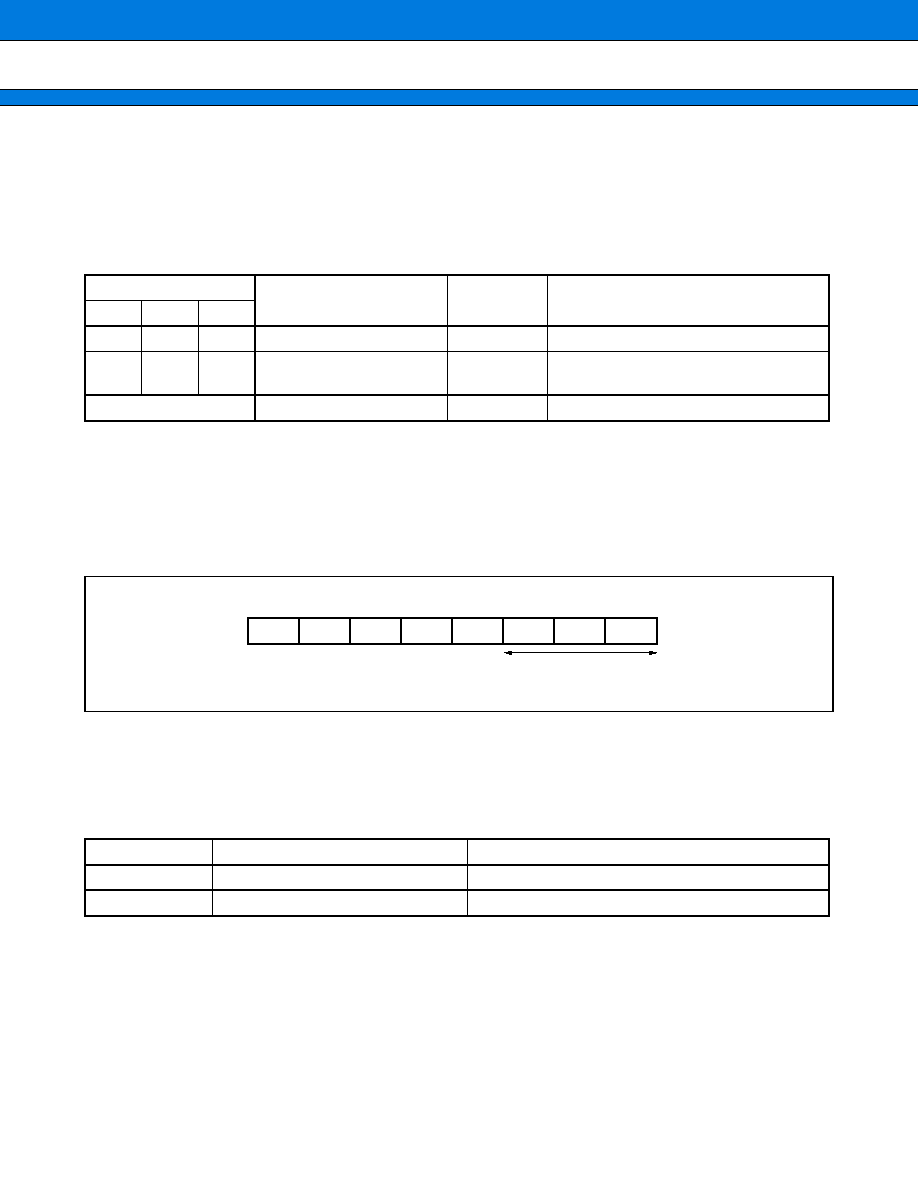

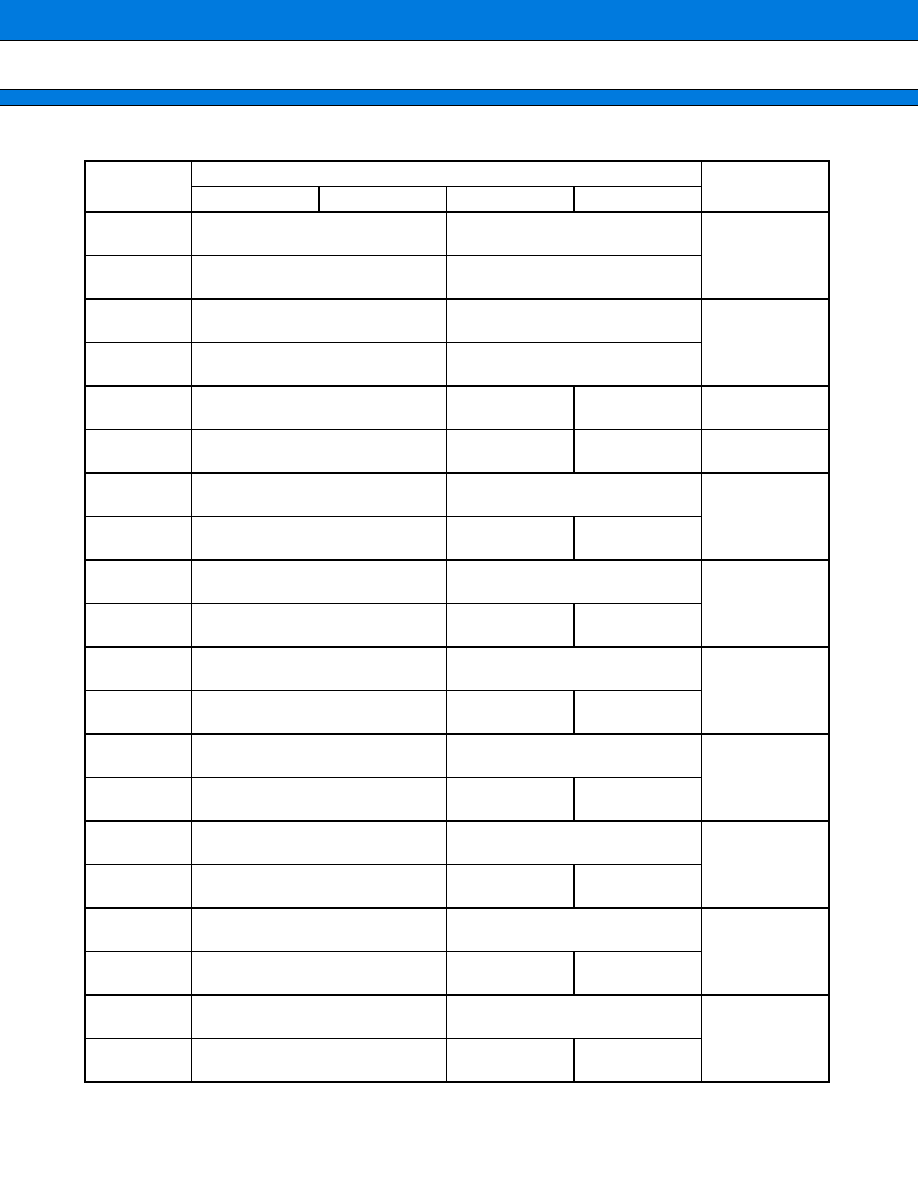

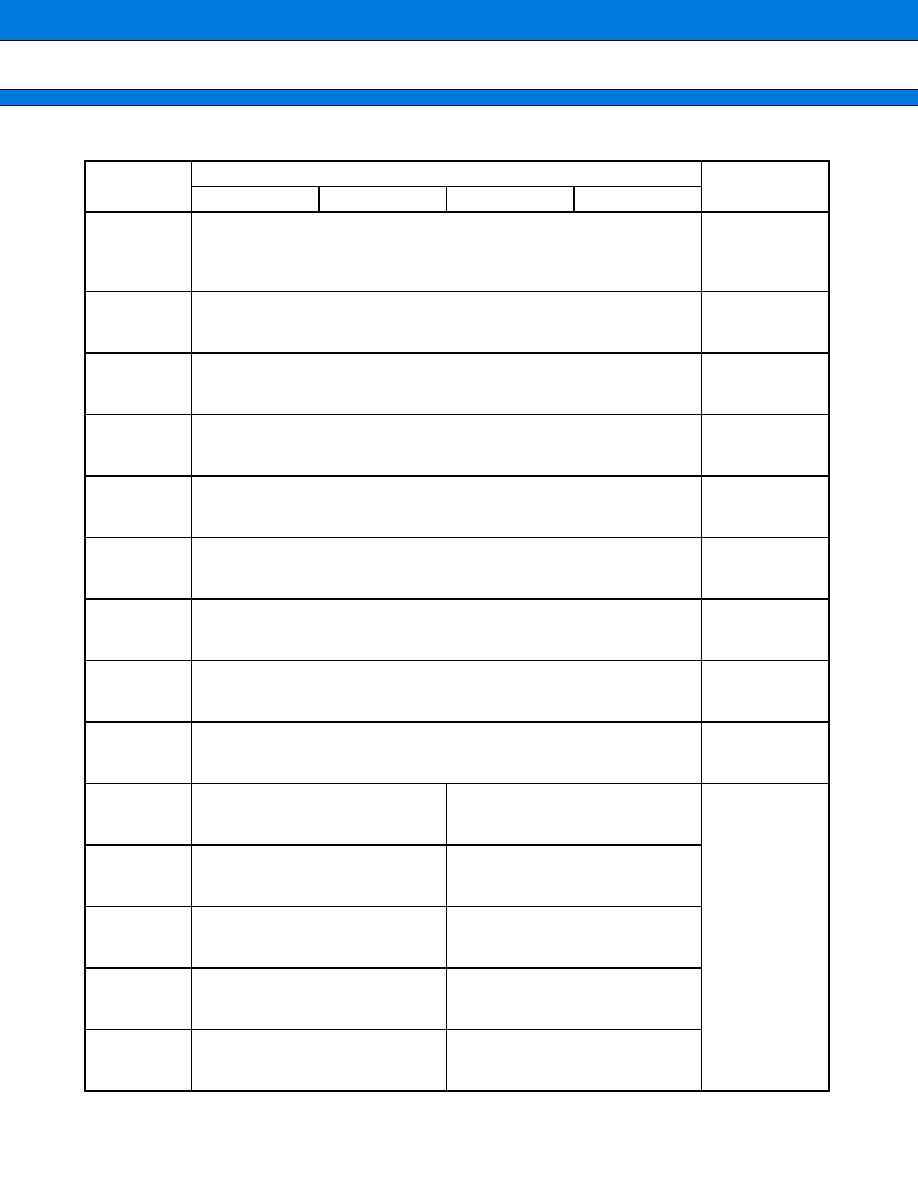

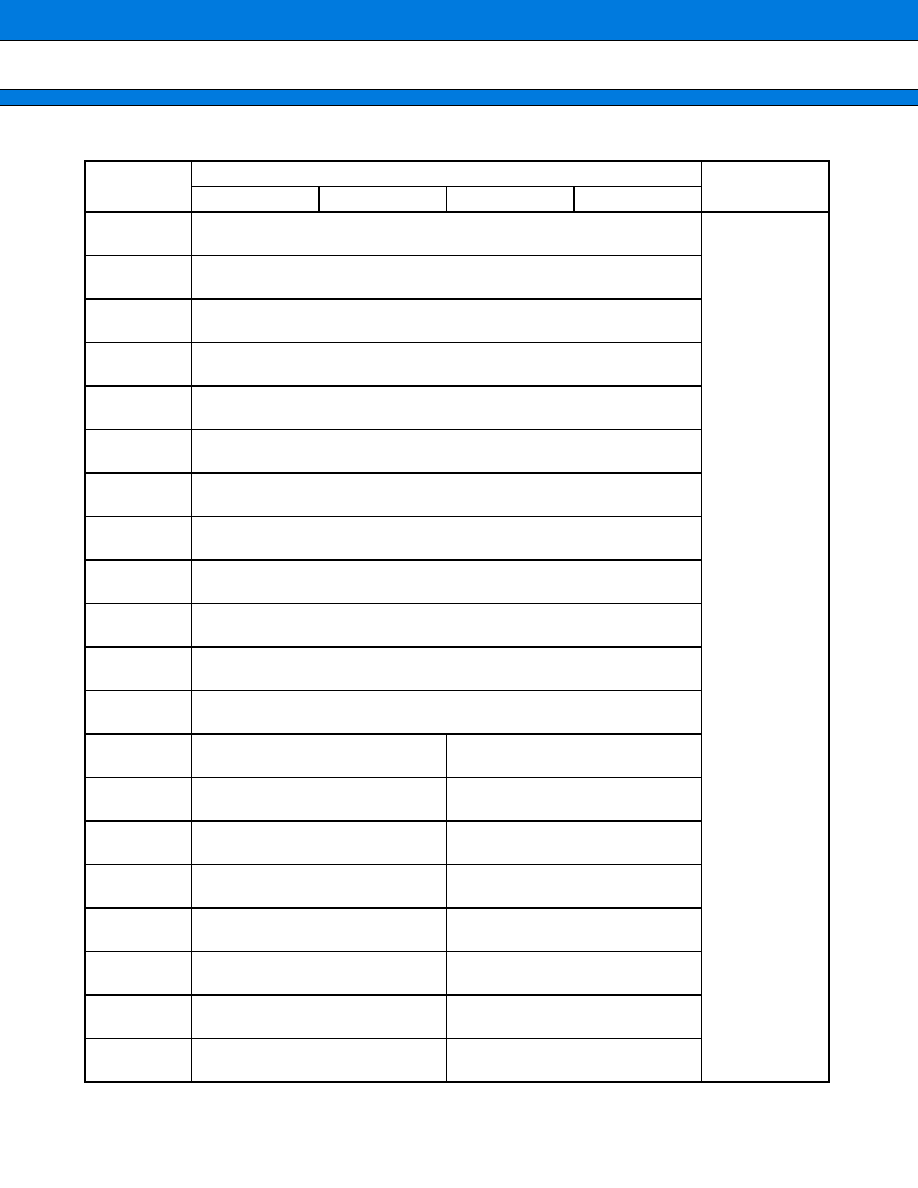

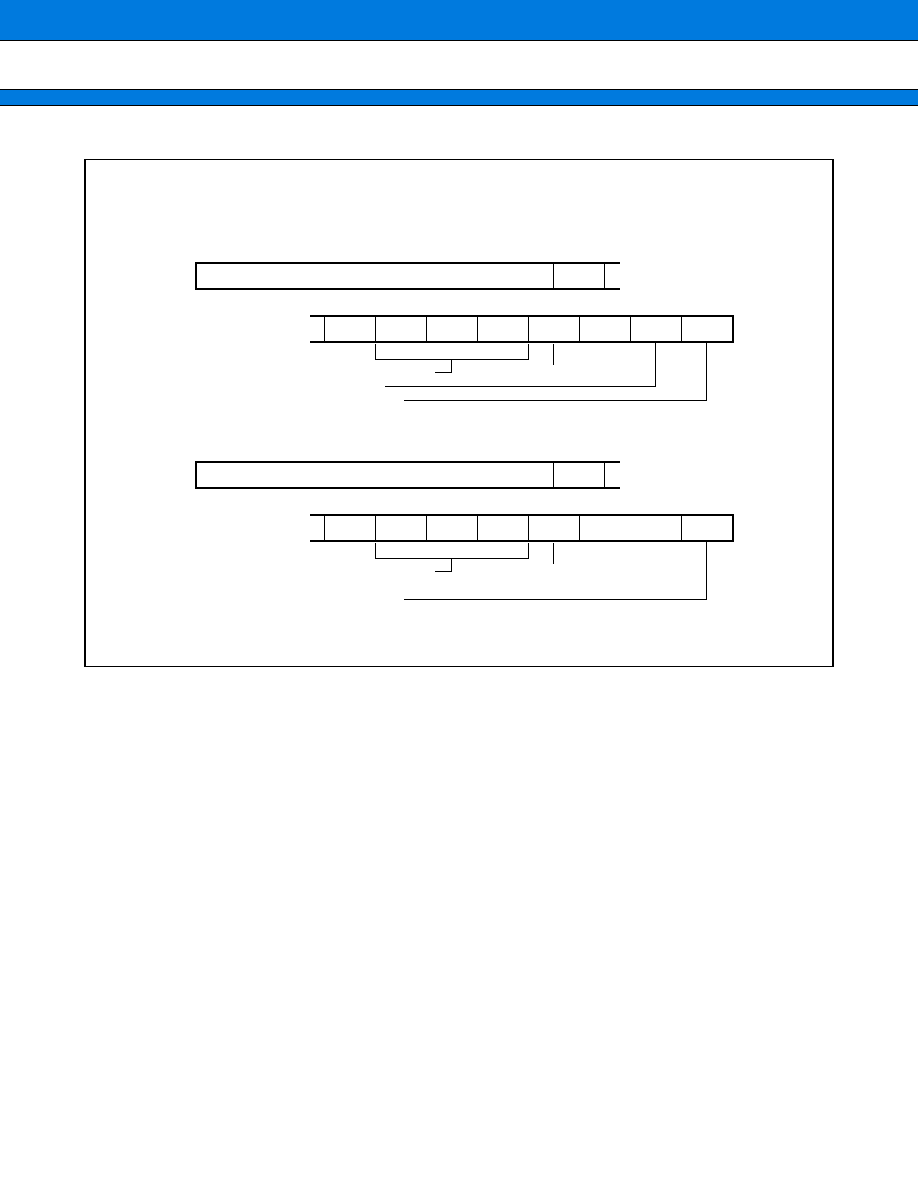

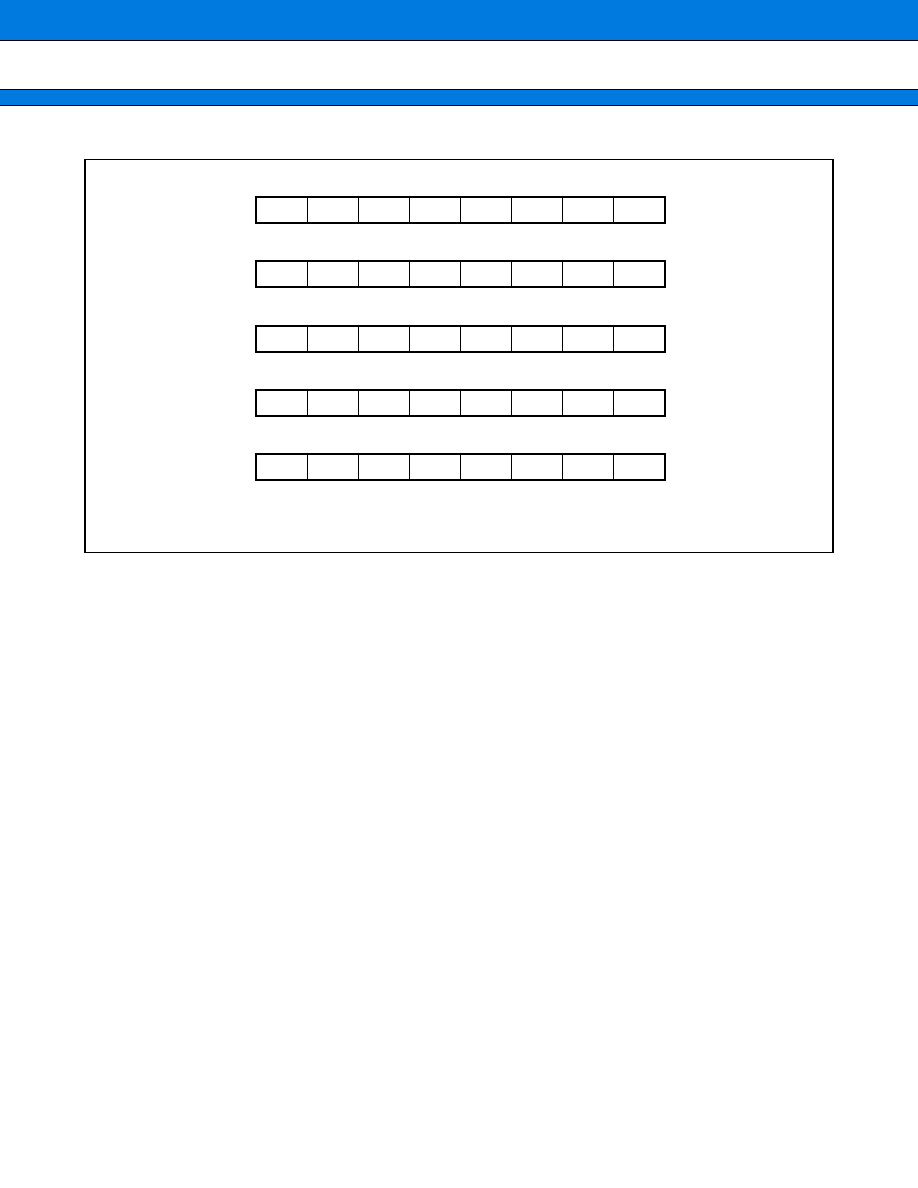

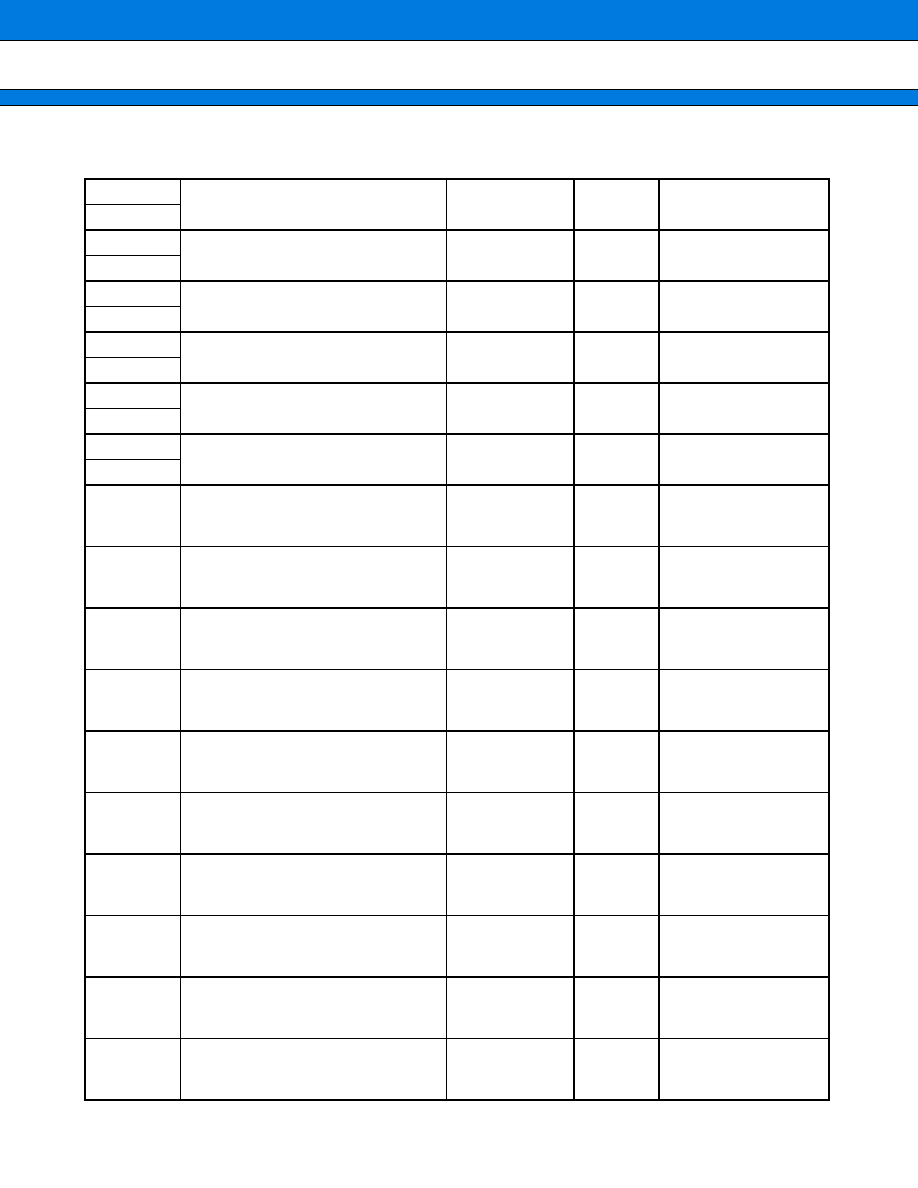

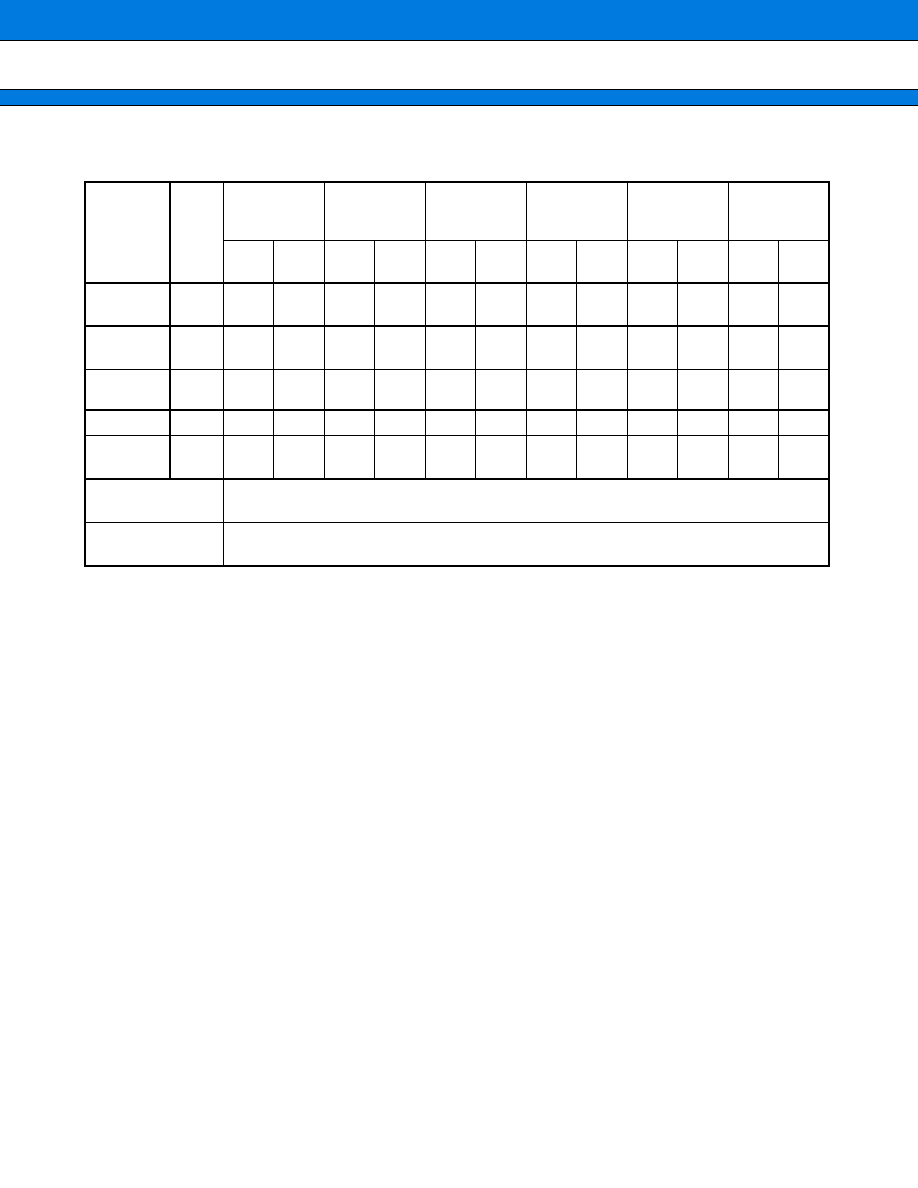

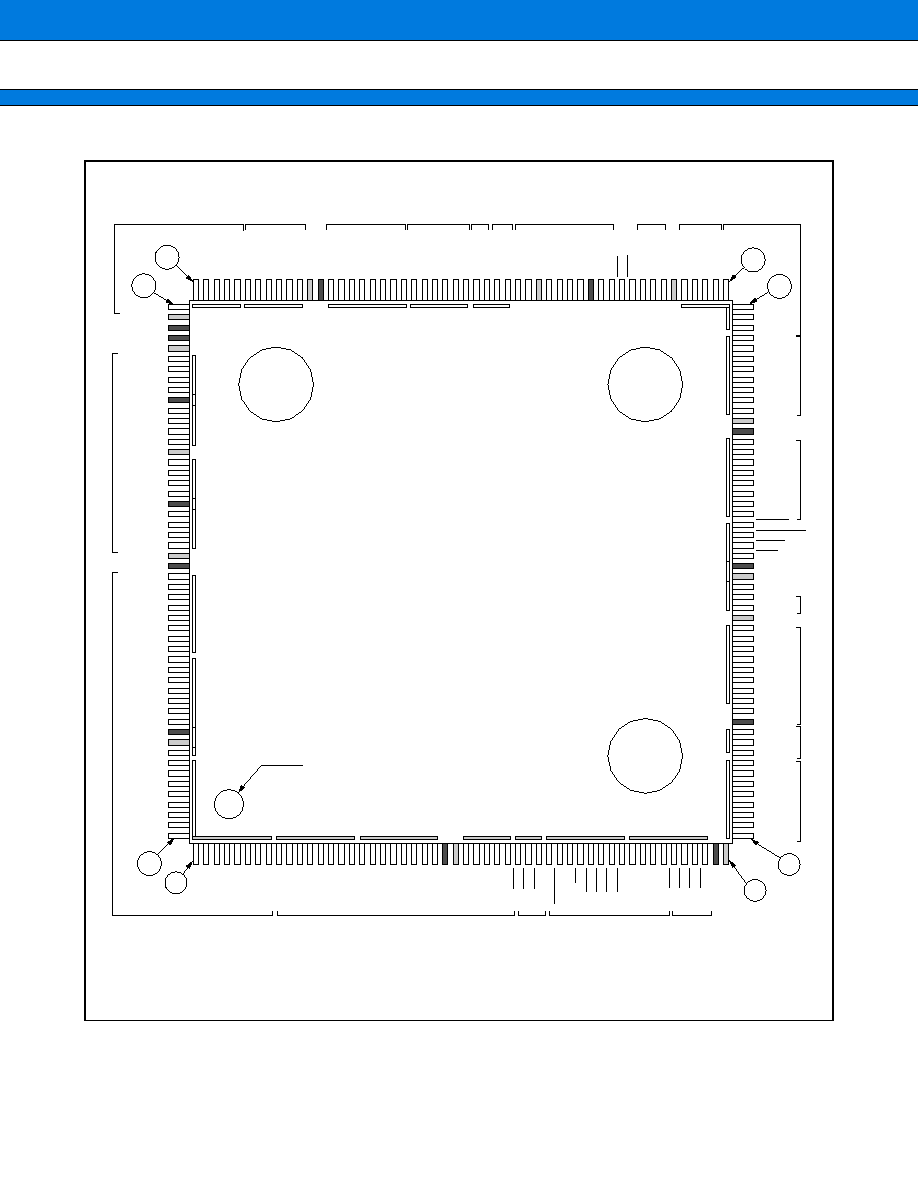

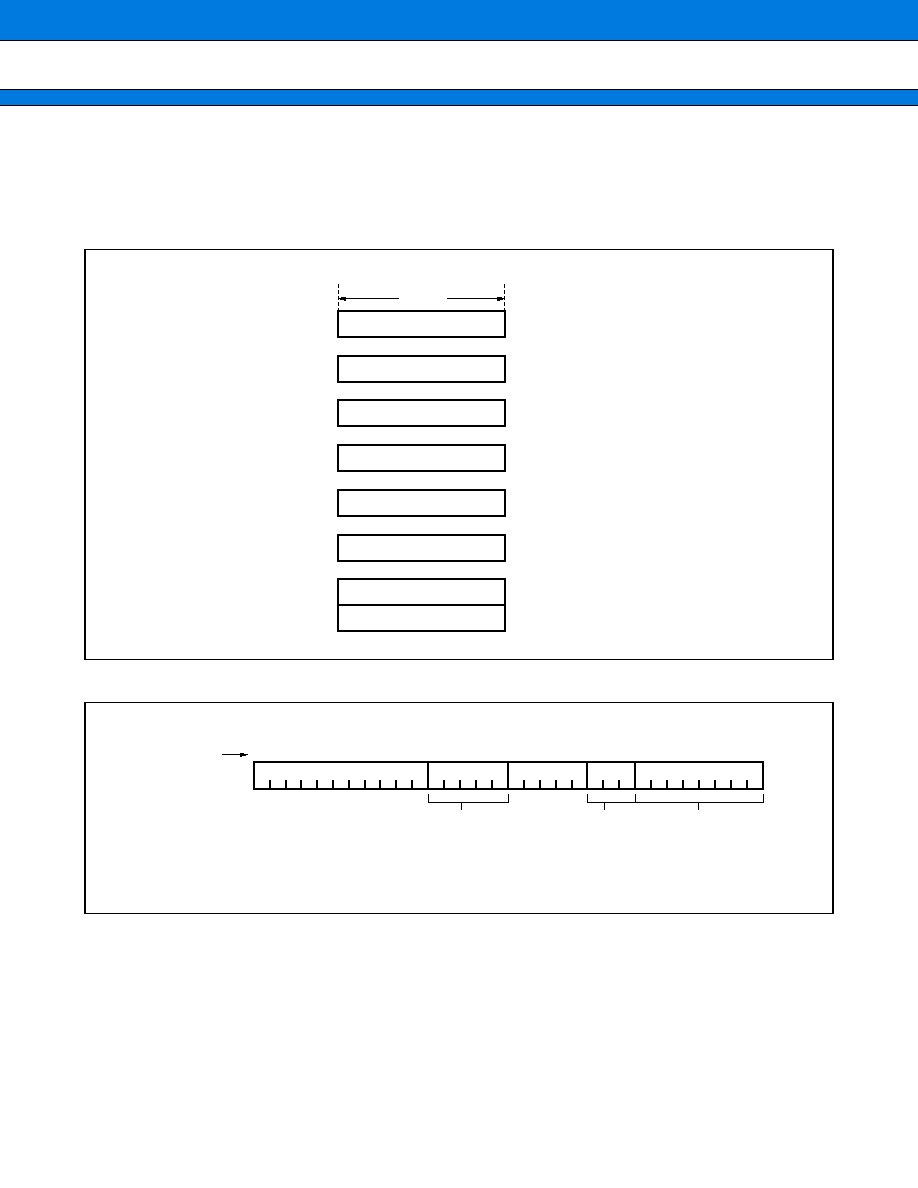

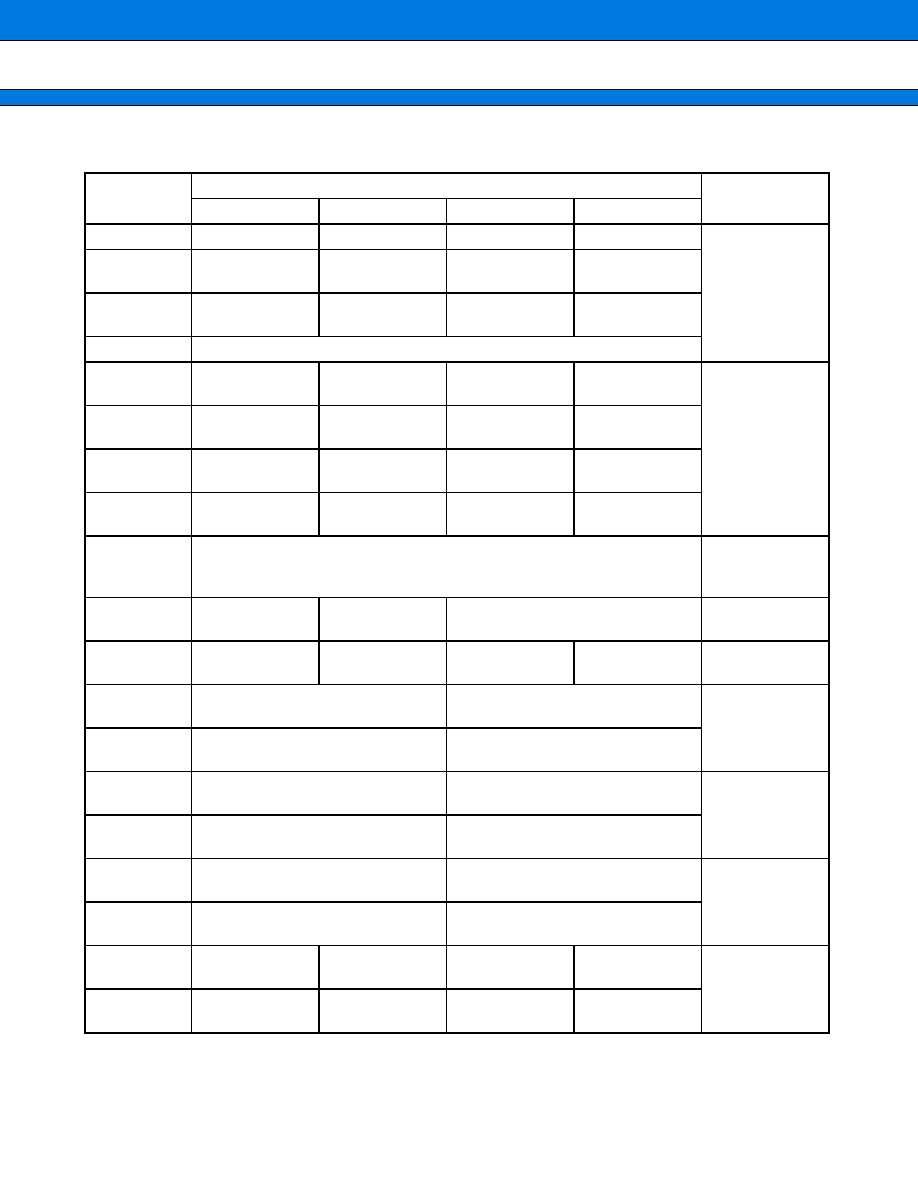

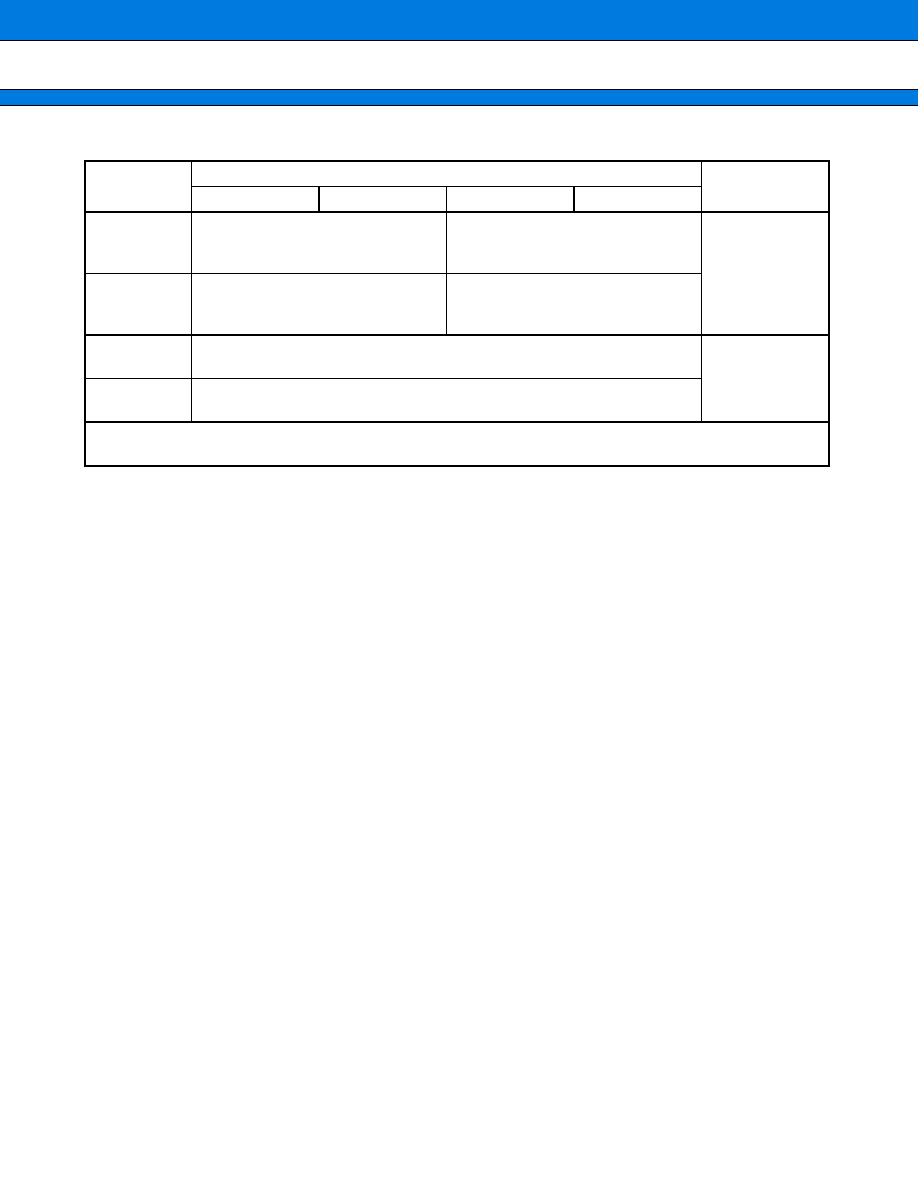

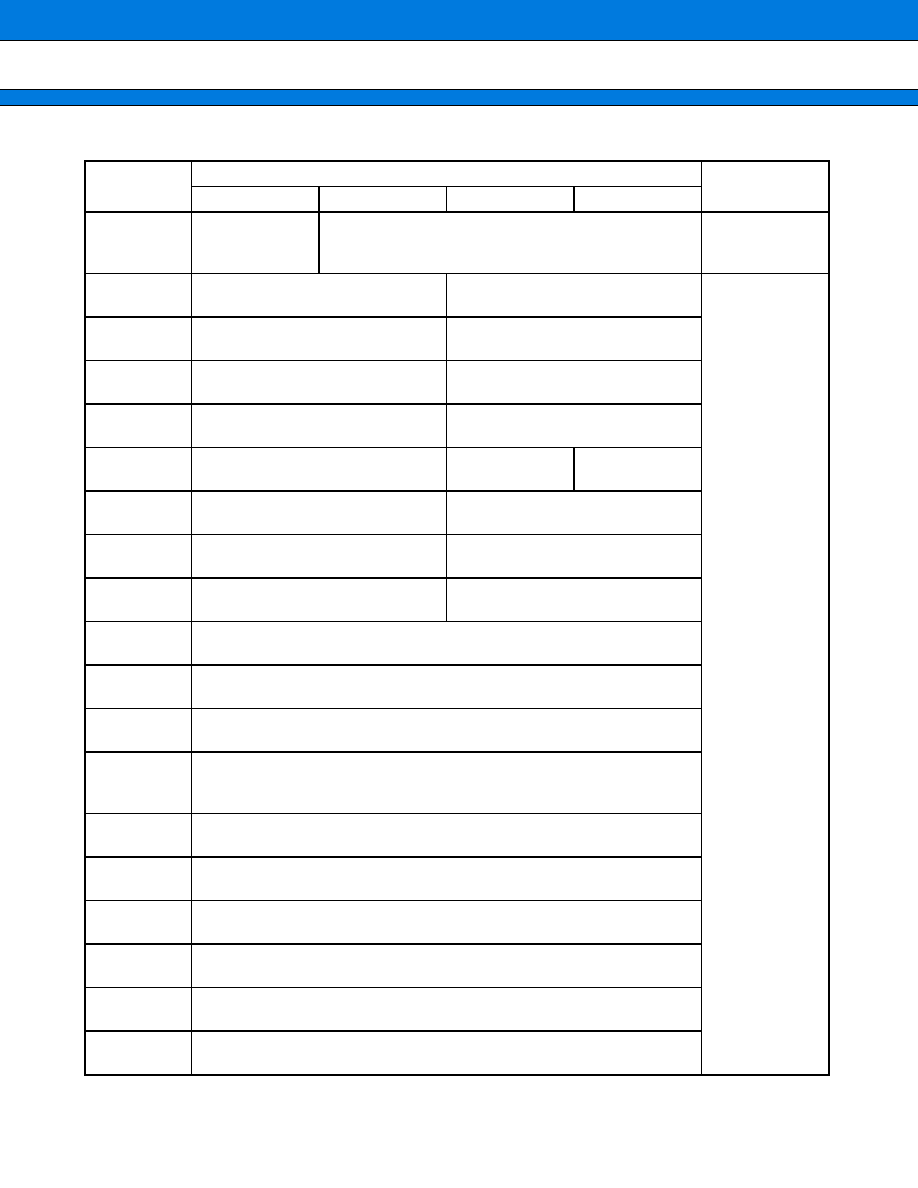

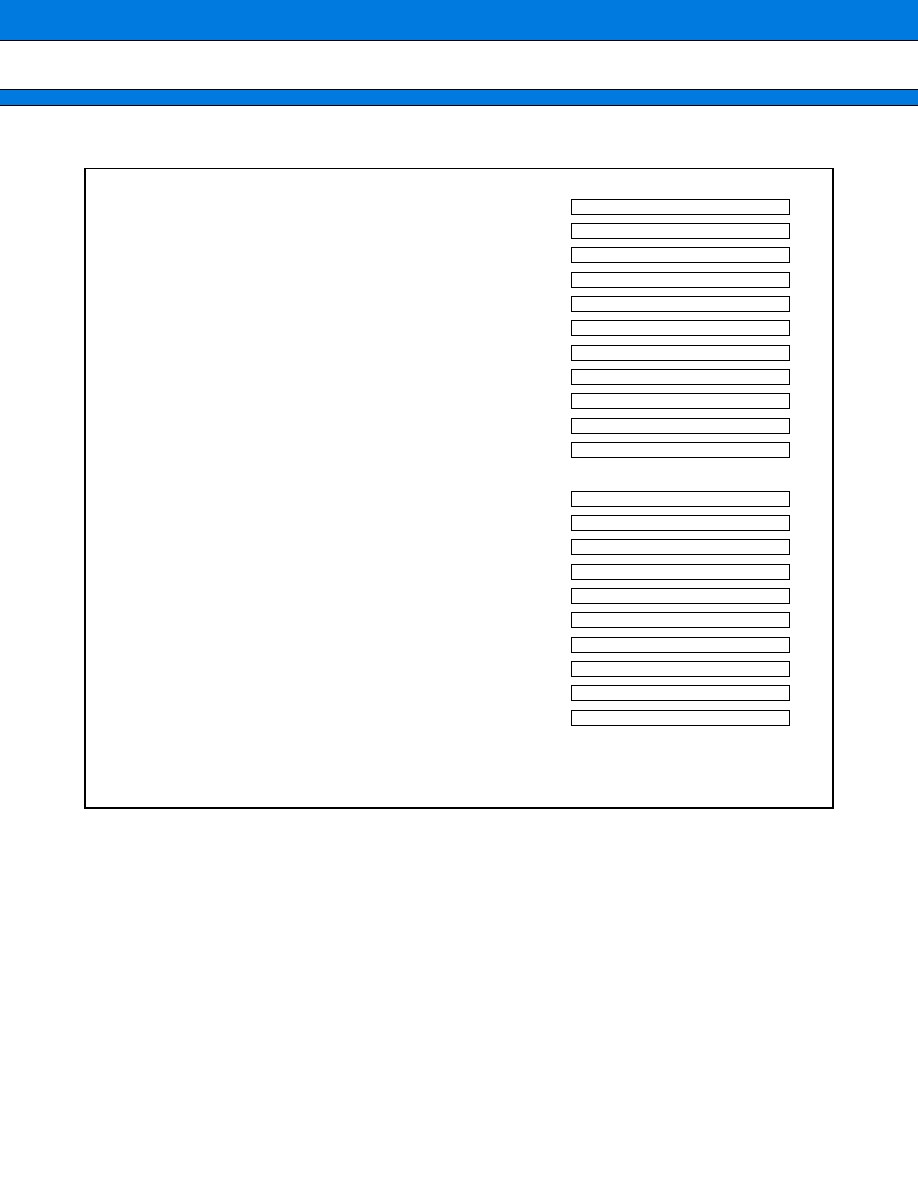

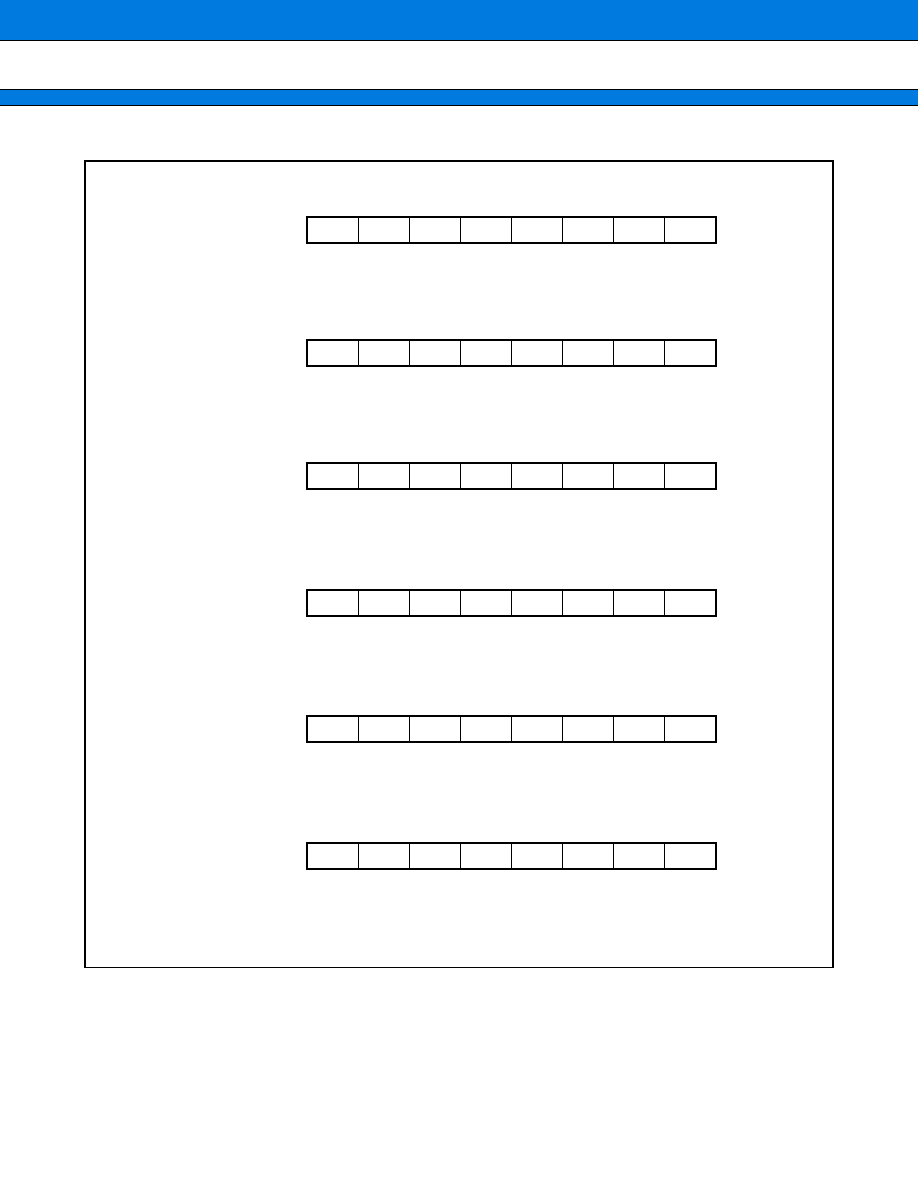

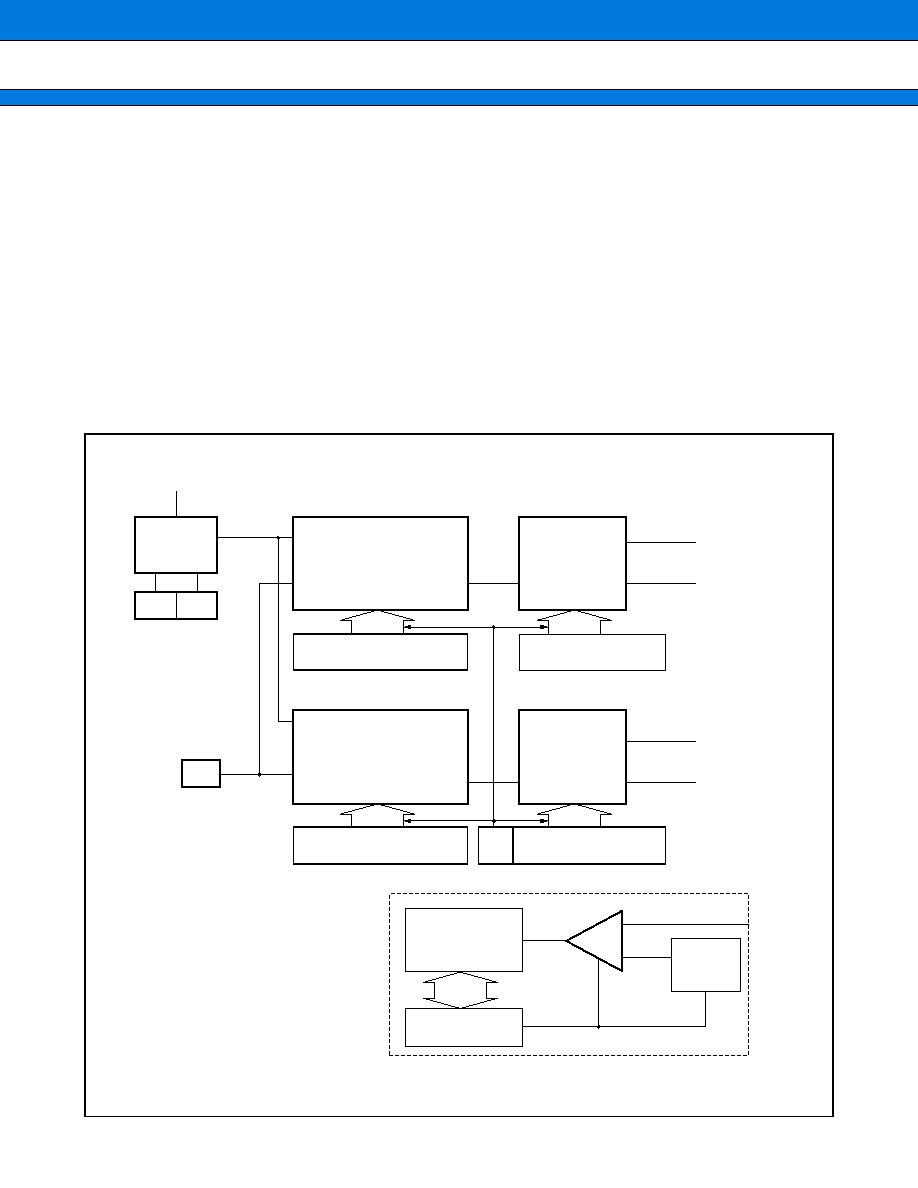

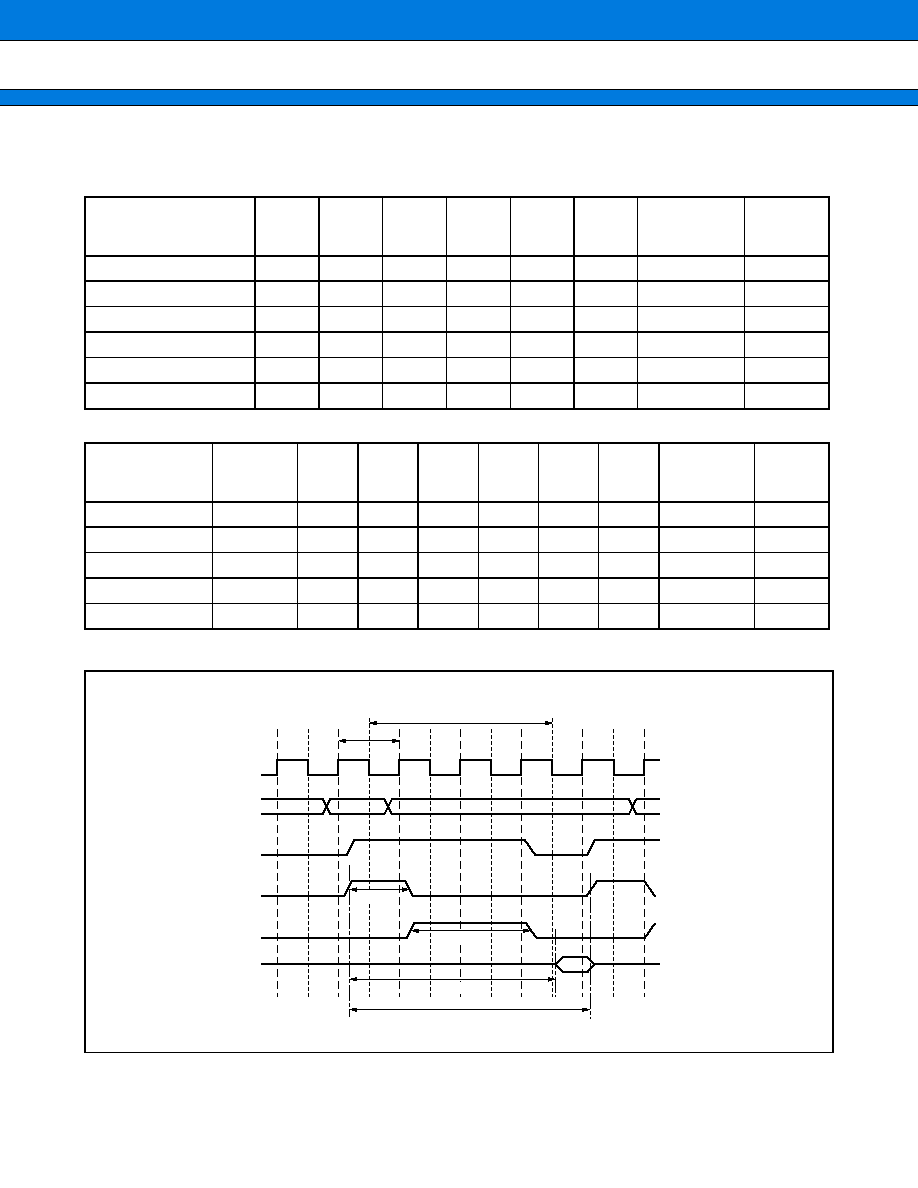

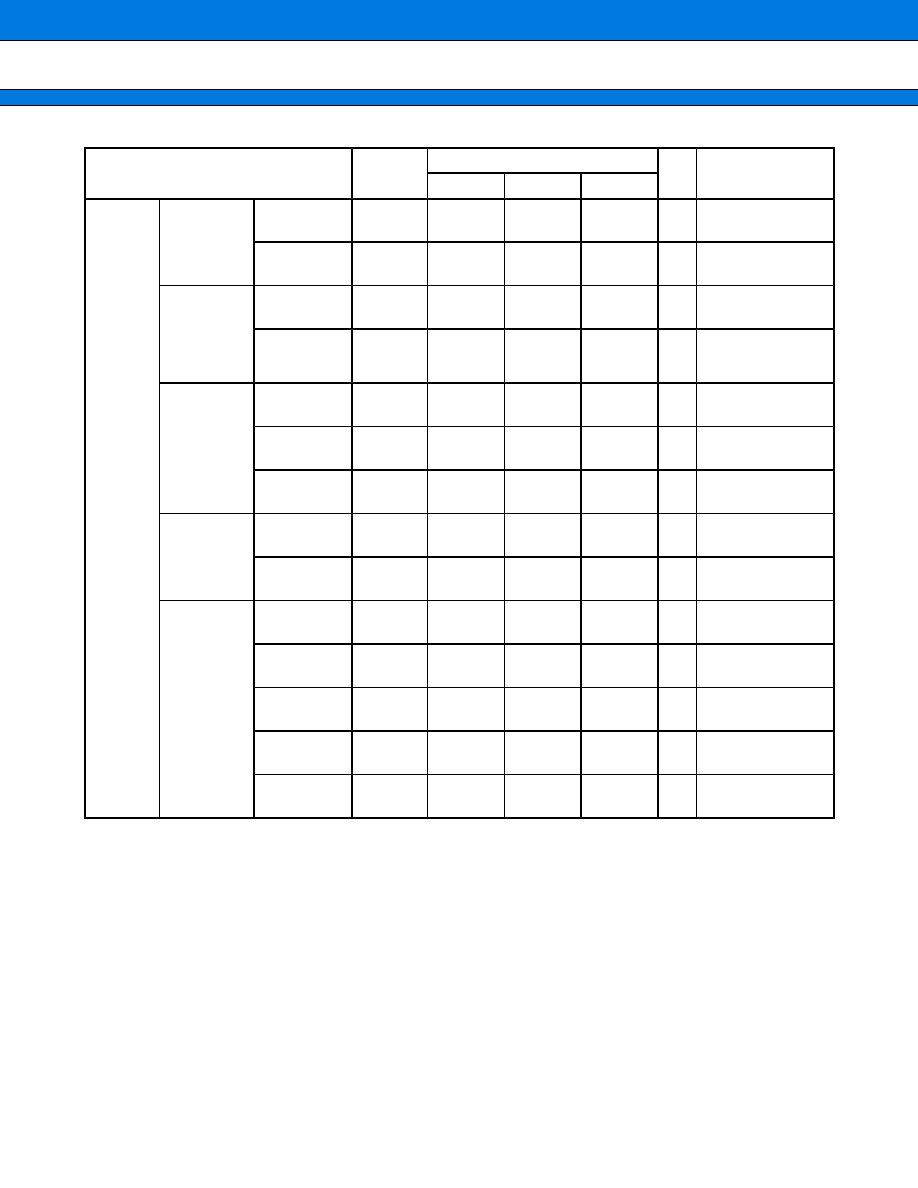

∑

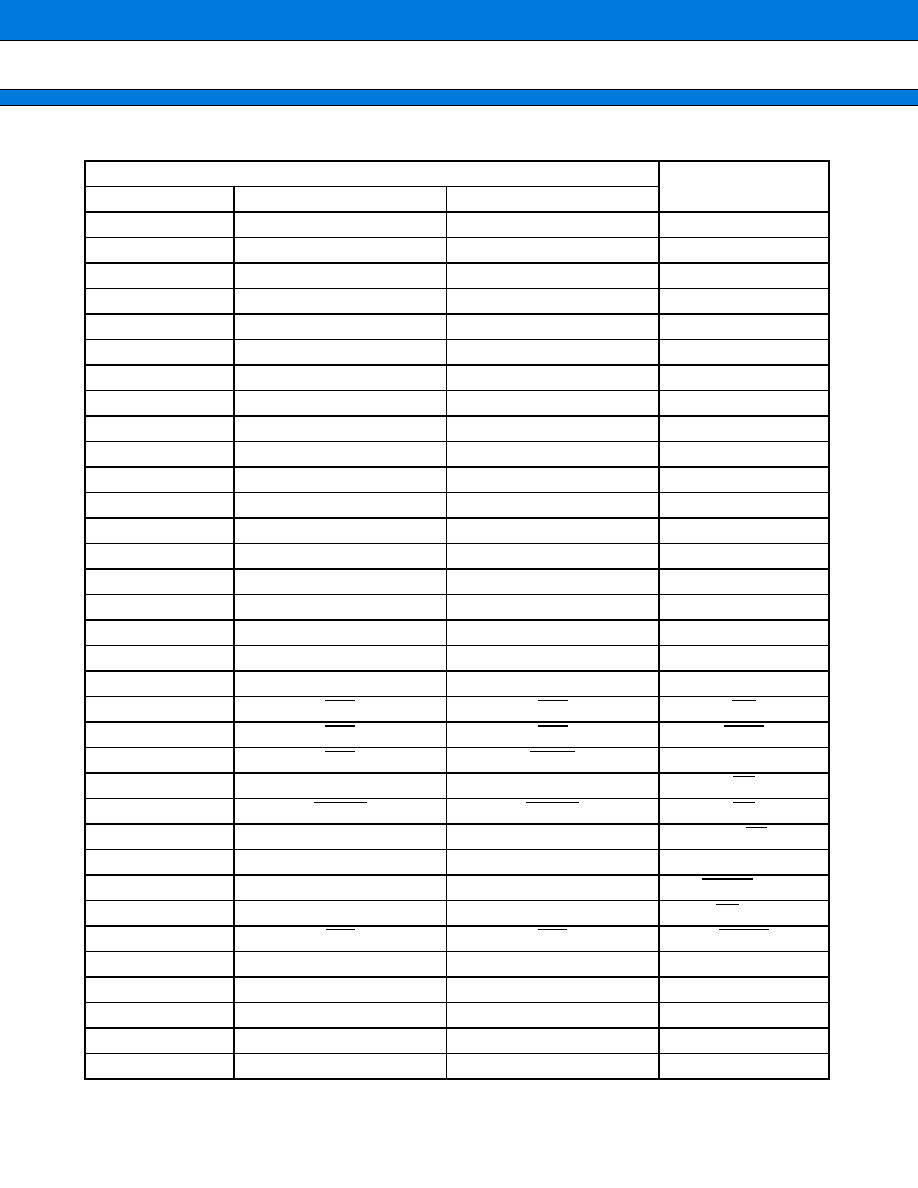

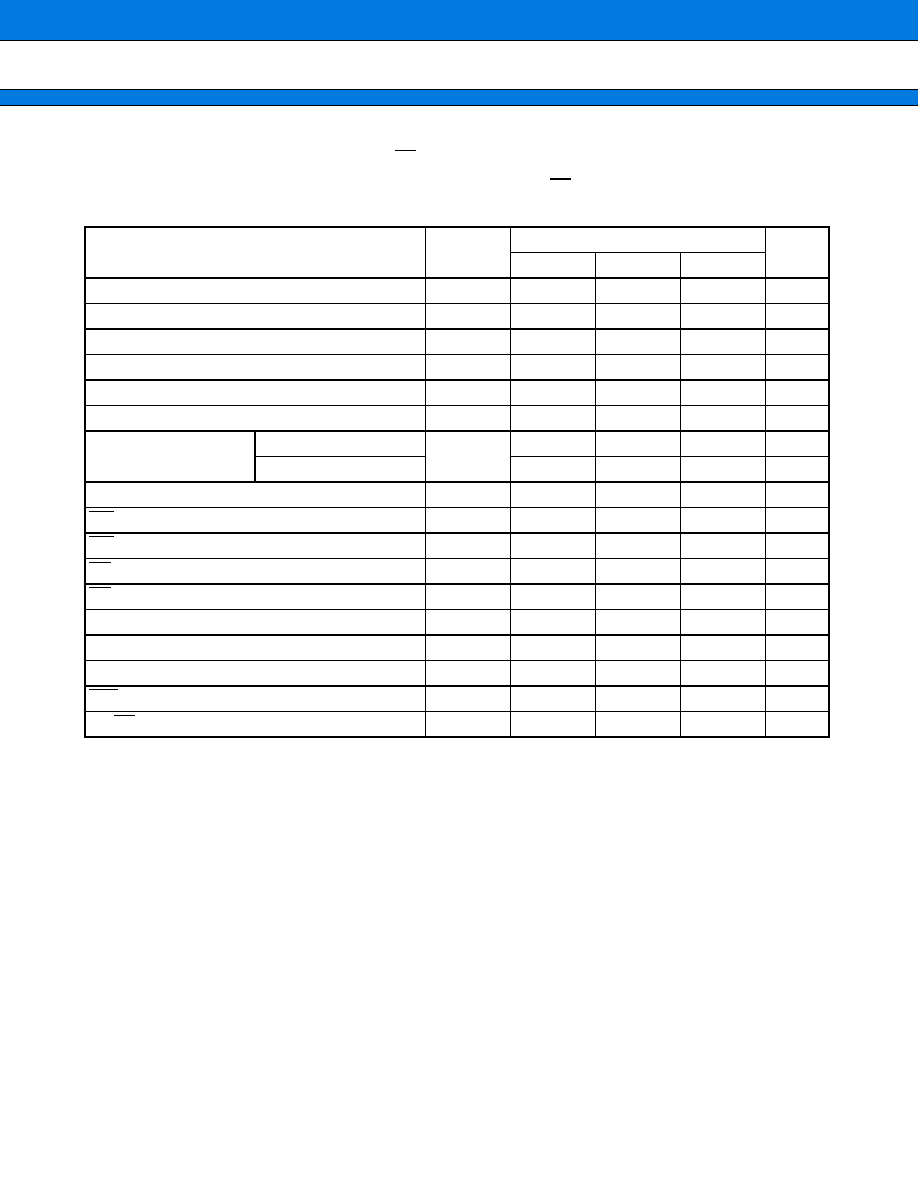

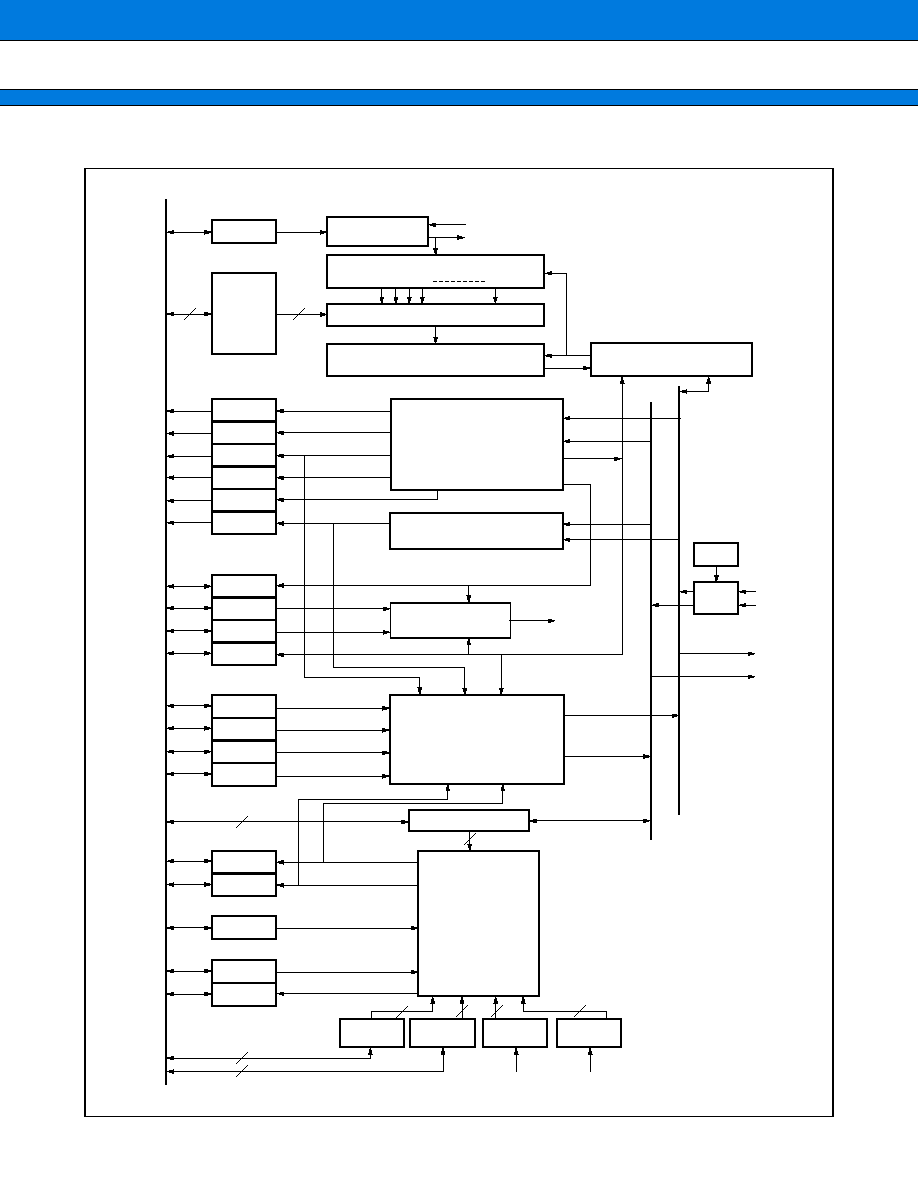

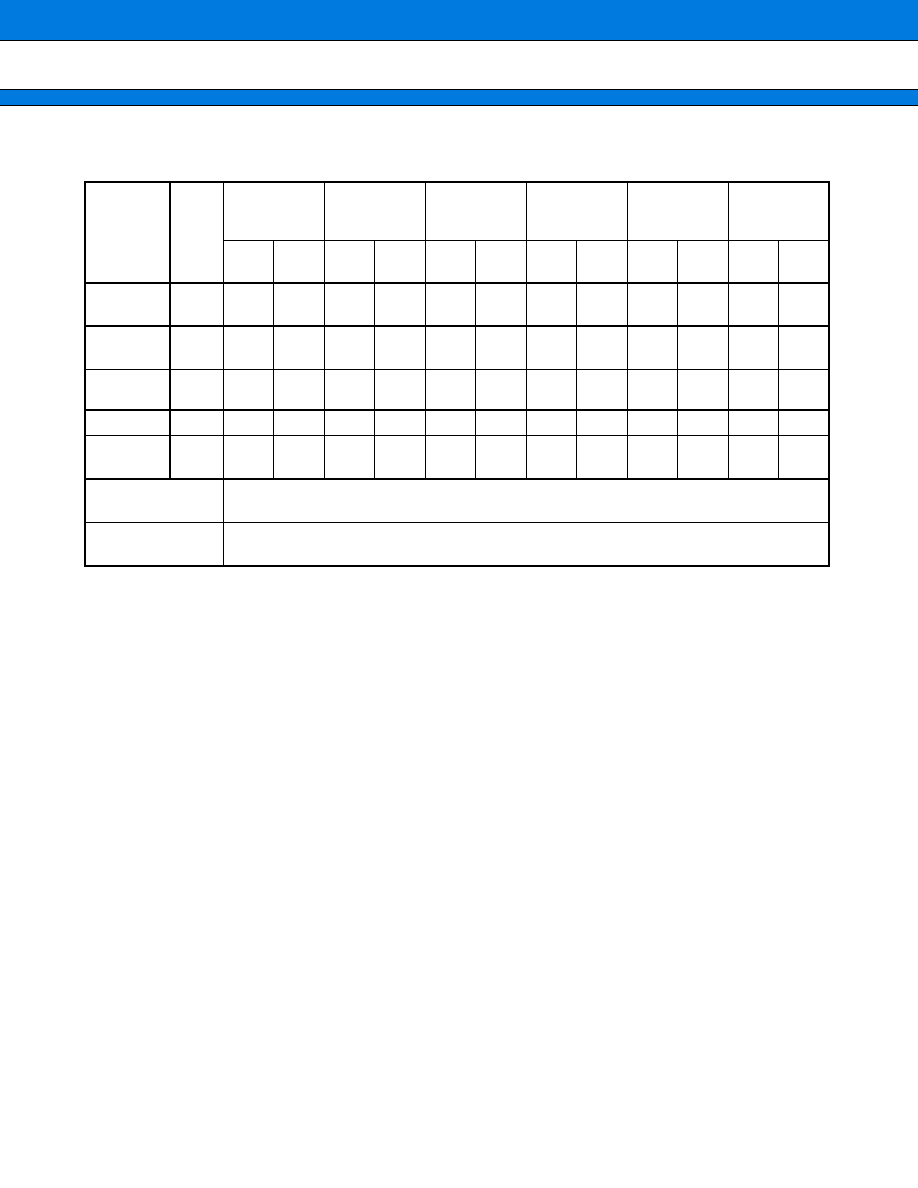

MB91F361GA/F362GA

(TOP VIEW)

(FPT-208P-M04)

,,,

,,,

,,,,

,,,

,,

,,,

156

157

UART

PQ [5:0]

PP [5:0]

PO [7:0]

PN [5:0] PM [3:0]

P9 [7:0]

P8 [7:0]

P7 [4:6]

P6 [4:0]

P5 [7:0]

P4 [7:0]

P3 [7:0]

P2 [7:0]

P1 [7:0]

P0 [7:0]

PS [7:0]

PR [7:0]

PL [7:0]

PK [7:0]

PJ [7:0]

PI [6:0]

PH [7:0]

PB [2:0]

PG [7:0]

CAN

PPG

SIO

I

2

C

XTAL

+

PLL

Mode

OCU

Sound

ICU

LED

DAC

ADC

DMA

ADC

ext. Int.

53

52

Chip

Select

Chip

Select

ext. Bus Control

ext. Bus Address

ext. Bus Data

1

208

INDEX

SMC

105

104

SIN2

SOT1

SIN1

SOT0

SIN0

RX2

TX2

RX1

TX1

RX0

TX0

V

SS

V

DD

OCPA7

OCPA6

OCPA5

OCPA4

OCPA3

OCPA2

OCPA1

OCPA0

SCK3

SOT3

SIN3

SCK4

SIN4

SOT4

SCL

SDA

SGA

SGO

VCI

CPO

V

SS

X1A

X0A

X1

X0

V

DD

SELCLK

MONCLK

INIT

HST

MD2

MD1

MD0

V

SS

OUT3

OUT2

OUT1

OUT0

IN3

D24

D25

D26

D27

D28

D29

D30

D31

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

V

DD

V

SS

A16

A17

A18

A19

A20

CS4

CS5

CS6

RDY

BGRNT

BRQ

RD

WR0

WR1

WR2

WR3

AS

ALE

CLK

AH/BOOT

CS0

CS1

CS2

CS3

V

DD

V

SS

IN2

IN1

IN0

INT7

INT6

INT5

INT4

INT3

INT2

INT1

INT0

V

SS

V

DD

LED7

LED6

LED5

LED4

LED3

LED2

LED1

LED0

LTEST

CPUTEST

TEST

ATG

V

DD

V

SS

ALARM

DA1

DA0

AV

SS

AN7

AN6

AN5

AN4

AN3

AN2

AN1

AN0

AVRH

AV

CC

DEOP0

DACK0

DREQ0

AN15

AN14

AN13

AN12

AN11

AN10

AN9

AN8

SOT2

V

SS

V

CC

3C

V

DD

HV

SS

PWM1P0

PWM1M0

PWM2P0

PWM2M0

HV

DD

PWM1P1

PWM1M1

PWM2P1

PWM2M1

HV

SS

PWM1P2

PWM1M2

PWM2P2

PWM2M2

HV

DD

PWM1P3

PWM1M3

PWM2P3

PWM2M3

HV

SS

V

DD

D0

D1

D2

D3

D4

D5

D6

D7

D8

D9

D10

D11

D12

D13

D14

V

DD

V

SS

D15

D16

D17

D18

D19

D20

D21

D22

D23

MB91360G Series

6

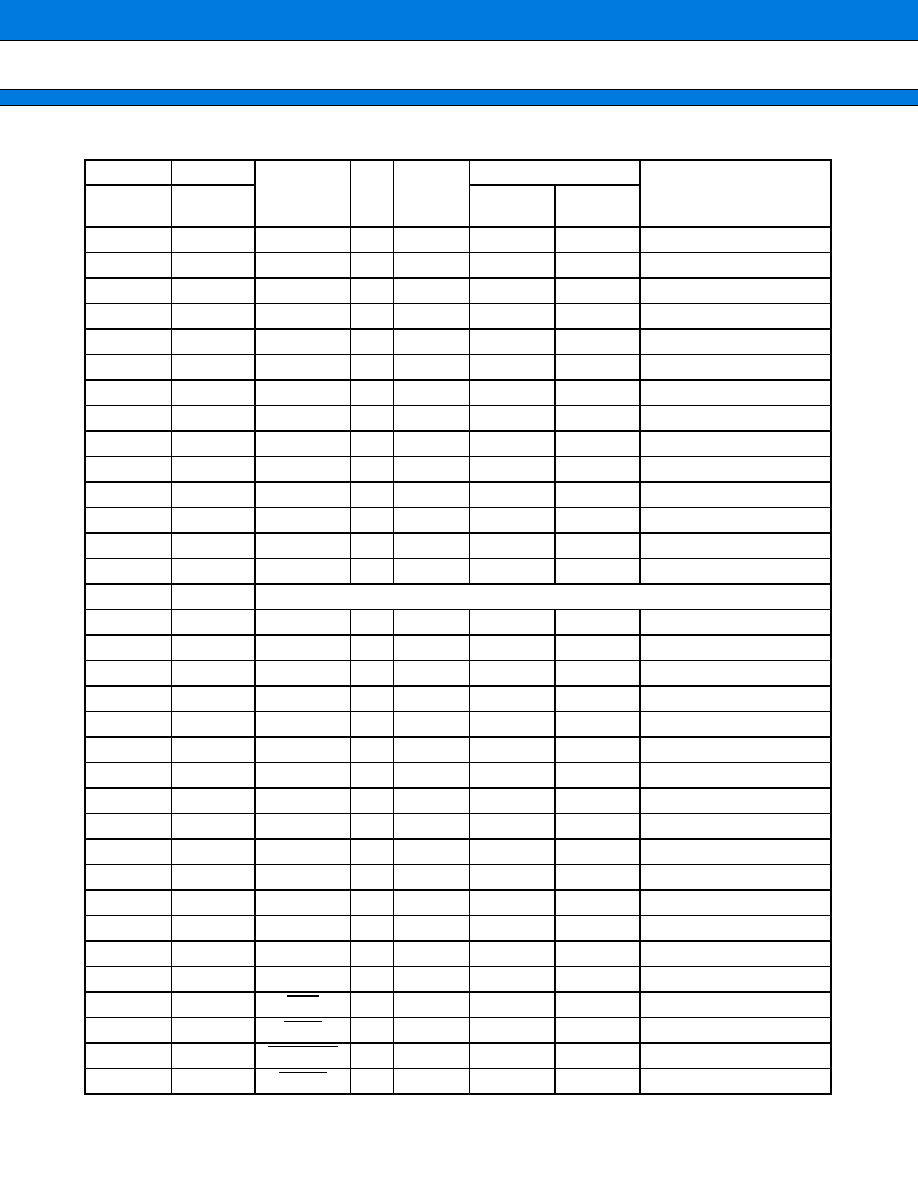

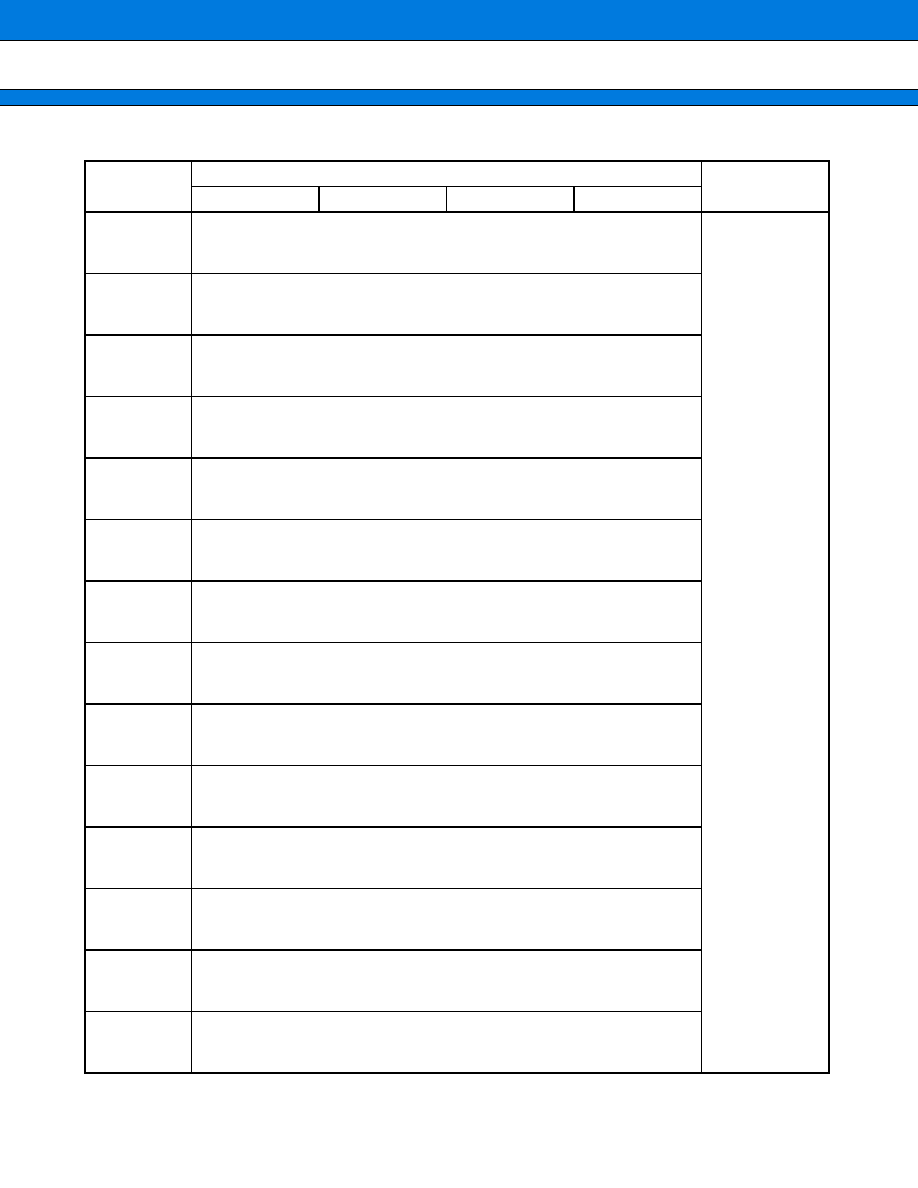

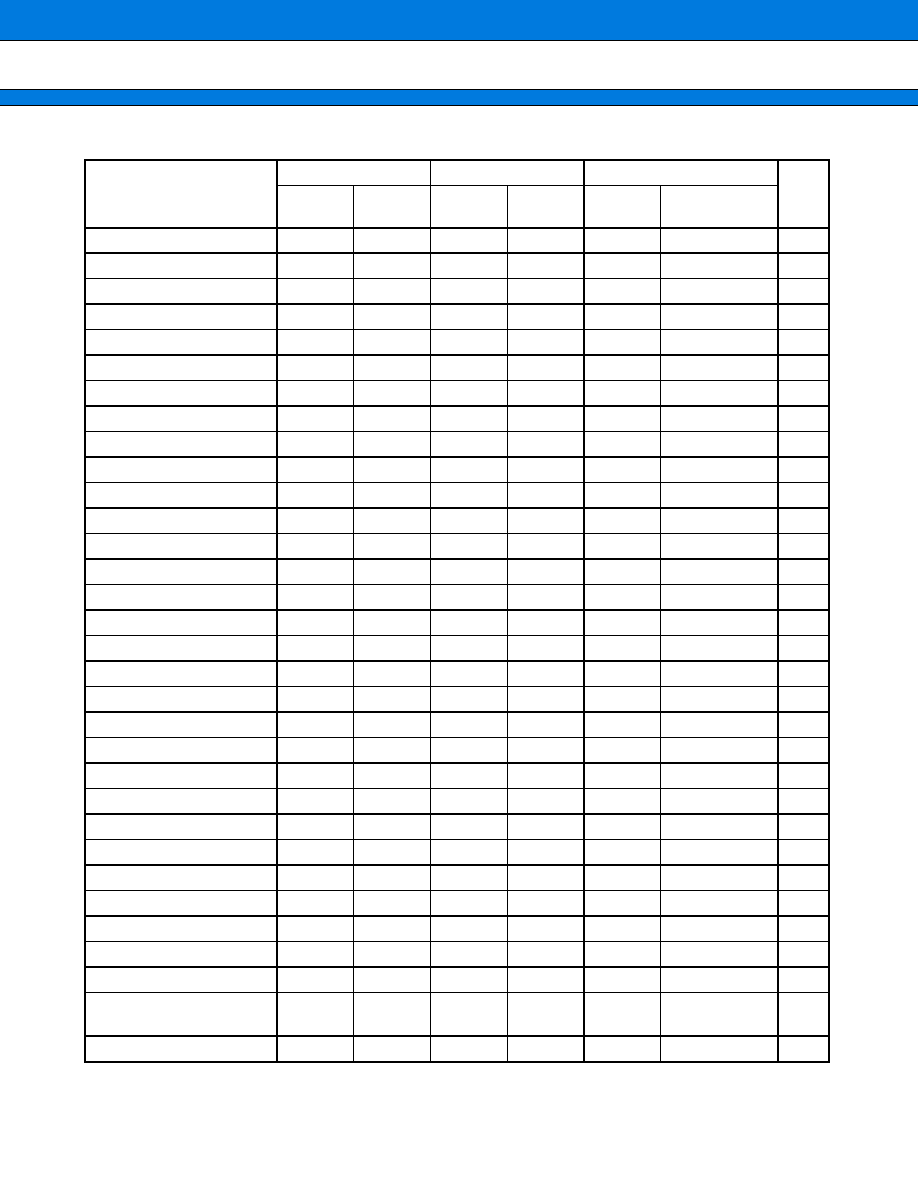

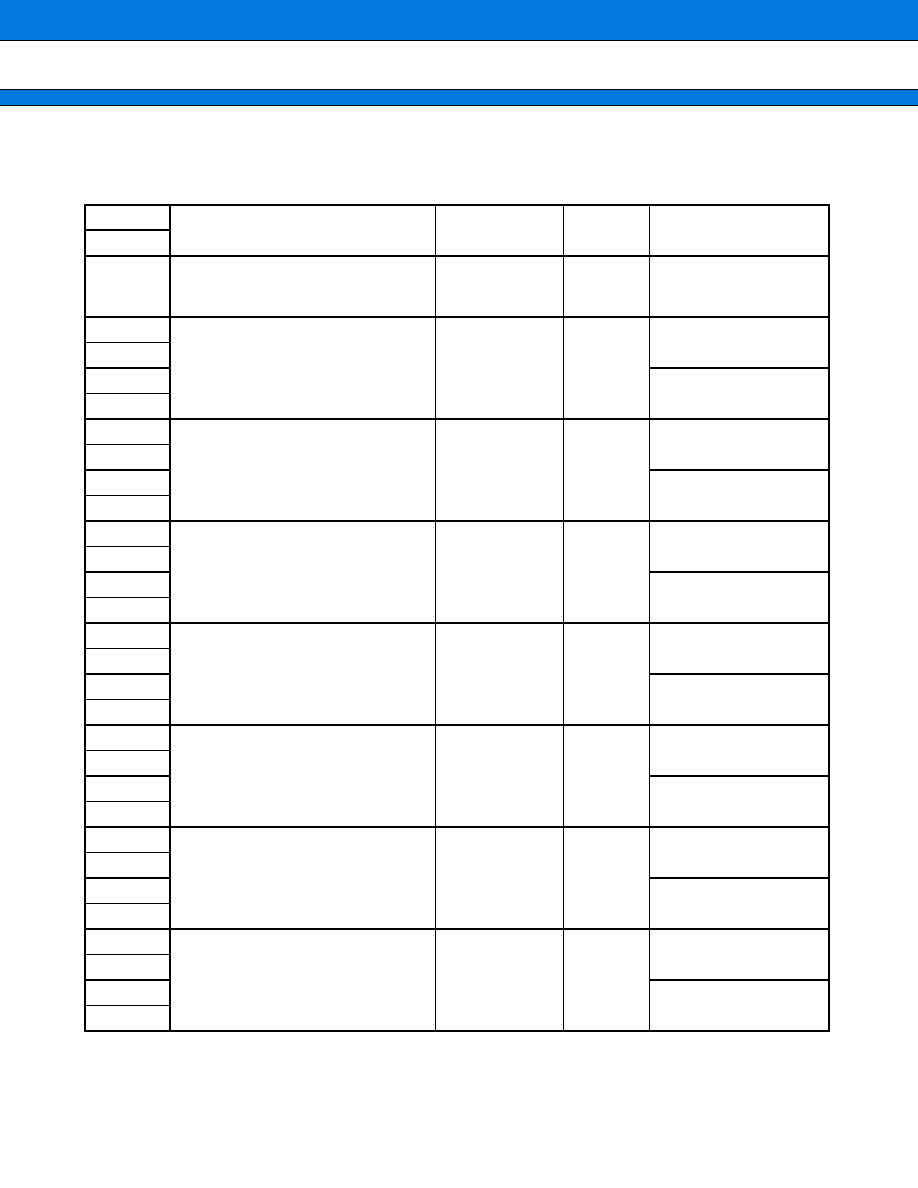

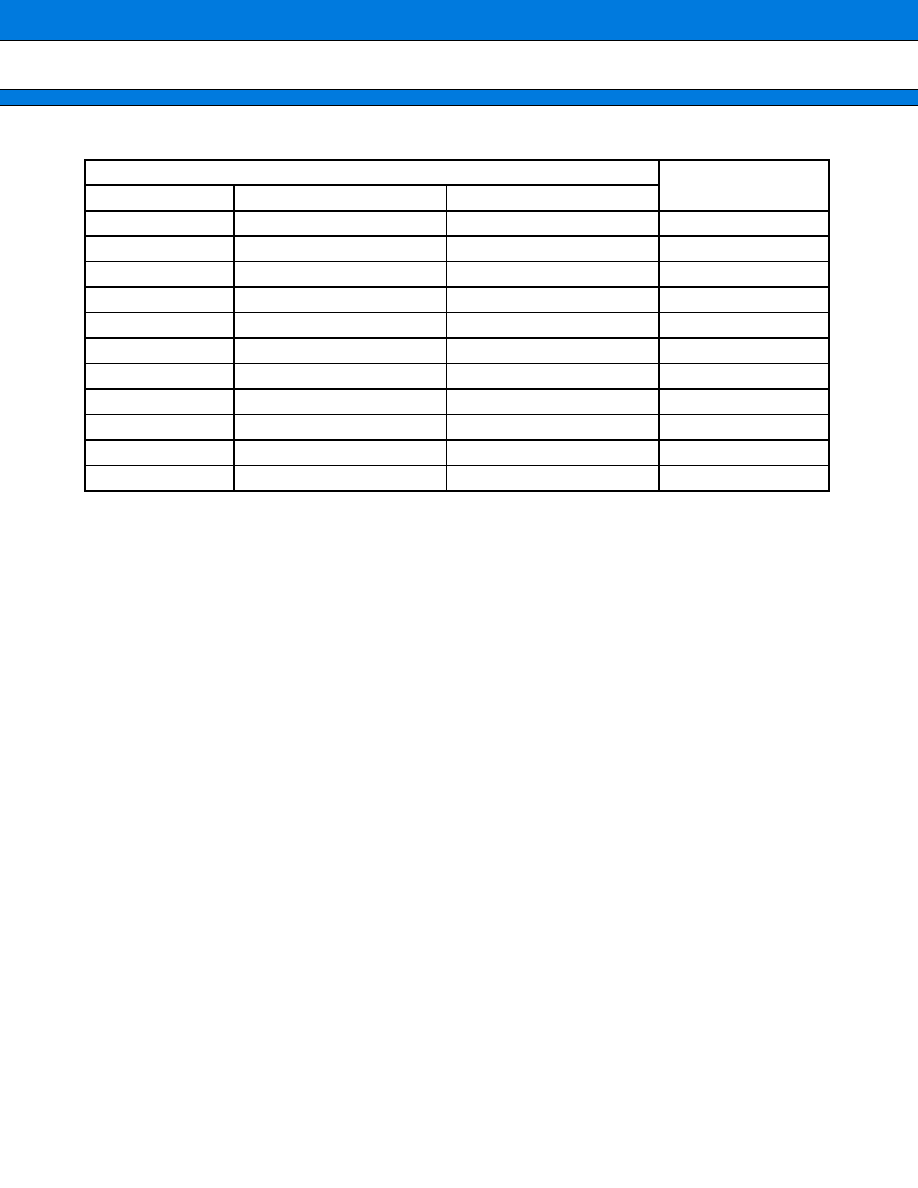

s

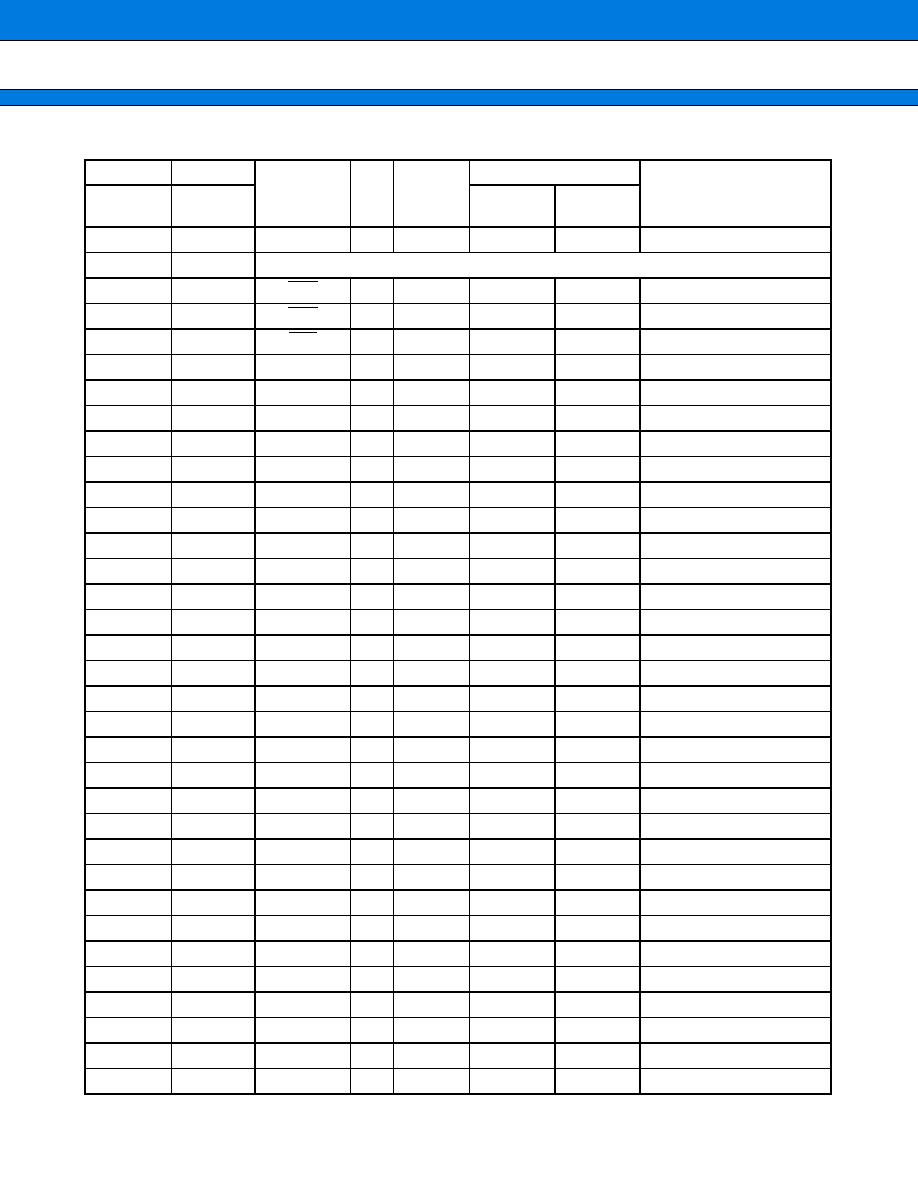

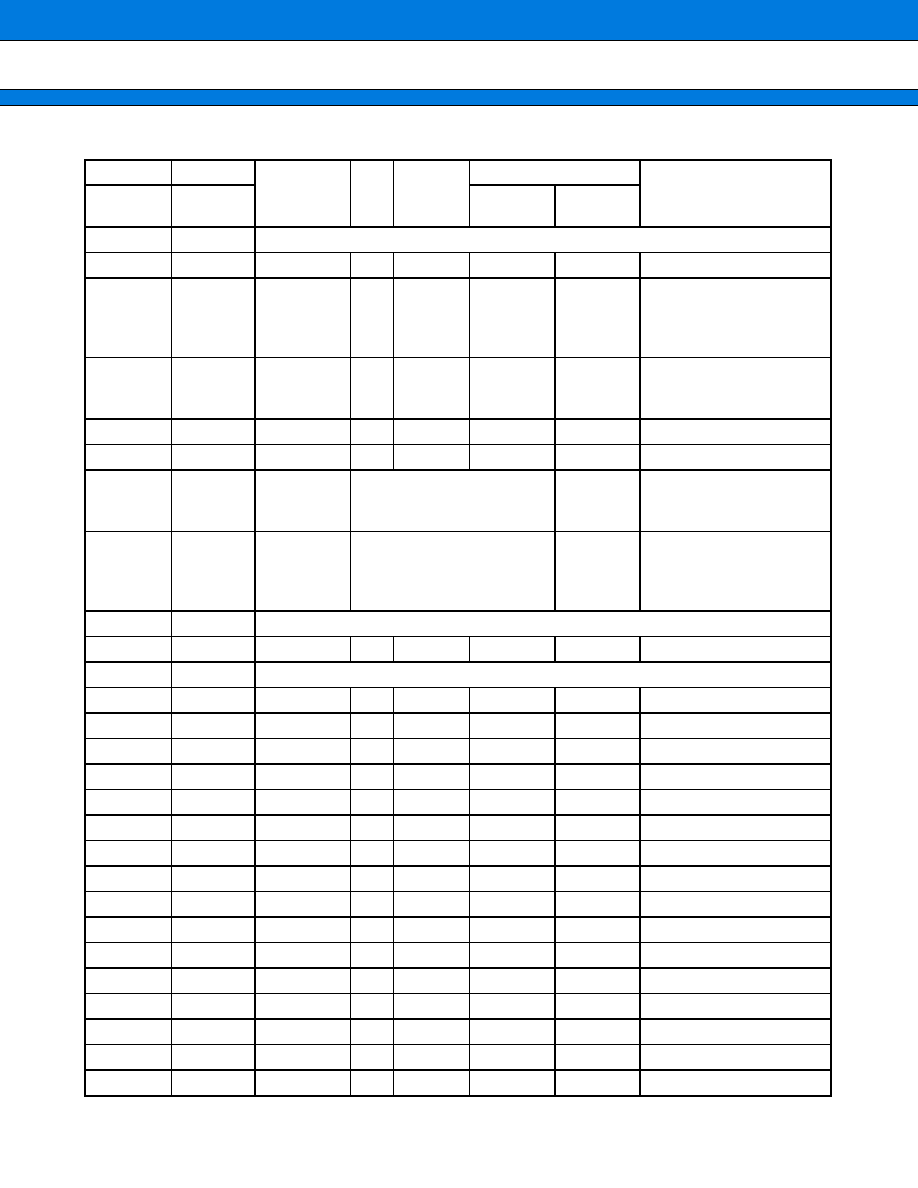

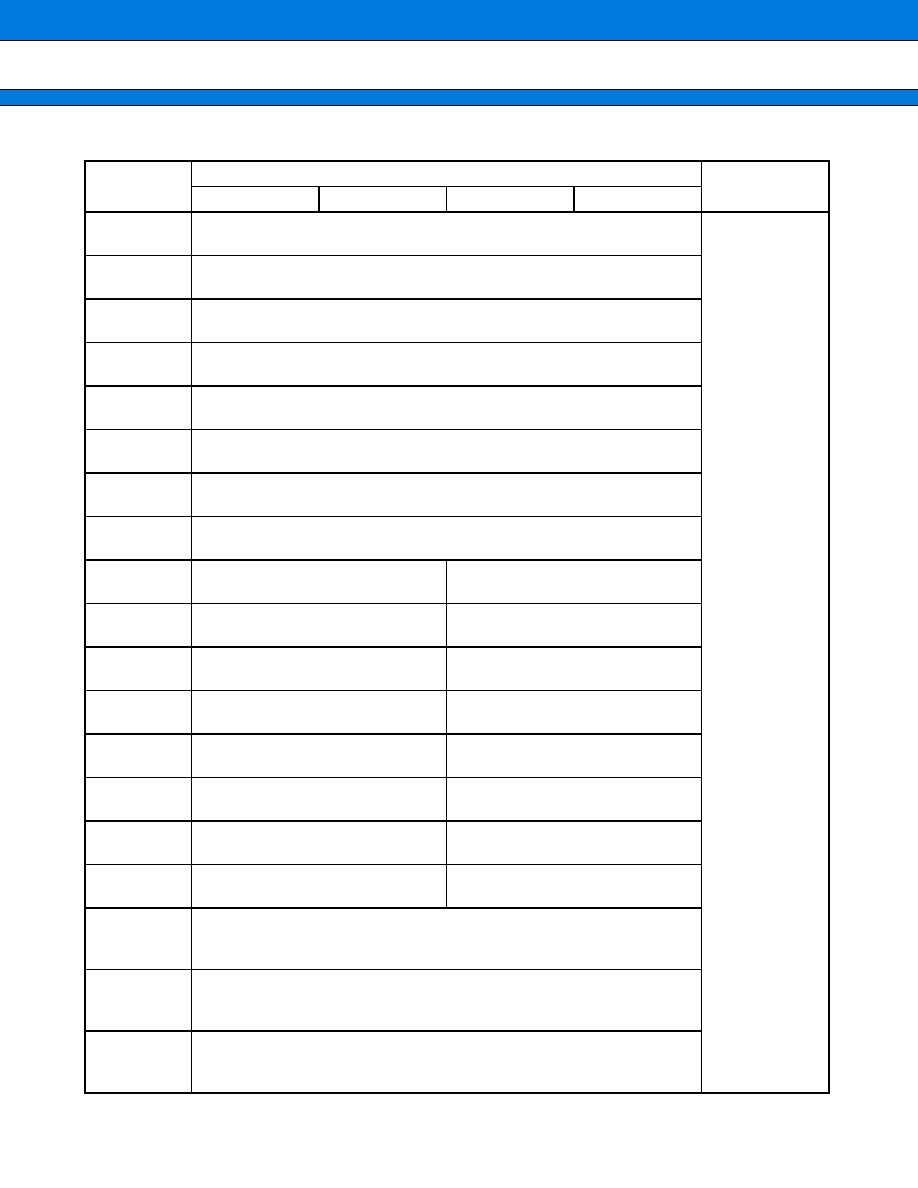

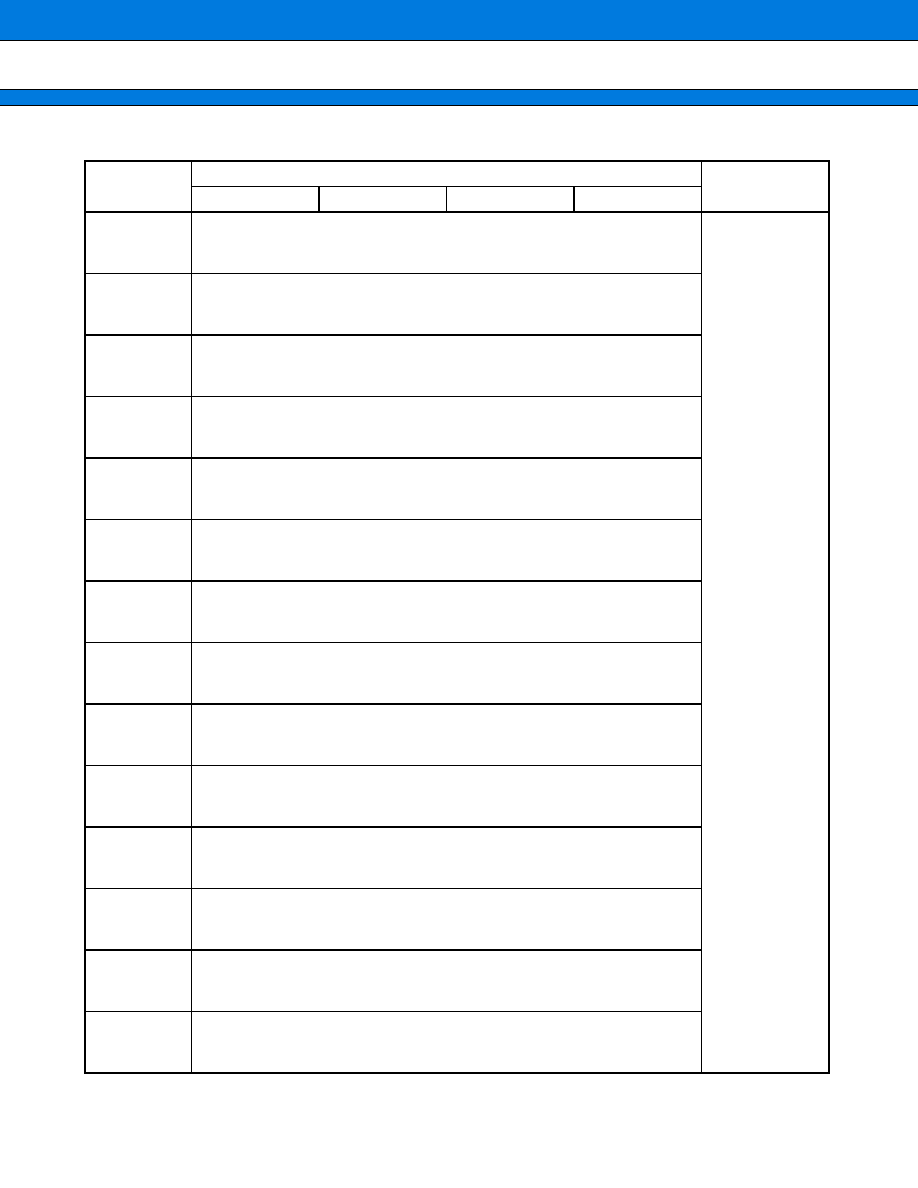

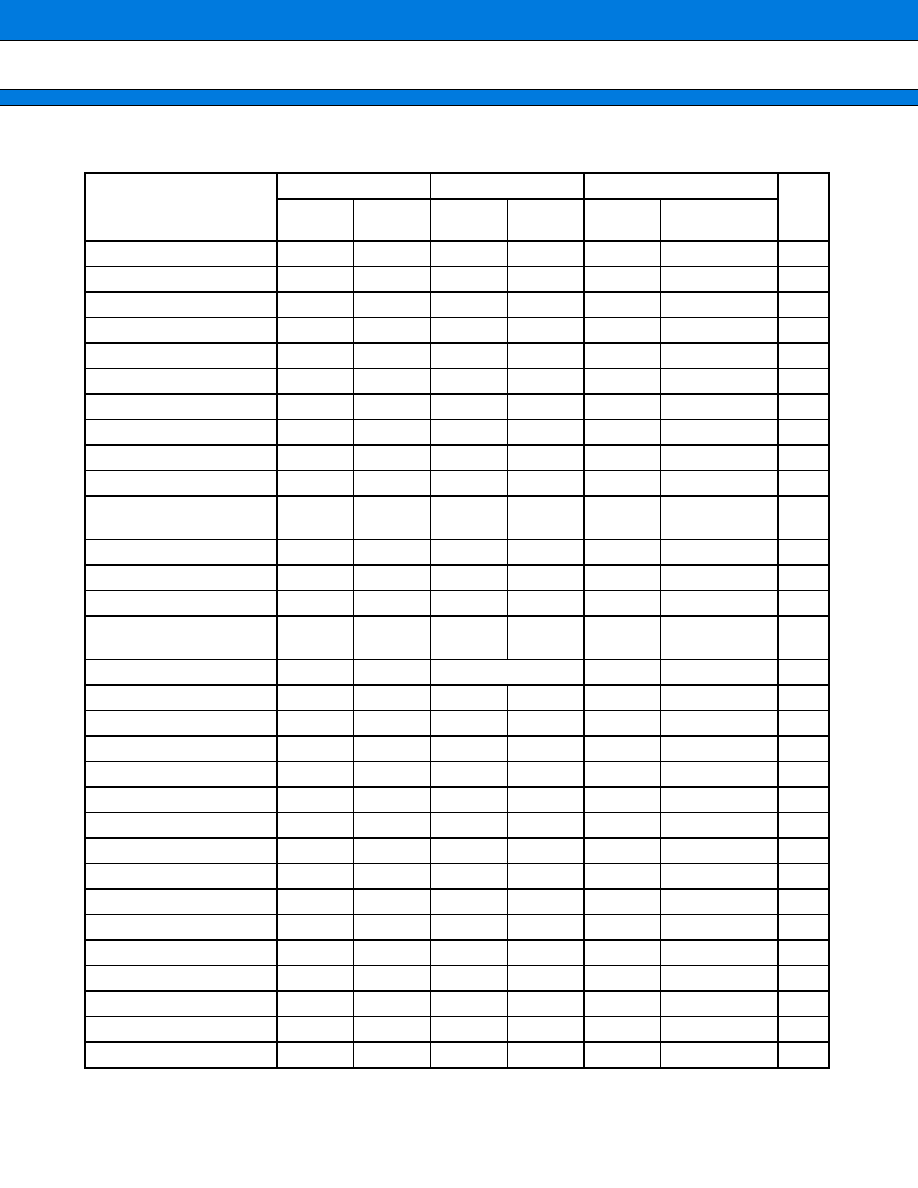

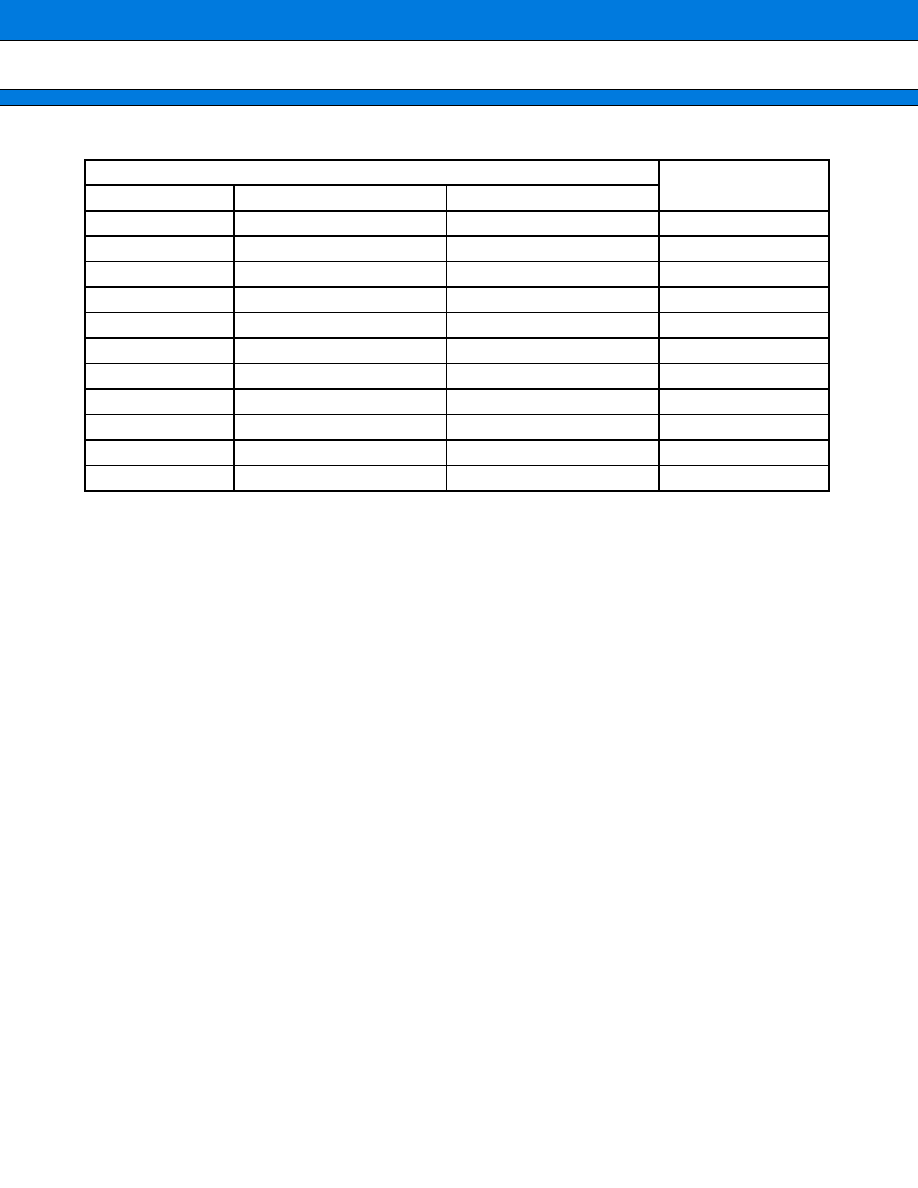

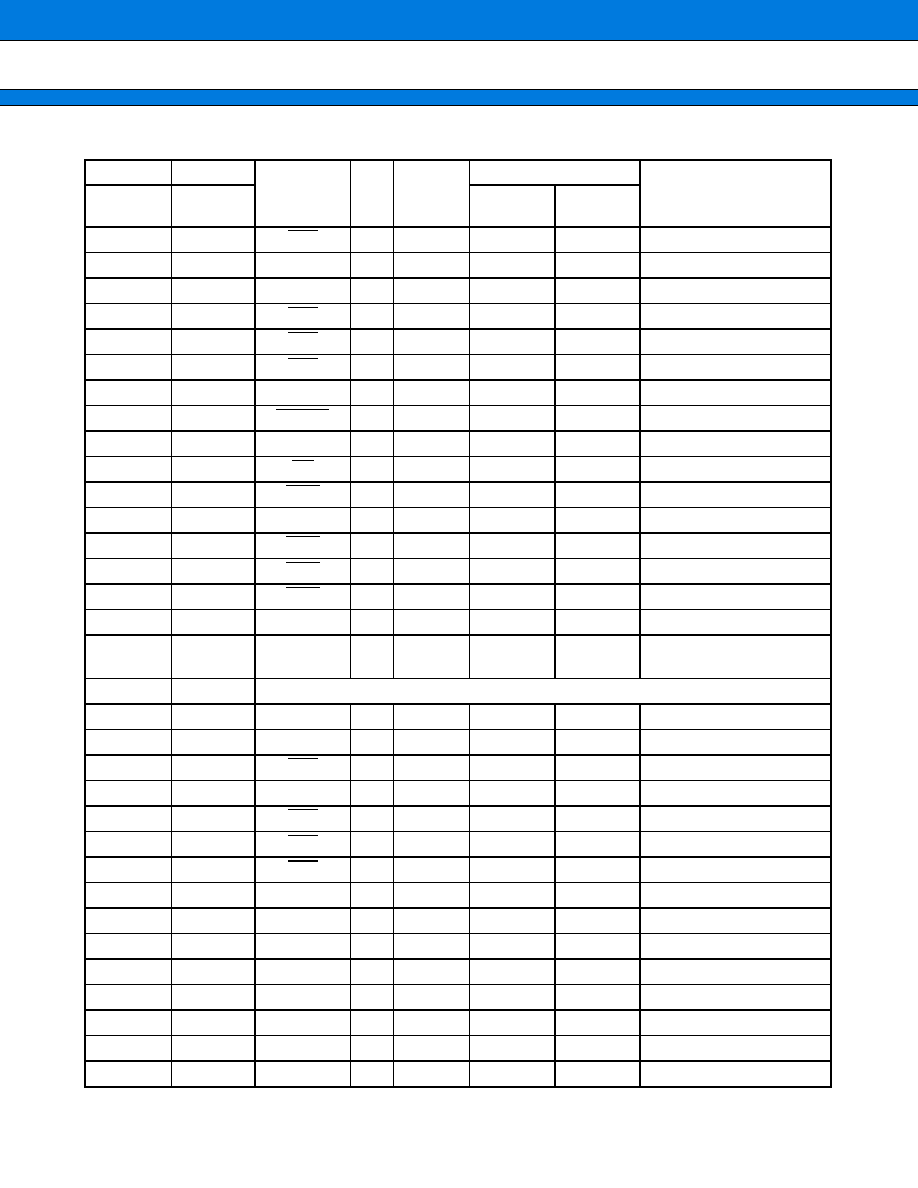

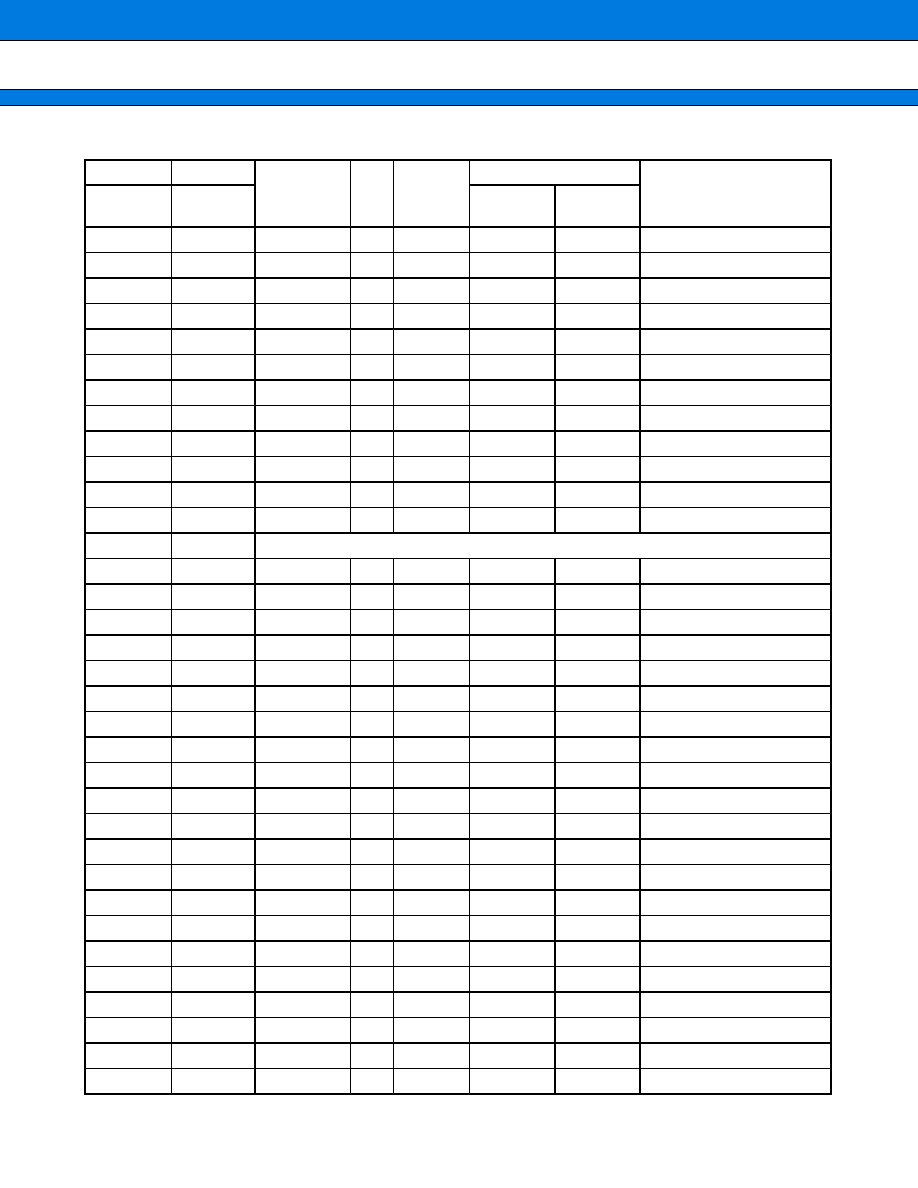

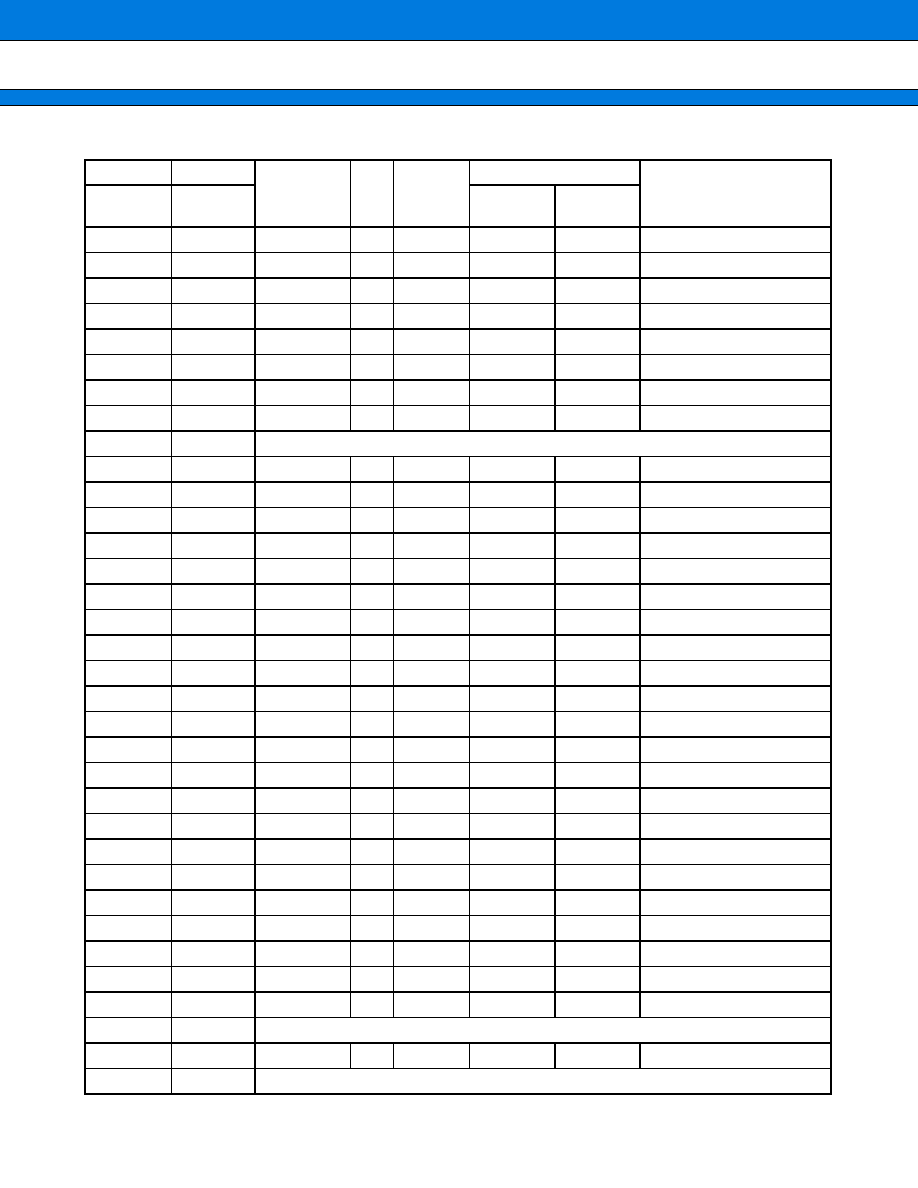

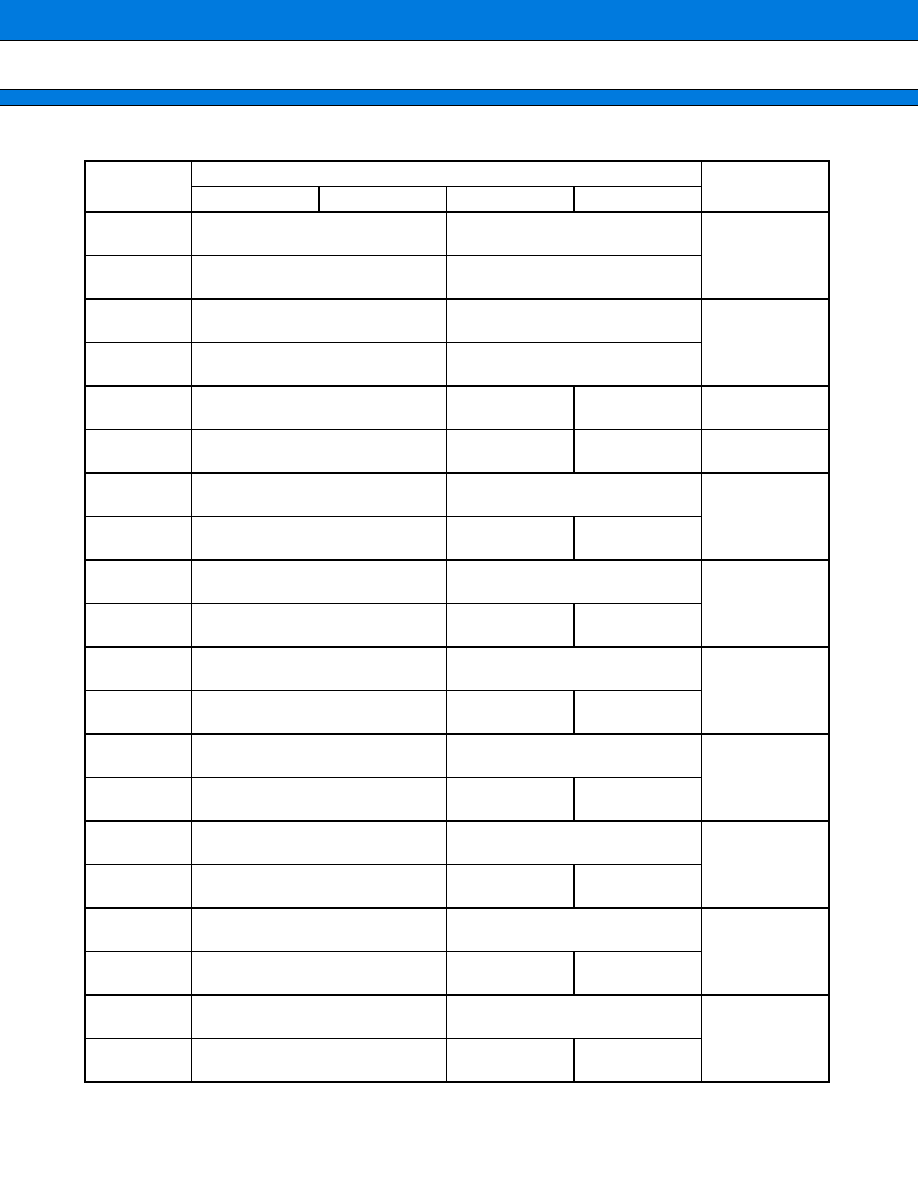

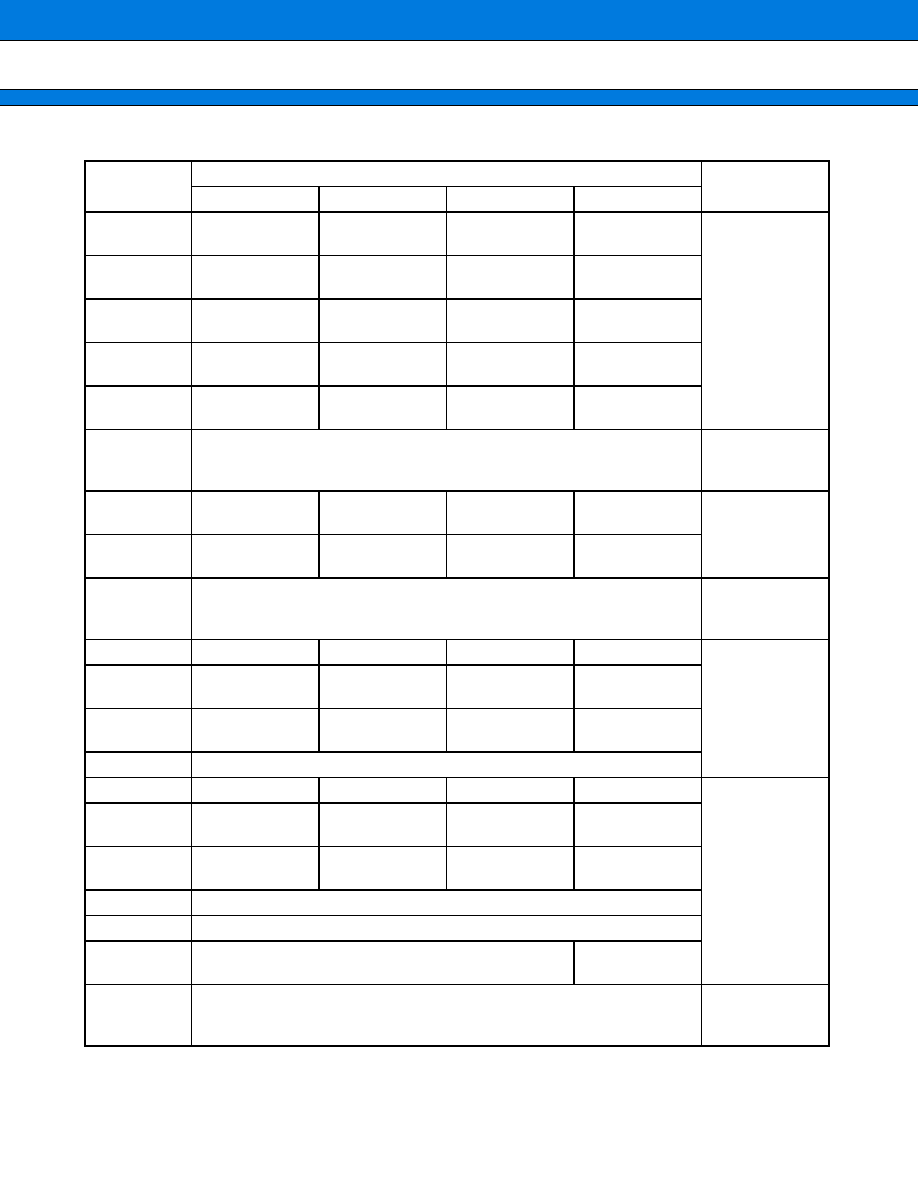

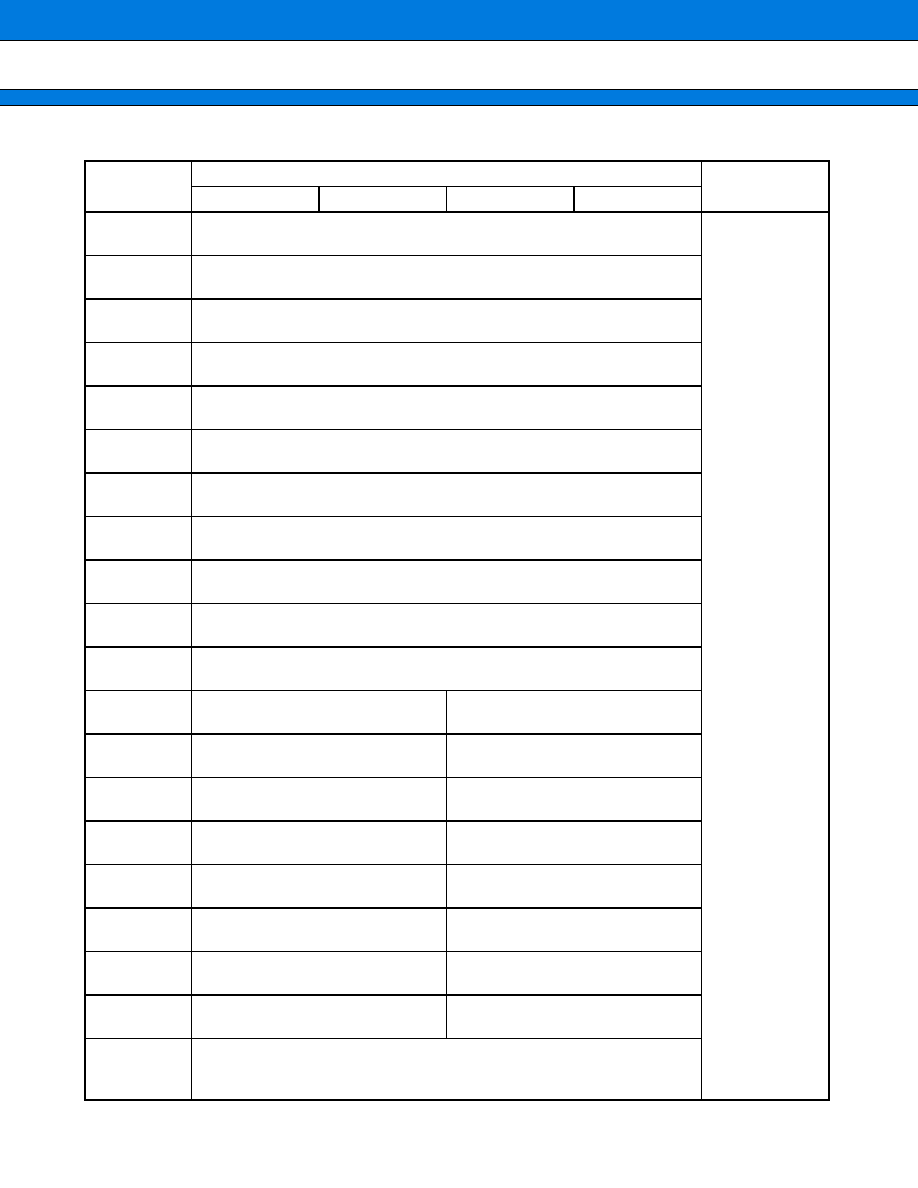

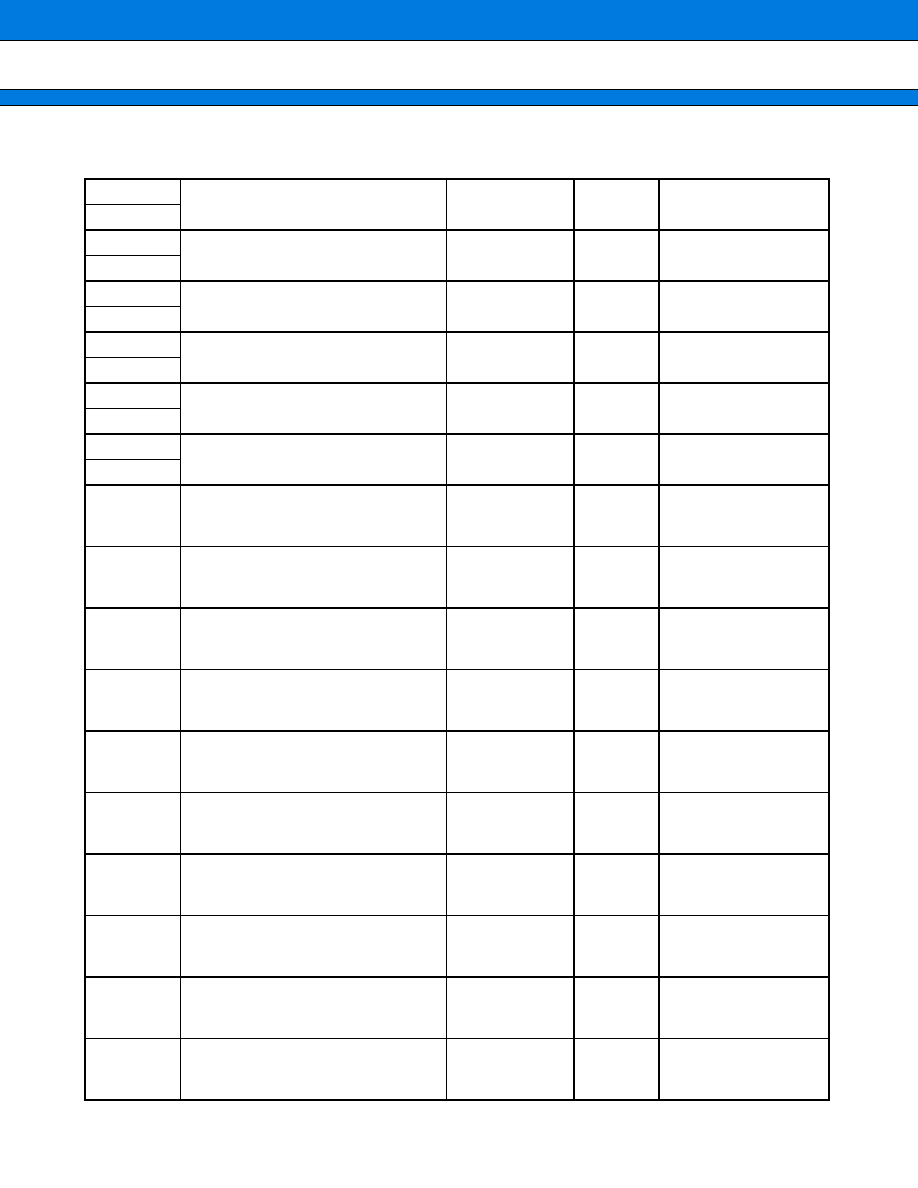

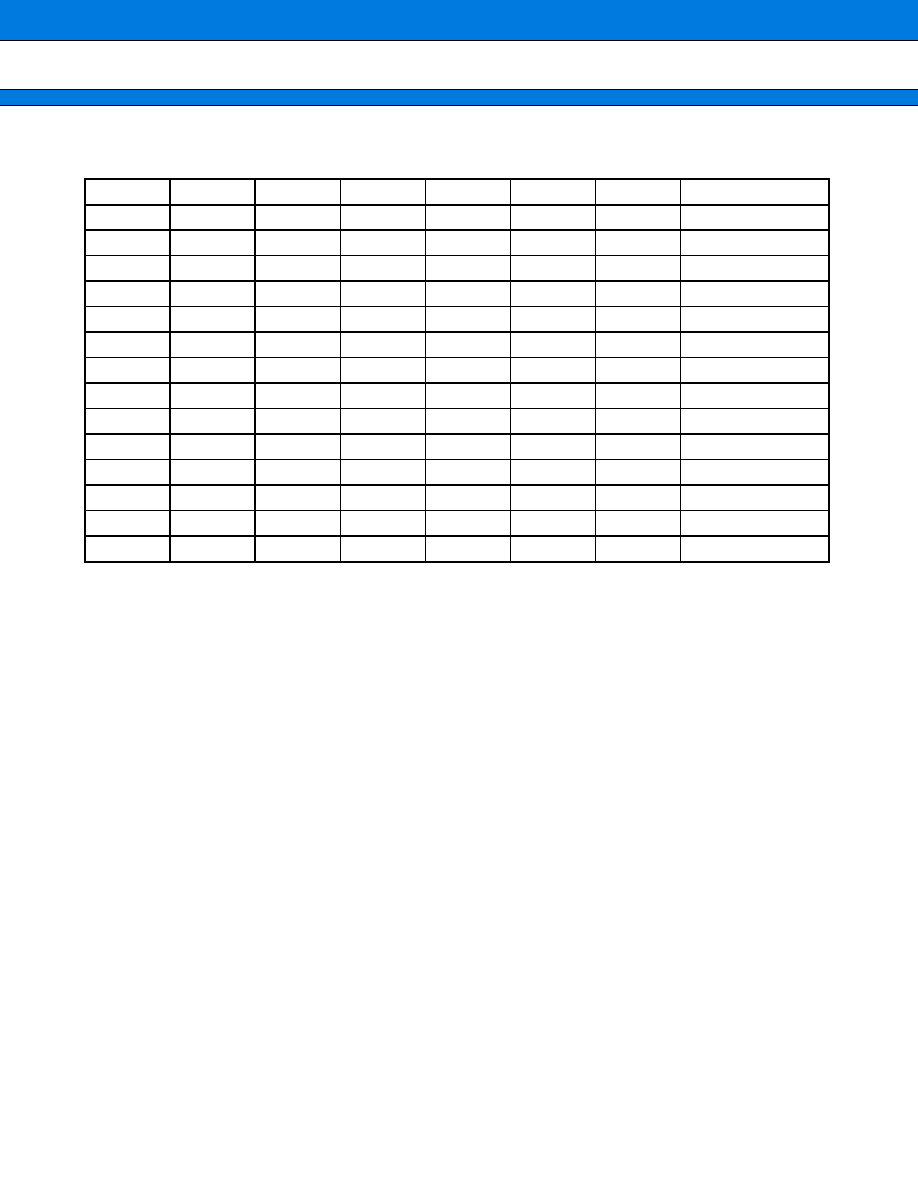

PIN DESCRIPTIONS

(Continued)

Pin No.

Pin No.

Pin Name

I/O

General

Purpose

IO Port

Circuit Type

Function

QFP208

PGA401

FV360GA

F361GA

F362GA

9

202

A0

I/O

Q

Q

Ext. Bus Address Bit 0

10

310

A1

I/O

Q

Q

Ext. Bus Address Bit 1

11

201

A2

I/O

Q

Q

Ext. Bus Address Bit 2

12

357

A3

I/O

Q

Q

Ext. Bus Address Bit 3

26

358

V

SS

25

401

V

DD

13

257

A4

I/O

Q

Q

Ext. Bus Address Bit 4

14

144

A5

I/O

Q

Q

Ext. Bus Address Bit 5

15

309

A6

I/O

Q

Q

Ext. Bus Address Bit 6

16

256

A7

I/O

Q

Q

Ext. Bus Address Bit 7

17

200

A8

I/O

Q

Q

Ext. Bus Address Bit 8

18

356

A9

I/O

Q

Q

Ext. Bus Address Bit 9

19

308

A10

I/O

Q

Q

Ext. Bus Address Bit 10

20

92

A11

I/O

Q

Q

Ext. Bus Address Bit 11

400

V

SS

21

44

A12

I/O

Q

Q

Ext. Bus Address Bit 12

22

255

A13

I/O

Q

Q

Ext. Bus Address Bit 13

23

143

A14

I/O

Q

Q

Ext. Bus Address Bit 14

24

199

A15

I/O

Q

Q

Ext. Bus Address Bit 15

27

307

A16

I/O

Q

Q

Ext. Bus Address Bit 16

355

not connected

28

91

A17

I/O

Q

Q

Ext. Bus Address Bit 17

29

142

A18

I/O

Q

Q

Ext. Bus Address Bit 18

30

254

A19

I/O

Q

Q

Ext. Bus Address Bit 19

399

V

SS

31

43

A20

I/O

Q

Q

Ext. Bus Address Bit 20

198

A21

I/O

Q

Ext. Bus Address Bit 21

141

A22

I/O

Q

Ext. Bus Address Bit 22

90

A23

I/O

Q

Ext. Bus Address Bit 23

197

A24

I/O

P70

Q

Ext. Bus Address Bit 24

306

A25

I/O

P71

Q

Ext. Bus Address Bit 25

42

A26

I/O

P72

Q

Ext. Bus Address Bit 26

253

DREQ2

I/O

P73

A

DMA Request 2

MB91360G Series

7

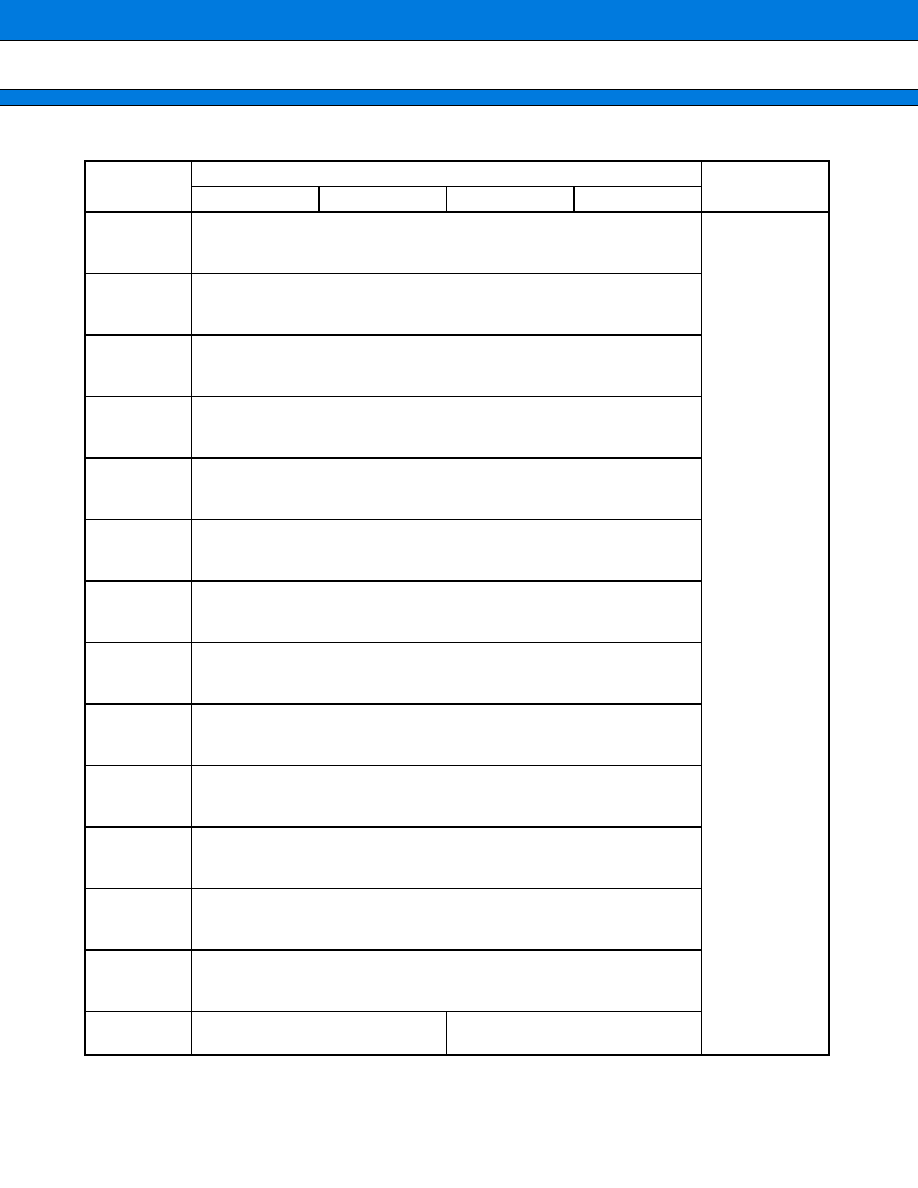

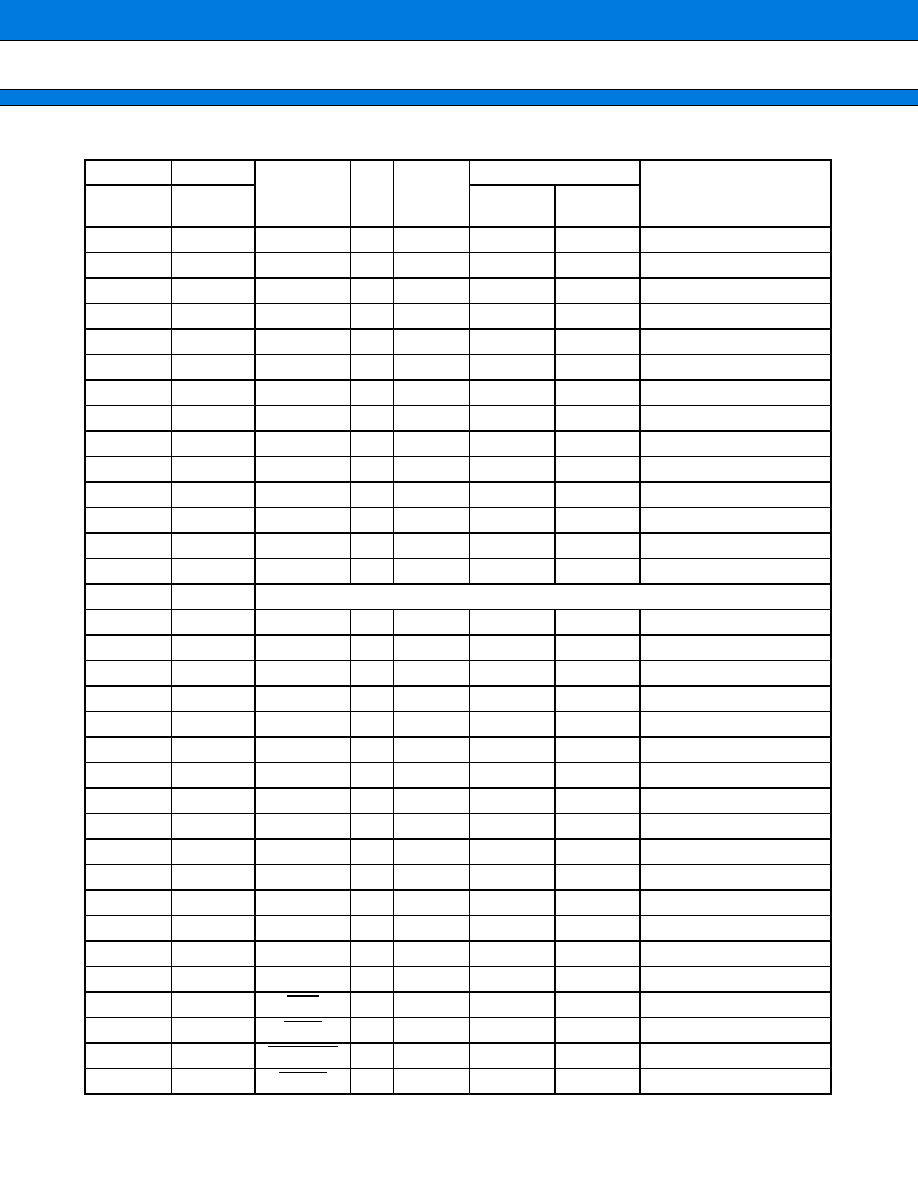

(Continued)

(Continued)

Pin No.

Pin No.

Pin Name

I/O

General

Purpose

IO Port

Circuit Type

Function

QFP208

PGA401

FV360GA

F361GA

F362GA

32

140

CS4

I/O

P74

A

A

Chip Select 4

398

V

SS

354

V

DD

33

196

CS5

I/O

P75

A

A

Chip Select 5

34

89

CS6

I/O

P76

A

A

Chip Select 6

41

CS7

I/O

P77

A

Chip Select 7 (CANs)

35

305

RDY

I/O

S

S

Ext. Bus Control

36

139

BGRNT

I/O

P81

A

A

Ext. Bus Control

37

88

BRQ

I/O

P82

A

A

Ext. Bus Control

38

40

RD

I/O

S

S

Ext. Bus Control

39

304

WR0

I/O

S

S

Ext. Bus Control

353

V

SS

40

39

WR1

I/O

S

S

Ext. Bus Control

41

252

WR2

I/O

S

S

Ext. Bus Control

42

251

WR3

I/O

S

S

Ext. Bus Control

43

87

AS

I/O

P90

A

A

Ext. Bus Control

44

38

ALE

I/O

P91

A

A

(Ext. Bus Control, not yet

implemented)

397

not connected

45

194

CLK

I/O

A

A

Ext. Bus Clk

46

195

AH/BOOT

I/O

P93

A

A

Test Signal/Boot Signal

47

137

CS0

I/O

P94

A

A

Chip select 0

52

352

V

SS

48

250

CS1

I/O

P95

A

A

Chip Select 1

49

351

CS2

I/O

P96

A

A

Chip Select 2

50

138

CS3

I/O

P97

A

A

Chip Select 3

53

37

AN8

I/O

PG0

B

B

ADC Input 8

54

86

AN9

I/O

PG1

B

B

ADC Input 9

55

136

AN10

I/O

PG2

B

B

ADC Input 10

56

303

AN11

I/O

PG3

B

B

ADC Input 11

57

302

AN12

I/O

PG4

B

B

ADC Input 12

58

36

AN13

I/O

PG5

B

B

ADC Input 13

396

V

SS

51

350

V

DD

MB91360G Series

8

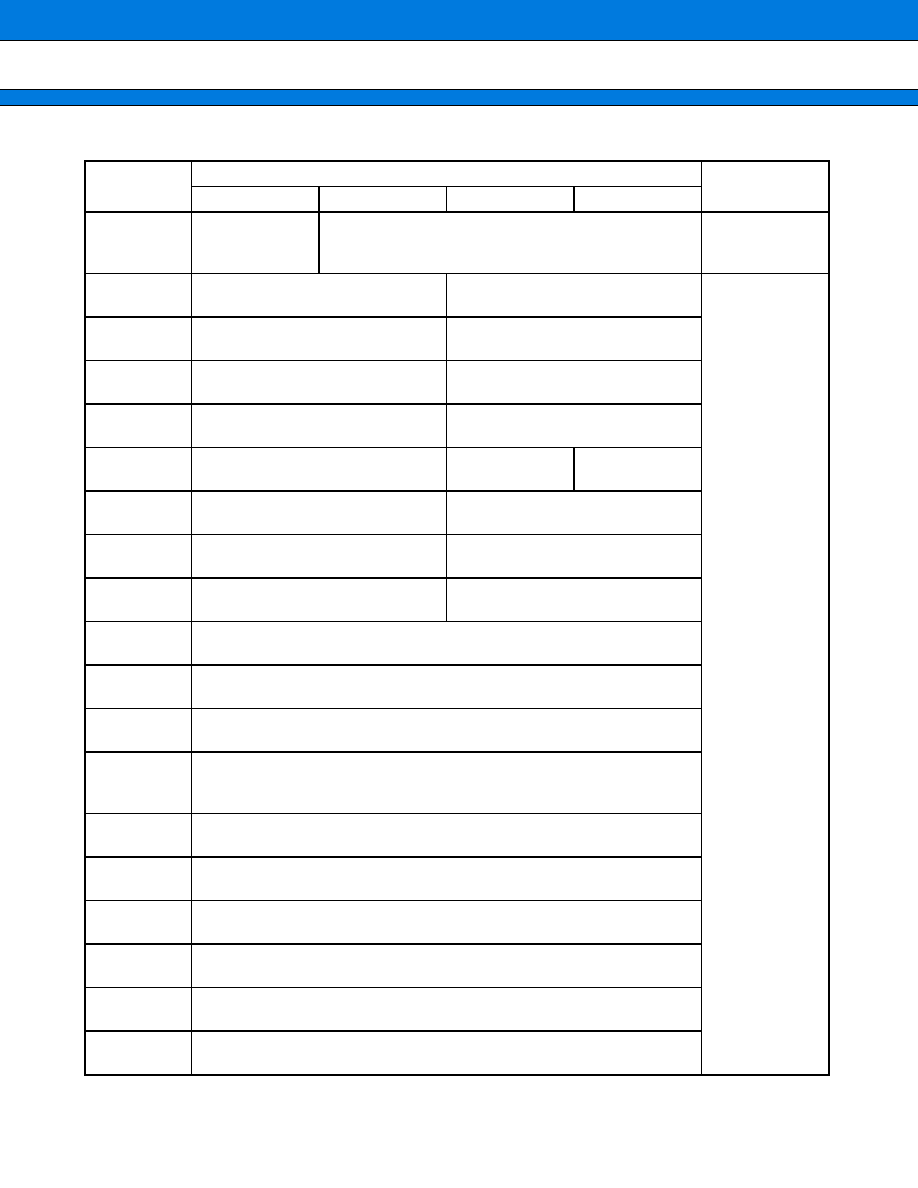

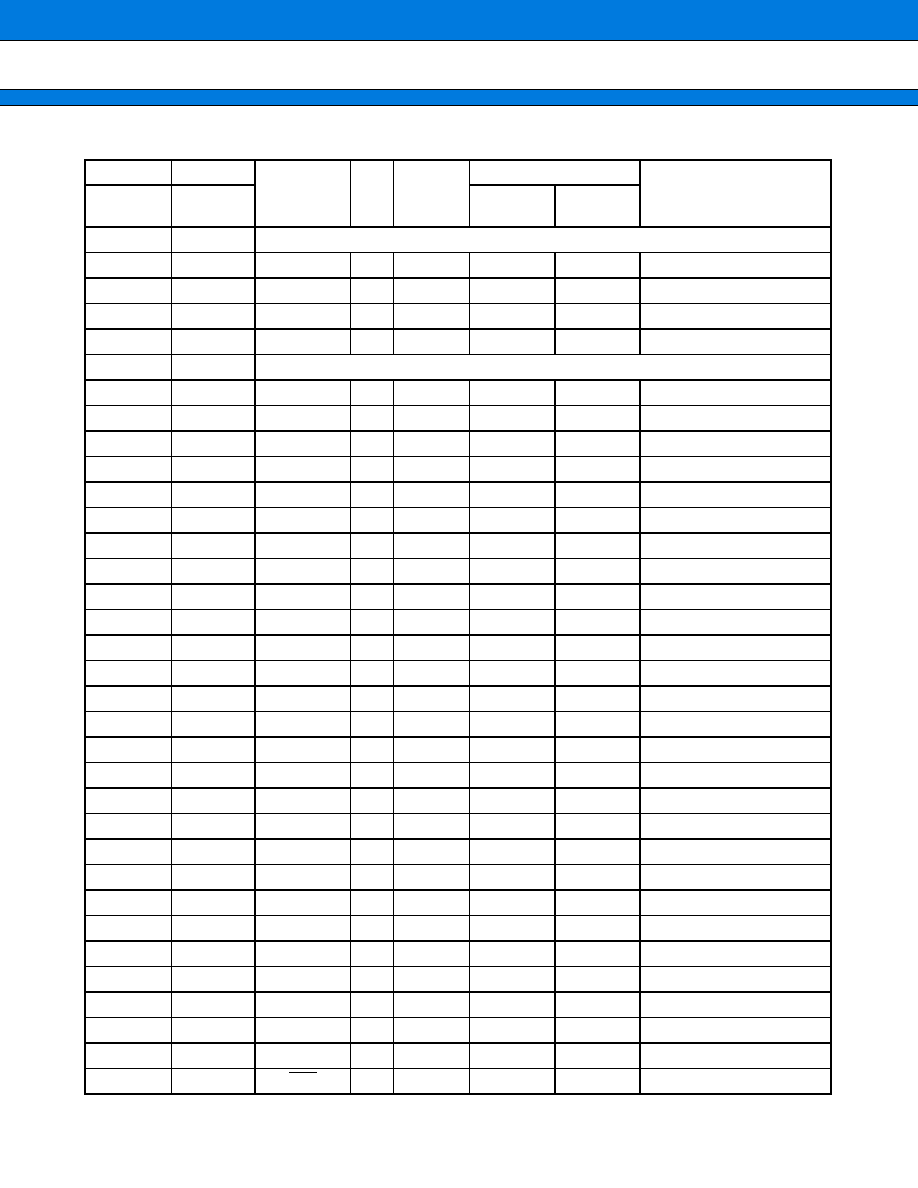

(Continued)

(Continued)

Pin No.

Pin No.

Pin Name

I/O

General

Purpose

IO Port

Circuit Type

Function

QFP208

PGA401

FV360GA

F361GA

F362GA

59

85

AN14

I/O

PG6

B

B

ADC Input 14

60

249

AN15

I/O

PG7

B

B

ADC Input 15

61

193

DREQ0

I/O

PB0

A

A

DMA Request 0

62

135

DACK0

I/O

PB1

A

A

DMA Acknowledge 0

63

84

DEOP0

I/O

PB2

A

A

DMA EOP 0

301

DREQ1

I/O

PB3

A

DMA Request 1

192

DACK1

I/O

PB4

A

DMA Acknowledge 1

191

DEOP1

I/O

PB5

A

DMA EOP 1

395

V

SS

35

DACK2

I/O

PB6

A

DMA Acknowledge 2

349

DEOP2

I/O

PB7

A

DMA EOP 2

64

83

AV

CC

Analog V

CC

65

300

AVRH

R

R

Analog Reference High

66

248

AN0

I/O

PH0

B

B

ADC Input 0

393

not connected

67

82

AN1

I/O

PH1

B

B

ADC Input 1

68

134

AN2

I/O

PH2

B

B

ADC Input 2

69

34

AN3

I/O

PH3

B

B

ADC Input 3

394

V

SS

70

190

AN4

I/O

PH4

B

B

ADC Input 4

71

247

AN5

I/O

PH5

B

B

ADC Input 5

72

81

AN6

I/O

PH6

B

B

ADC Input 6

73

133

AN7

I/O

PH7

B

B

ADC Input 7

299

AVRL

R

Analog Reference Low

74

348

AV

SS

Analog V

SS

75

246

DA0

O

C

C

DAC Output

76

189

DA1

O

C

C

DAC Output

77

132

ALARM

I

D

D

Alarm Comparator Input

78

392

V

SS

79

347

V

DD

80

298

ATG

I/O

PI3

A

A

ADC Trigger Input

81

245

TEST

I

E

E

Test Input

82

188

CPUTEST

I

E

E

Test Input

83

297

LTEST

I

E

E

Test Input

MB91360G Series

9

(Continued)

(Continued)

Pin No.

Pin No.

Pin Name

I/O

General

Purpose

IO Port

Circuit Type

Function

QFP208

PGA401

FV360GA

F361GA

F362GA

244

not connected

84

346

LED0

I/O

PJ0

J

J

LED Port 0

85

187

LED1

I/O

PJ1

J

J

LED Port 1

86

345

LED2

I/O

PJ2

J

J

LED Port 2

391

V

SS

390

not connected

87

243

LED3

I/O

PJ3

J

J

LED Port 3

88

131

LED4

I/O

PJ4

J

J

LED Port 4

89

296

LED5

I/O

PJ5

J

J

LED Port 5

90

242

LED6

I/O

PJ6

J

J

LED Port 6

91

186

LED7

I/O

PJ7

J

J

LED Port 7

94

344

INT0

I/O

PK0

A

A

Ext. Interrupt 0

95

295

INT1

I/O

PK1

A

A

Ext. Interrupt 1

96

80

INT2

I/O

PK2

A

A

Ext. Interrupt 2

93

389

V

SS

97

33

INT3

I/O

PK3

A

A

Ext. Interrupt 3

98

241

INT4

I/O

PK4

A

A

Ext. Interrupt 4

99

130

INT5

I/O

PK5

A

A

Ext. Interrupt 5

100

185

INT6

I/O

PK6

A

A

Ext. Interrupt 6

101

294

INT7

I/O

PK7

A

A

Ext. Interrupt 7

92

343

V

DD

102

79

IN0

I/O

PL0

A

A

ICU Input 0

103

129

IN1

I/O

PL1

A

A

ICU Input 1

104

240

IN2

I/O

PL2

A

A

ICU Input 2

110

388

V

SS

105

32

IN3

I/O

PL3

A

A

ICU Input 3

106

184

OUT0

I/O

PL4

A

A

OCU Output 0

107

128

OUT1

I/O

PL5

A

A

OCU Output 1

108

78

OUT2

I/O

PL6

A

A

OCU Output 2

109

183

OUT3

I/O

PL7

A

A

OCU Output 3

111

293

MD0

I

T

T

Mode Pin 0

112

31

MD1

I

T

T

Mode Pin 1

113

239

MD2

I

T

T

Mode Pin 2

127

NMI

I

E

Non maskable Interrupt

MB91360G Series

10

(Continued)

(Continued)

Pin No.

Pin No.

Pin Name

I/O

General

Purpose

IO Port

Circuit Type

Function

QFP208

PGA401

FV360GA

F361GA

F362GA

387

V

SS

342

not connected

114

182

HST

I

E

E

Hardware Standby

77

RST

I

E

Reset Pin

115

30

INIT

I

U

U

Initial Pin

116

292

MONCLK

O

G

G

System Clock Output

117

126

SELCLK

I

F

F

Clock Selection

118

76

V

DD

119

29

X0

H

H

4 MHz Oscillator Pin

120

291

X1

H

H

4 MHz Oscillator Pin

341

V

SS

28

ICLK

IO

L

ICE CLK

238

ICS0

O

G

ICE Status

237

ICS1

O

G

ICE Status

75

ICS2

O

G

ICE Status

27

ICD0

I/O

N

ICE Data

386

V

DD

180

ICD1

I/O

N

ICE Data

181

ICD2

I/O

N

ICE Data

124

ICD3

I/O

N

ICE Data

340

V

SS

236

BREAK

I

O

ICE Break

339

TDT0

I/O

W

Trace Data

125

TDT1

I/O

W

Trace Data

26

TDT2

I/O

W

Trace Data

74

TDT3

I/O

W

Trace Data

123

TDT4

I/O

W

Trace Data

290

TDT5

I/O

W

Trace Data

289

TDT6

I/O

W

Trace Data

25

TDT7

I/O

W

Trace Data

385

V

SS

3

338

V

DD

3

73

TDT8

I/O

W

Trace Data

235

TDT9

I/O

W

Trace Data

MB91360G Series

11

(Continued)

(Continued)

Pin No.

Pin No.

Pin Name

I/O

General

Purpose

IO Port

Circuit Type

Function

QFP208

PGA401

FV360GA

F361GA

F362GA

179

TDT10

I/O

W

Trace Data

122

TDT11

I/O

W

Trace Data

72

TDT12

I/O

W

Trace Data

288

TDT13

I/O

W

Trace Data

178

TDT14

I/O

W

Trace Data

177

TDT15

I/O

W

Trace Data

384

V

SS

3

24

TDT16

I/O

W

Trace Data

337

TDT17

I/O

W

Trace Data

71

TDT18

I/O

W

Trace Data

287

TDT19

I/O

W

Trace Data

234

TDT20

I/O

W

Trace Data

382

not connected

70

TDT21

I/O

W

Trace Data

121

TDT22

I/O

W

Trace Data

23

TDT23

I/O

W

Trace Data

383

V

SS

3

176

TDT24

I/O

W

Trace Data

233

TDT25

I/O

W

Trace Data

69

TDT26

I/O

W

Trace Data

120

TDT27

I/O

W

Trace Data

286

TDT28

I/O

W

Trace Data

336

TDT29

I/O

W

Trace Data

232

TDT30

I/O

W

Trace Data

175

TDT31

I/O

W

Trace Data

119

TDT32

I/O

W

Trace Data

381

V

SS

3

335

V

DD

3

285

TDT33

I/O

W

Trace Data

231

TDT34

I/O

W

Trace Data

174

TDT35

I/O

W

Trace Data

284

TDT36

I/O

W

Trace Data

230

TDT37

I/O

W

Trace Data

334

TDT38

I/O

W

Trace Data

MB91360G Series

12

(Continued)

(Continued)

Pin No.

Pin No.

Pin Name

I/O

General

Purpose

IO Port

Circuit Type

Function

QFP208

PGA401

FV360GA

F361GA

F362GA

173

TDT39

I/O

W

Trace Data

333

TDT40

I/O

W

Trace Data

380

V

SS

3

379

not connected

229

TDT41

I/O

W

Trace Data

118

TDT42

I/O

W

Trace Data

283

TDT43

I/O

W

Trace Data

228

TDT44

I/O

W

Trace Data

172

TDT45

I/O

W

Trace Data

332

TDT46

I/O

W

Trace Data

282

TDT47

I/O

W

Trace Data

68

TDT48

I/O

W

Trace Data

378

V

SS

3

22

TDT49

I/O

W

Trace Data

227

TDT50

I/O

W

Trace Data

117

TDT51

I/O

W

Trace Data

171

TDT52

I/O

W

Trace Data

281

TDT53

I/O

W

Trace Data

331

V

DD

3

67

TDT54

I/O

W

Trace Data

116

TDT55

I/O

W

Trace Data

226

TDT56

I/O

W

Trace Data

377

V

SS

3

21

TDT57

I/O

W

Trace Data

170

TDT58

I/O

W

Trace Data

115

TDT59

I/O

W

Trace Data

66

TDT60

I/O

W

Trace Data

169

TDT61

I/O

W

Trace Data

280

TDT62

I/O

W

Trace Data

20

TDT63

I/O

W

Trace Data

225

TDT64

I/O

W

Trace Data

114

TDT65

I/O

W

Trace Data

376

V

SS

3

330

not connected

MB91360G Series

13

(Continued)

(Continued)

Pin No.

Pin No.

Pin Name

I/O

General

Purpose

IO Port

Circuit Type

Function

QFP208

PGA401

FV360GA

F361GA

F362GA

168

TDT66

I/O

W

Trace Data

65

TDT67

I/O

W

Trace Data

19

TDT68

I/O

W

Trace Data

279

TAD0

O

X

Trace Address

113

TAD1

O

X

Trace Address

64

TAD2

O

X

Trace Address

18

TAD3

O

X

Trace Address

278

TAD4

O

X

Trace Address

329

V

SS

3

17

TAD5

O

X

Trace Address

224

TAD6

O

X

Trace Address

223

TAD7

O

X

Trace Address

63

TAD8

O

X

Trace Address

16

TAD9

O

X

Trace Address

375

V

DD

3

166

TAD10

O

X

Trace Address

167

TAD11

O

X

Trace Address

111

TAD12

O

X

Trace Address

328

V

SS

3

222

TAD13

O

X

Trace Address

327

TAD14

O

X

Trace Address

112

TAD15

O

X

Trace Address

15

TWR

O

X

Trace Control

62

TOE

O

X

Trace Control

110

TCLK

I/O

W

Trace Control

277

TCE1

O

X

Trace Control

276

TADSC

O

X

Trace Control

14

EXRAM

I

P

Trace Control

374

V

SS

326

V

DD

126

61

SGO

I/O

PM0

A

A

Sound Generator SGO

127

221

SGA

I/O

PM1

A

A

Sound Generator SGA

128

165

SDA

I/O

PM2

Y

Y

I

2

C SDA

129

109

SCL

I/O

PM3

Y

Y

I

2

C SCL

MB91360G Series

14

(Continued)

(Continued)

Pin No.

Pin No.

Pin Name

I/O

General

Purpose

IO Port

Circuit Type

Function

QFP208

PGA401

FV360GA

F361GA

F362GA

60

not connected

275

V

DD

121

164

X0A

I

I

reserved

should be

connected

to be V

SS

32 kHz Oscillator Pin

122

163

X1A

O

I

reserved

should be

left open

32 kHz Oscillator Pin

123

373

V

SS

13

V

DD

124

325

CPO

not connected

reserved

should be

left open

125

59

VCI

not connected

reserved

should be

connected

to be V

SS

274

not connected

220

V

SS

371

not connected

130

58

SOT4

I/O

PN0

A

A

SIO Output

131

108

SIN4

I/O

PN1

A

A

SIO Input

132

12

SCK4

I/O

PN2

A

A

SIO Clock

372

V

SS

162

V

DD

133

219

SIN3

I/O

PN3

A

A

SIO Input

134

57

SOT3

I/O

PN4

A

A

SIO Output

135

107

SCK3

I/O

PN5

A

A

SIO Clock

273

V

SS

324

V

DD

136

218

OCPA0

I/O

PO0

A

A

PPG Output

137

161

OCPA1

I/O

PO1

A

A

PPG Output

138

106

OCPA2

I/O

PO2

A

A

PPG Output

370

V

SS

323

V

DD

139

272

OCPA3

I/O

PO3

A

A

PPG Output

MB91360G Series

15

(Continued)

(Continued)

Pin No.

Pin No.

Pin Name

I/O

General

Purpose

IO Port

Circuit Type

Function

QFP208

PGA401

FV360GA

F361GA

F362GA

140

217

OCPA4

I/O

PO4

A

A

PPG Output

141

160

OCPA5

I/O

PO5

A

A

PPG Output

271

V

SS

144

216

V

DD

142

322

OCPA6

I/O

PO6

A

A

PPG Output

143

159

OCPA7

I/O

PO7

A

A

PPG Output

146

321

TX0

I/O

PP0

Q

Q

CAN 0 TX

145

369

V

SS

368

not connected

147

215

RX0

I/O

PP1

Q

Q

CAN 0 RX

148

105

TX1

I/O

PP2

Q

Q

CAN 1 TX

149

270

RX1

I/O

PP3

Q

Q

CAN 1 RX

214

V

SS

158

V

DD

150

320

TX2

I/O

PP4

Q

Q

CAN 2 TX

151

269

RX2

I/O

PP5

Q

Q

CAN 2 RX

56

TX3

I/O

PP6

Q

CAN 3 TX

367

V

SS

11

V

DD

213

RX3

I/O

PP7

Q

CAN 3 RX

152

104

SIN0

I/O

PQ0

A

A

UART 0 Input

153

157

SOT0

I/O

PQ1

A

A

UART 0 Output

268

V

SS

319

V

DD

154

55

SIN1

I/O

PQ2

A

A

UART 1 Input

155

103

SOT1

I/O

PQ3

A

A

UART 1 Output

156

212

SIN2

I/O

PQ4

A

A

UART 2 Input

366

V

SS

160

10

V

DD

V

DD

157

156

SOT2

I/O

PQ5

A

A

UART 2 Output

159

102

V

CC

3C

C

C

Bypass Capacitor Pin

54

not connected

158

155

V

SS

267

not connected

MB91360G Series

16

(Continued)

(Continued)

Pin No.

Pin No.

Pin Name

I/O

General

Purpose

IO Port

Circuit Type

Function

QFP208

PGA401

FV360GA

F361GA

F362GA

162

9

PWM1P0

I/O

PR0

K

K

SMC 0

163

211

PWM1M0

I/O

PR1

K

K

SMC 0

164

101

PWM2P0

I/O

PR2

K

K

SMC 0

161

365

HV

SS

318

not connected

165

154

PWM2M0

I/O

PR3

M

M

SMC 0

167

53

PWM1P1

I/O

PR4

K

K

SMC 1

168

8

PWM1M1

I/O

PR5

K

K

SMC 1

266

HV

SS

166

100

HV

DD

169

52

PWM2P1

I/O

PR6

K

K

SMC 1

170

7

PWM2M1

I/O

PR7

M

M

SMC 1

265

not connected

171

317

HV

SS

6

HV

DD

172

210

PWM1P2

I/O

PS0

K

K

SMC 2

173

209

PWM1M2

I/O

PS1

K

K

SMC 2

174

51

PWM2P2

I/O

PS2

K

K

SMC 2

5

HV

SS

364

not connected

175

152

PWM2M2

I/O

PS3

M

M

SMC 2

177

153

PWM1P3

I/O

PS4

K

K

SMC 3

178

98

PWM1M3

I/O

PS5

K

K

SMC 3

181

316

HV

SS

176

208

HV

DD

179

315

PWM2P3

I/O

PS6

K

K

SMC 3

180

99

PWM2M3

I/O

PS7

M

M

SMC 3

4

not connected

50

V

SS

182

97

V

DD

183

264

D0

I/O

Q

Q

Ext. Bus Data Bit 0

184

263

D1

I/O

Q

Q

Ext. Bus Data Bit 1

185

3

D2

I/O

Q

Q

Ext. Bus Data Bit 2

363

V

SS

MB91360G Series

17

(Continued)

Pin No.

Pin No.

Pin Name

I/O

General

Purpose

IO Port

Circuit Type

Function

QFP208

PGA401

FV360GA

F361GA

F362GA

314

not connected

186

49

D3

I/O

Q

Q

Ext. Bus Data Bit 3

187

207

D4

I/O

Q

Q

Ext. Bus Data Bit 4

188

151

D5

I/O

Q

Q

Ext. Bus Data Bit 5

189

96

D6

I/O

Q

Q

Ext. Bus Data Bit 6

190

48

D7

I/O

Q

Q

Ext. Bus Data Bit 7

191

262

D8

I/O

Q

Q

Ext. Bus Data Bit 8

192

150

D9

I/O

Q

Q

Ext. Bus Data Bit 9

193

149

D10

I/O

Q

Q

Ext. Bus Data Bit 10

362

V

SS

194

2

D11

I/O

Q

Q

Ext. Bus Data Bit 11

195

313

D12

I/O

Q

Q

Ext. Bus Data Bit 12

196

47

D13

I/O

Q

Q

Ext. Bus Data Bit 13

197

261

D14

I/O

Q

Q

Ext. Bus Data Bit 14

200

206

D15

I/O

Q

Q

Ext. Bus Data Bit 15

198

360

V

DD

201

46

D16

I/O

Q

Q

Ext. Bus Data Bit 16

202

95

D17

I/O

Q

Q

Ext. Bus Data Bit 17

203

1

D18

I/O

Q

Q

Ext. Bus Data Bit 18

199

361

V

SS

204

148

D19

I/O

Q

Q

Ext. Bus Data Bit 19

205

205

D20

I/O

Q

Q

Ext. Bus Data Bit 20

206

45

D21

I/O

Q

Q

Ext. Bus Data Bit 21

207

94

D22

I/O

Q

Q

Ext. Bus Data Bit 22

208

260

D23

I/O

Q

Q

Ext. Bus Data Bit 23

1

312

D24

I/O

Q

Q

Ext. Bus Data Bit 24

2

204

D25

I/O

Q

Q

Ext. Bus Data Bit 25

3

147

D26

I/O

Q

Q

Ext. Bus Data Bit 26

4

93

D27

I/O

Q

Q

Ext. Bus Data Bit 27

359

V

SS

311

not connected

5

259

D28

I/O

Q

Q

Ext. Bus Data Bit 28

6

203

D29

I/O

Q

Q

Ext. Bus Data Bit 29

7

146

D30

I/O

Q

Q

Ext. Bus Data Bit 30

8

258

D31

I/O

Q

Q

Ext. Bus Data Bit 31

MB91360G Series

18

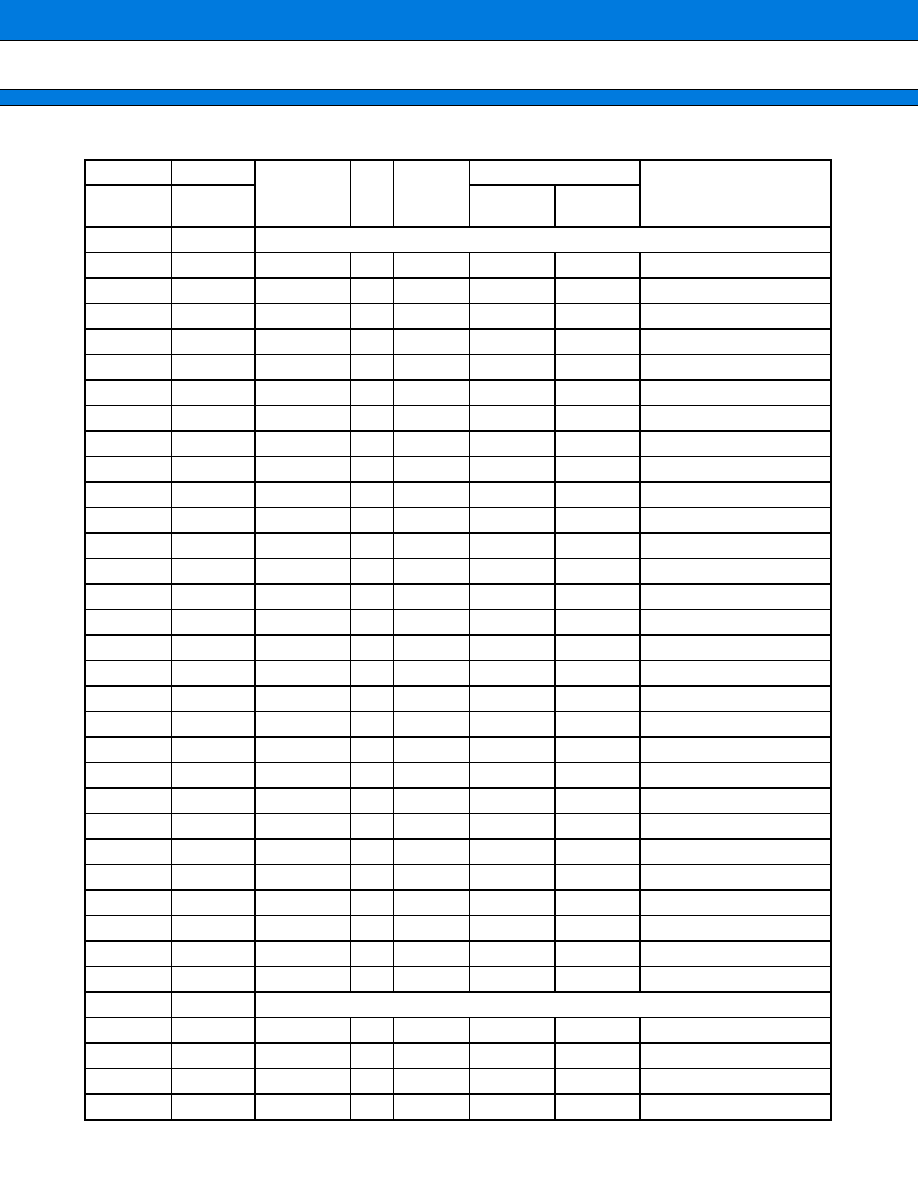

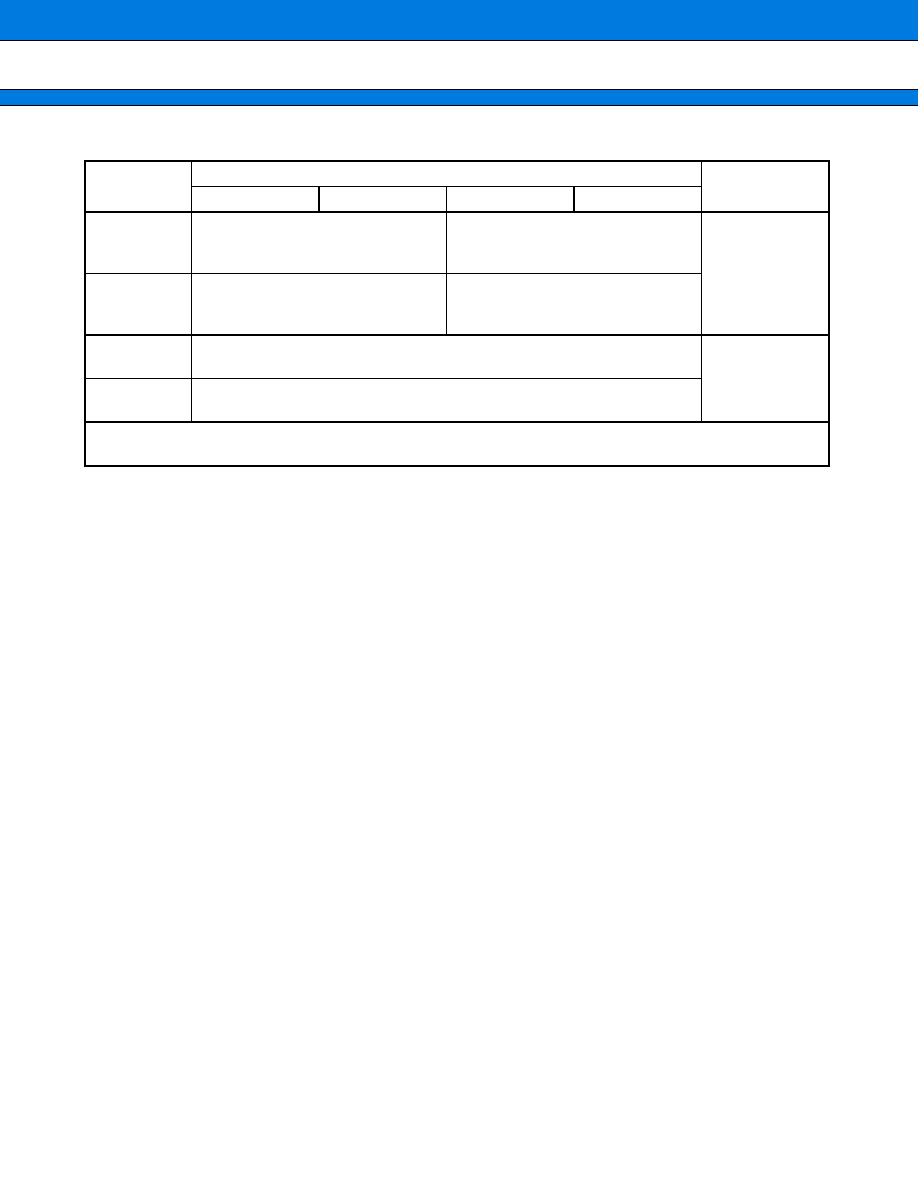

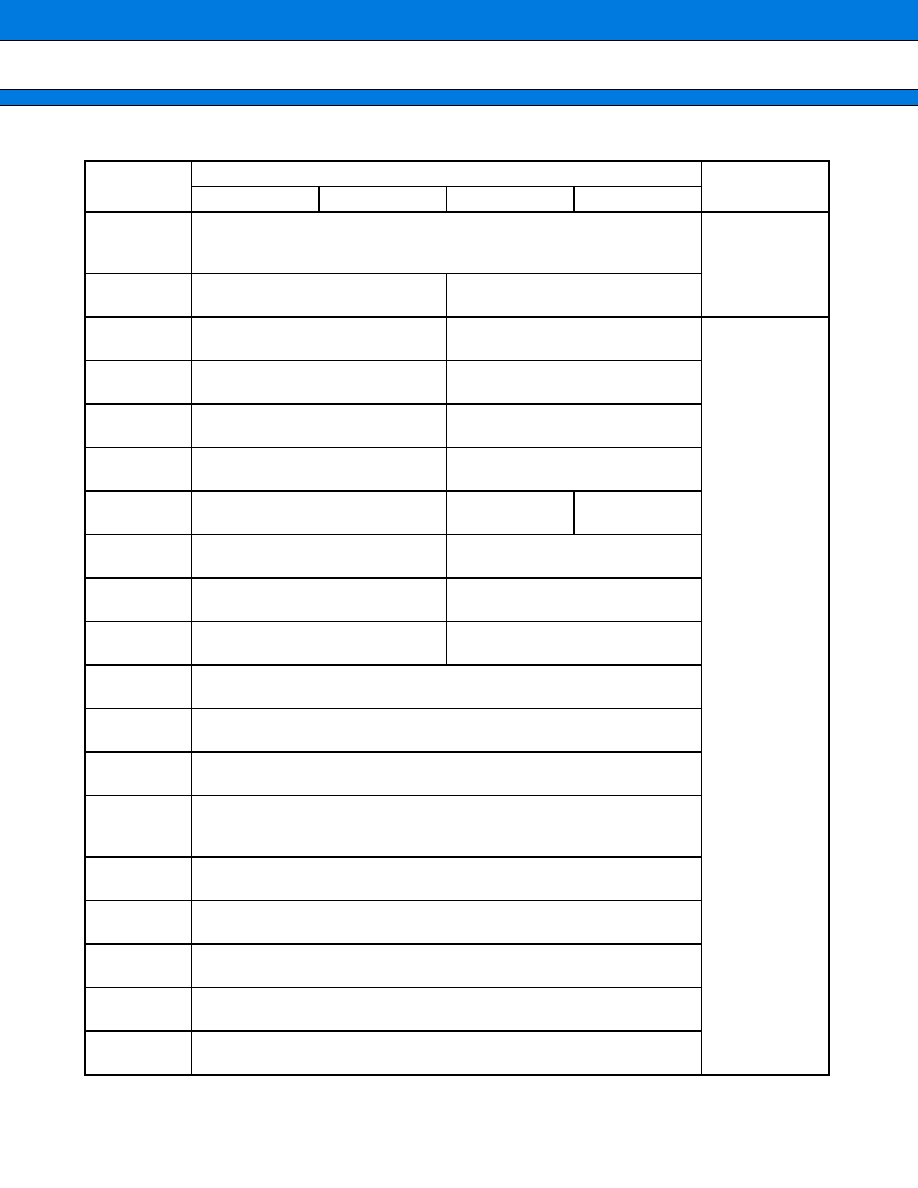

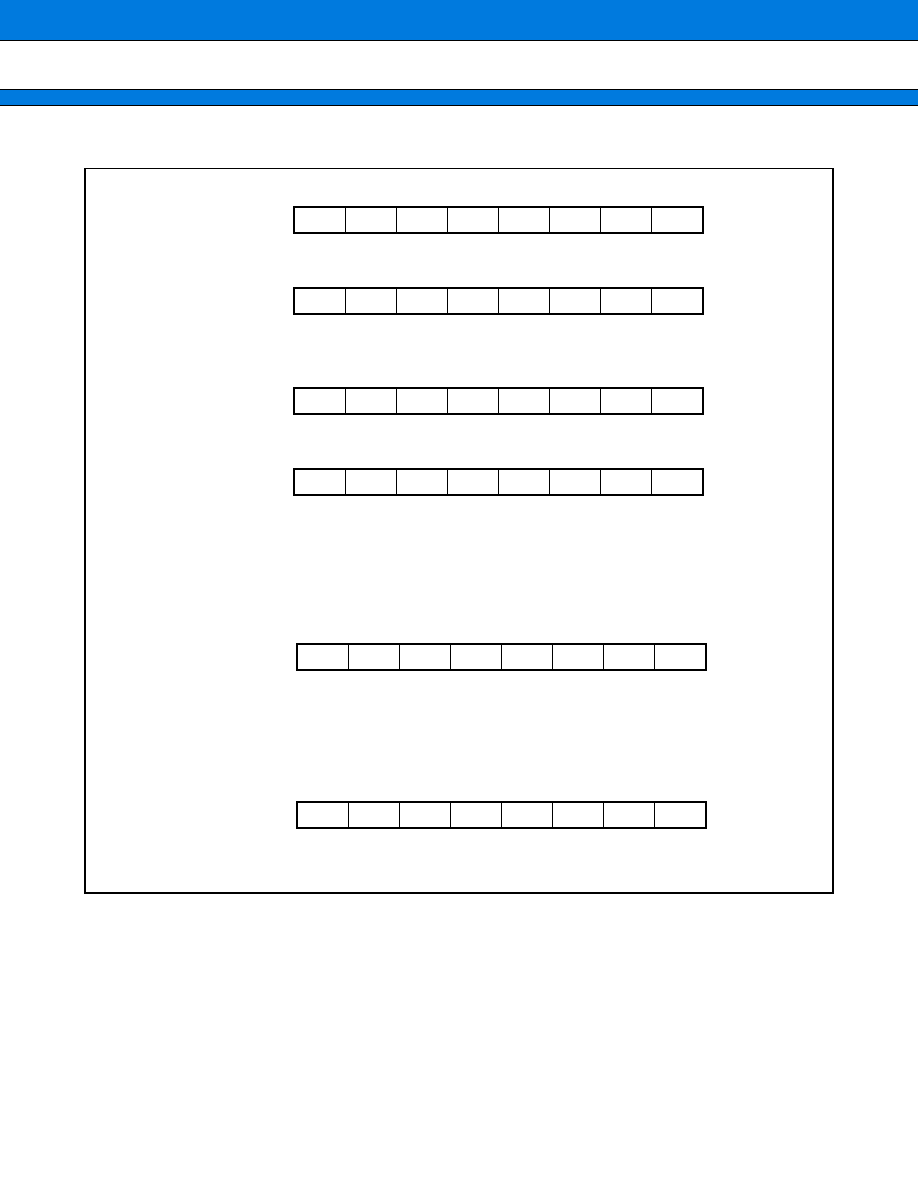

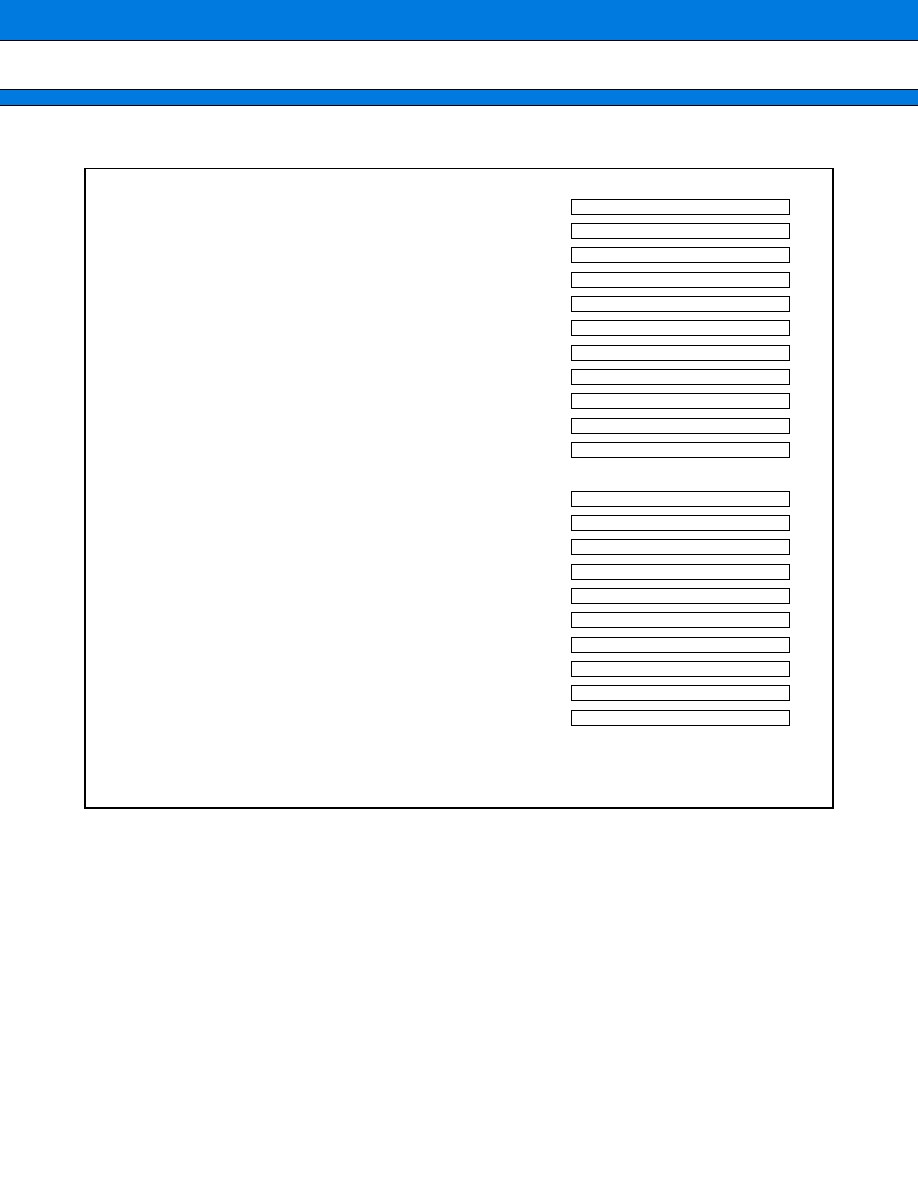

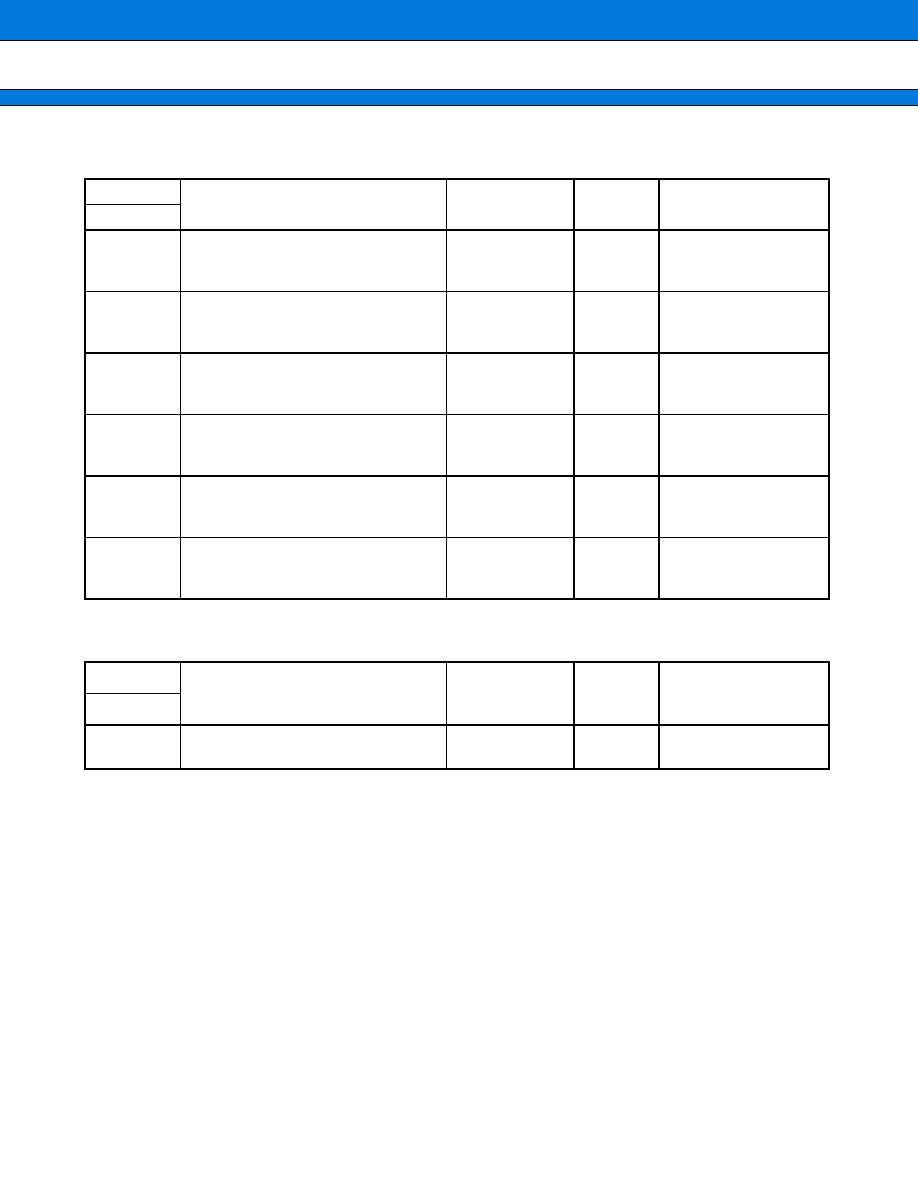

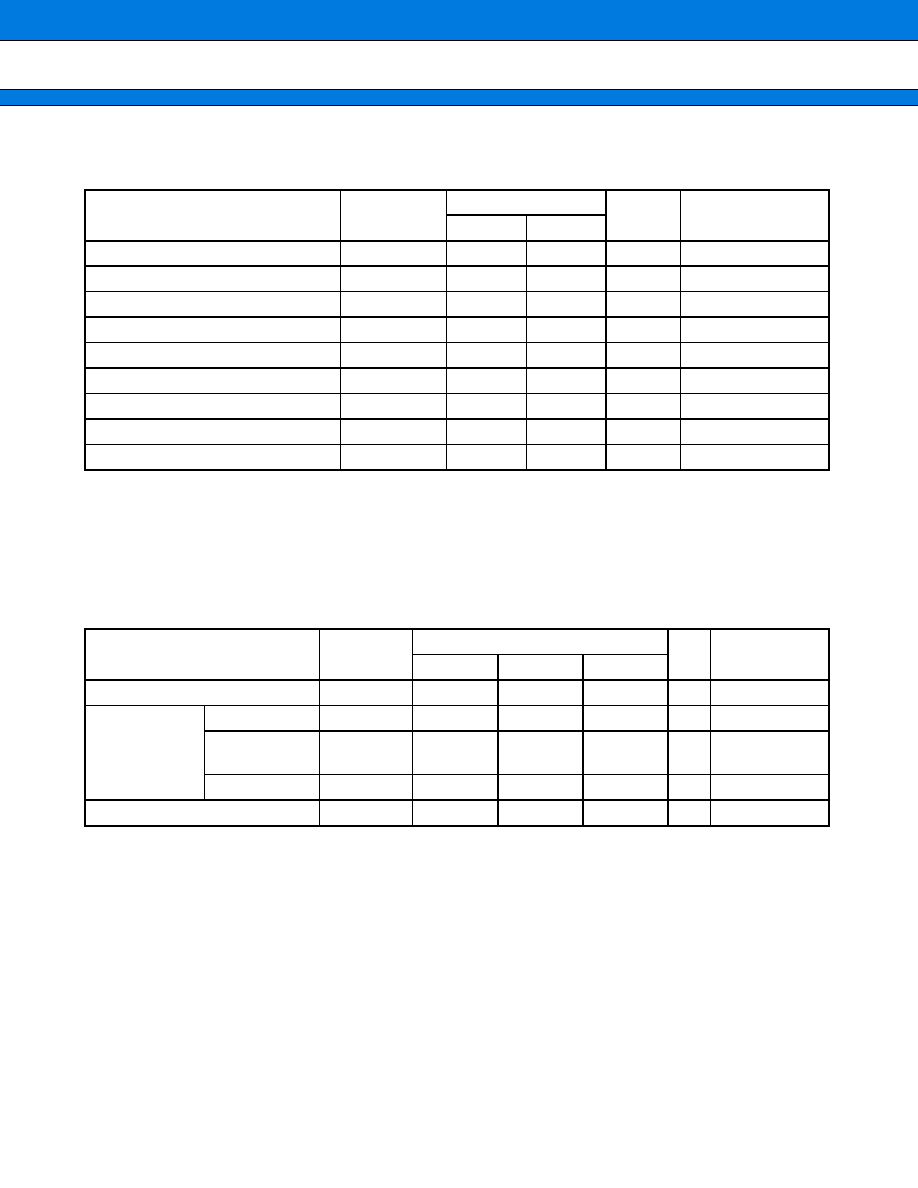

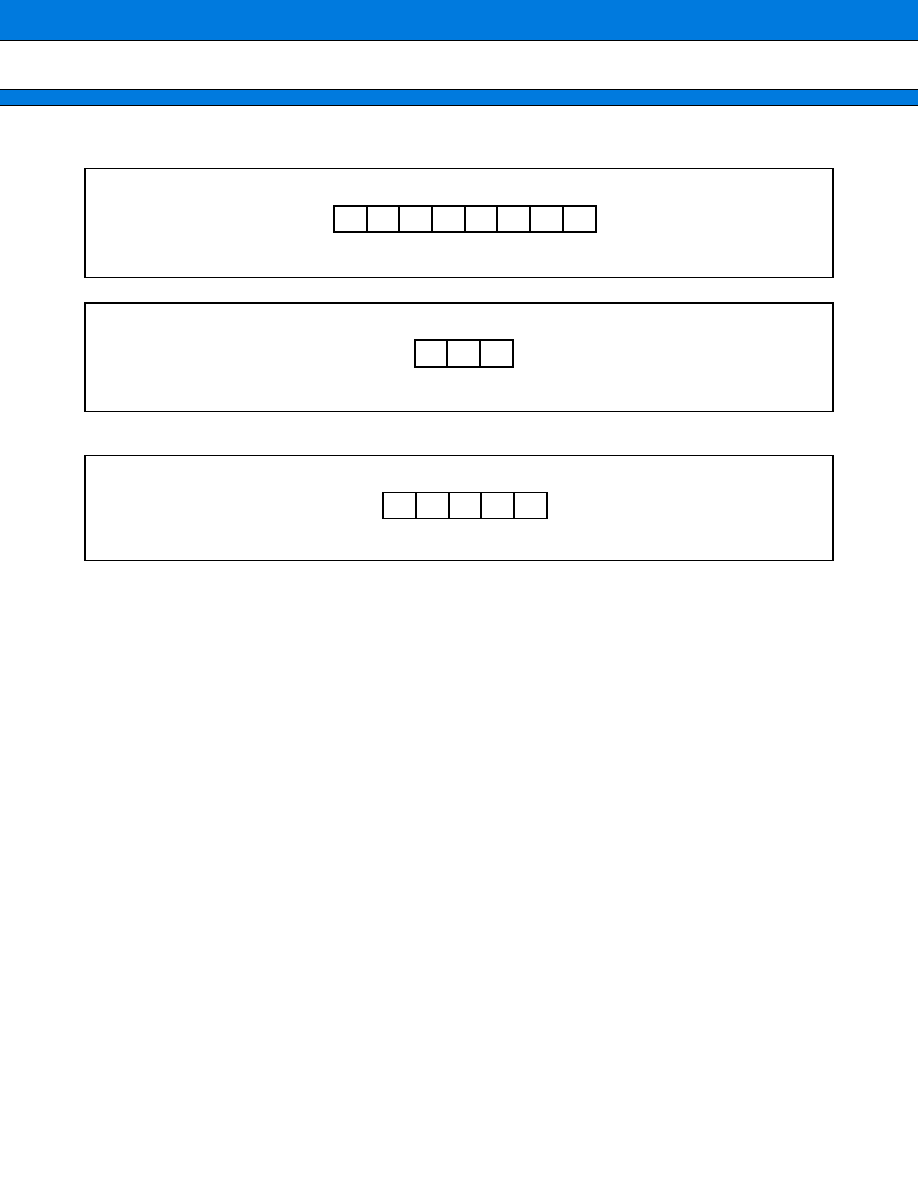

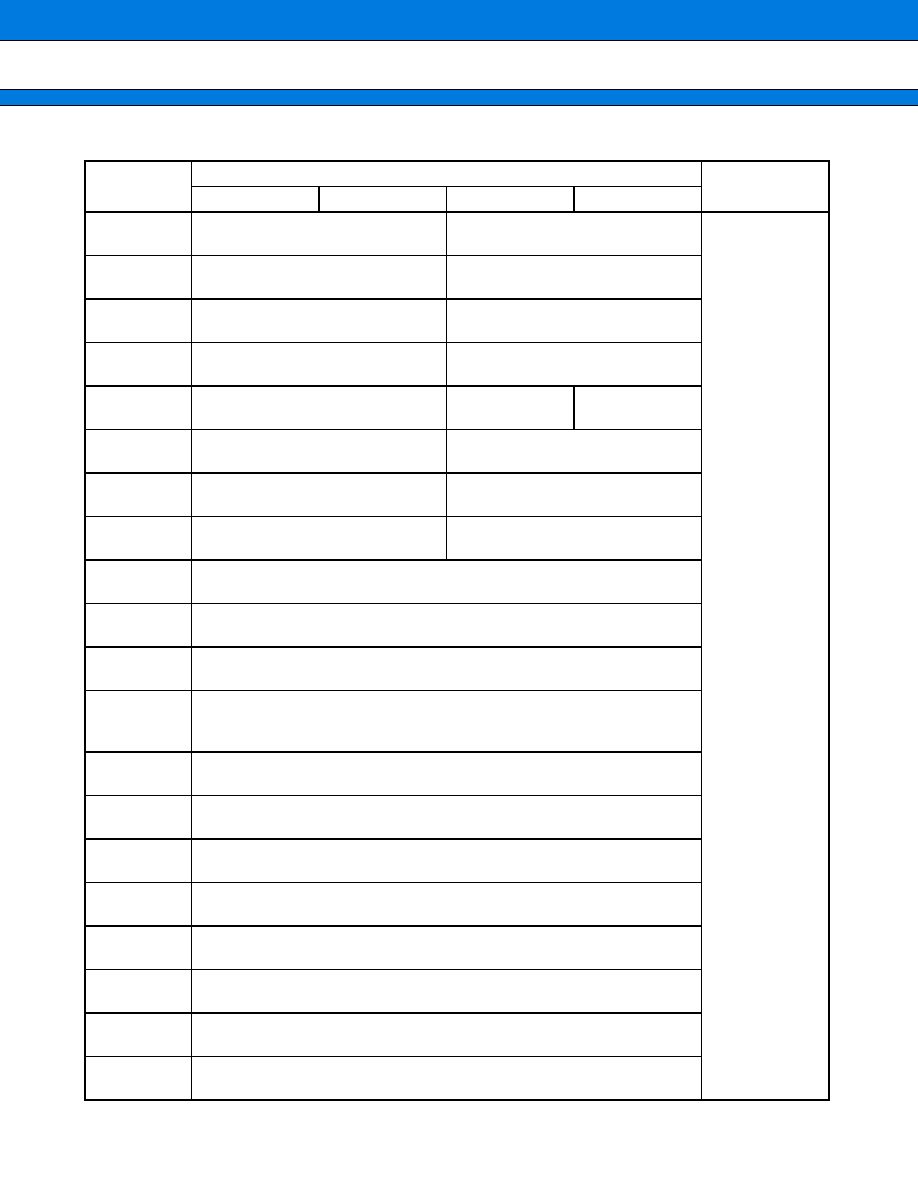

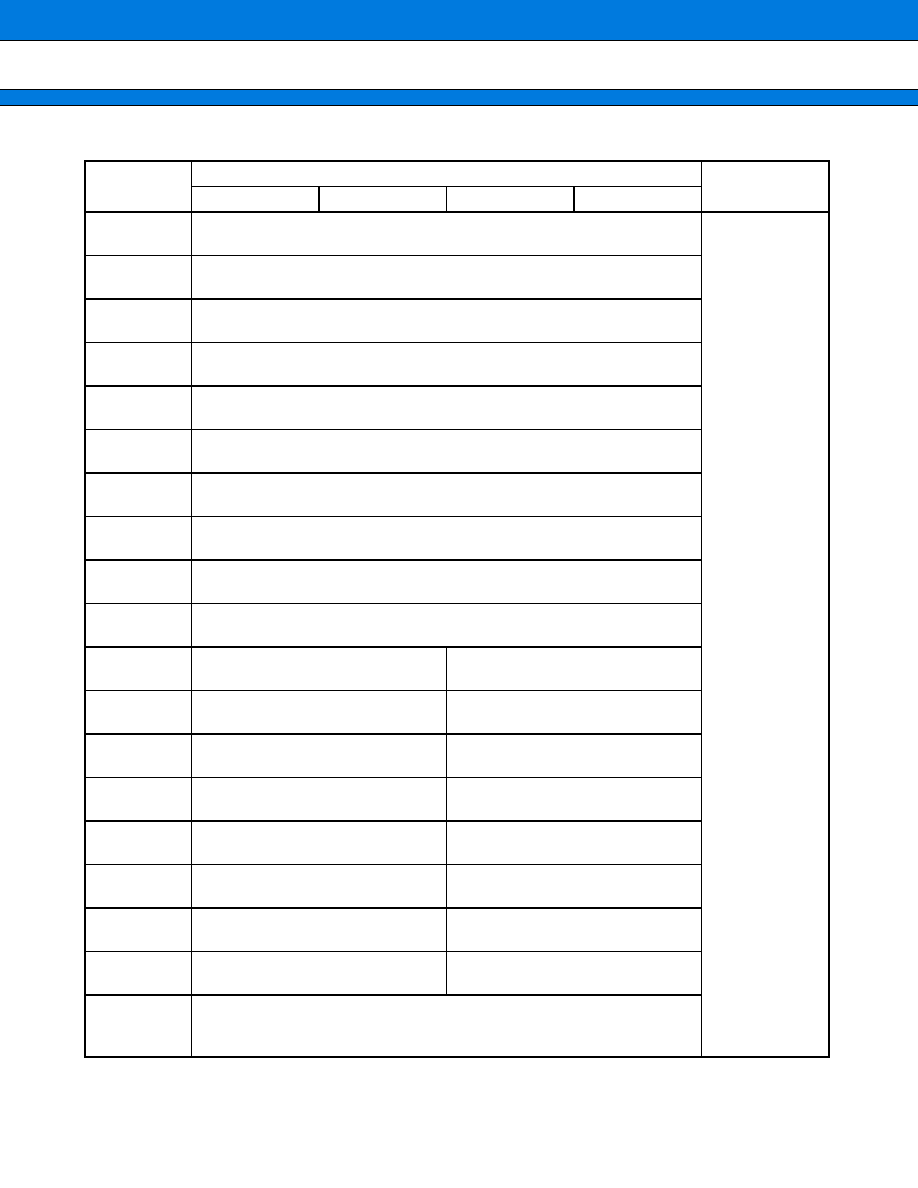

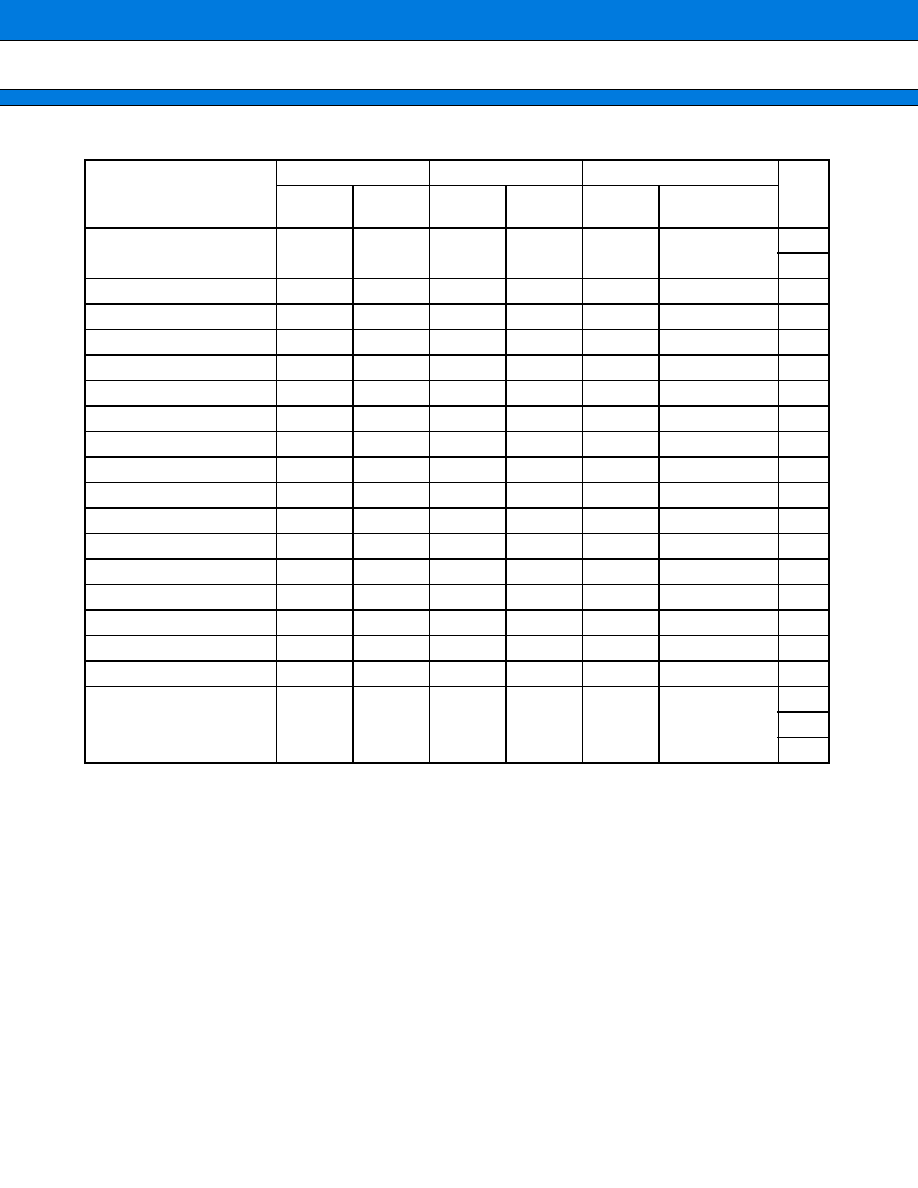

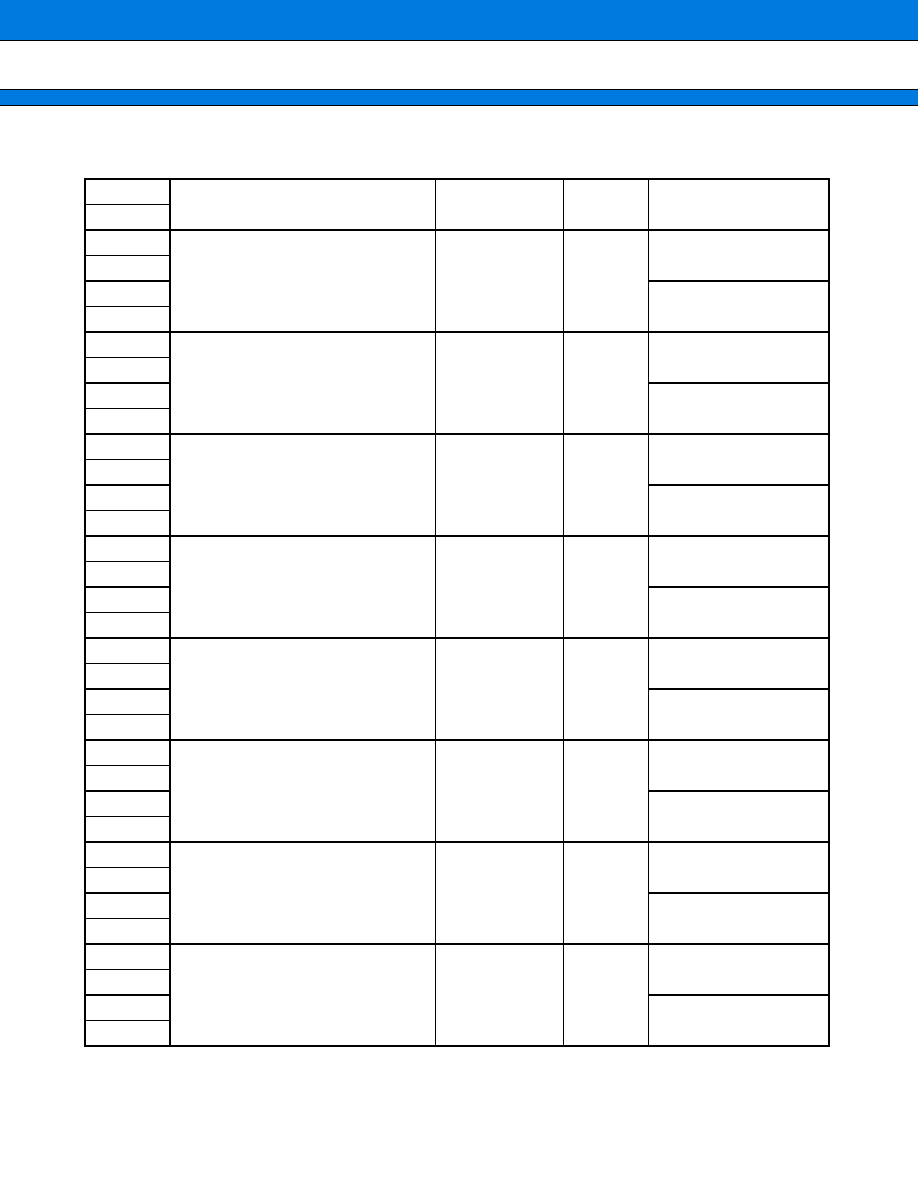

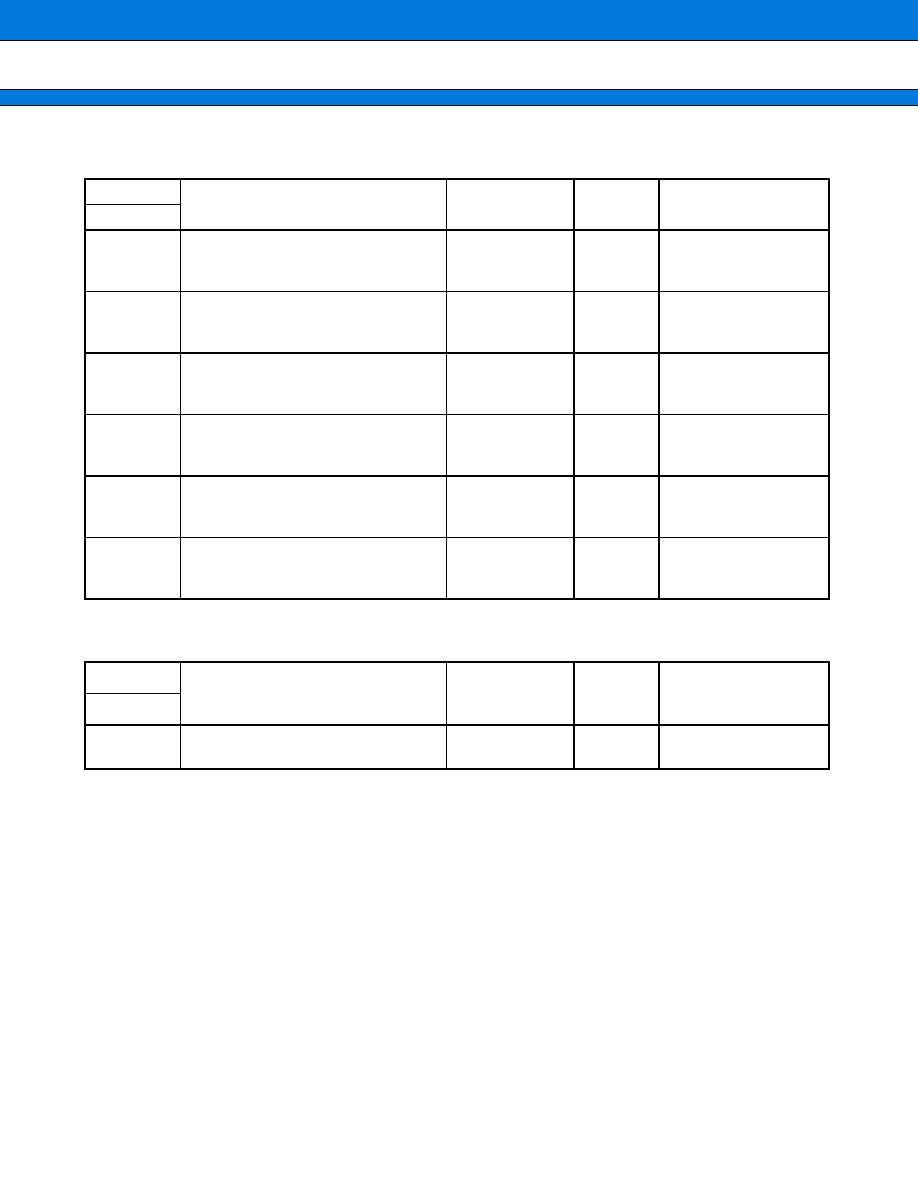

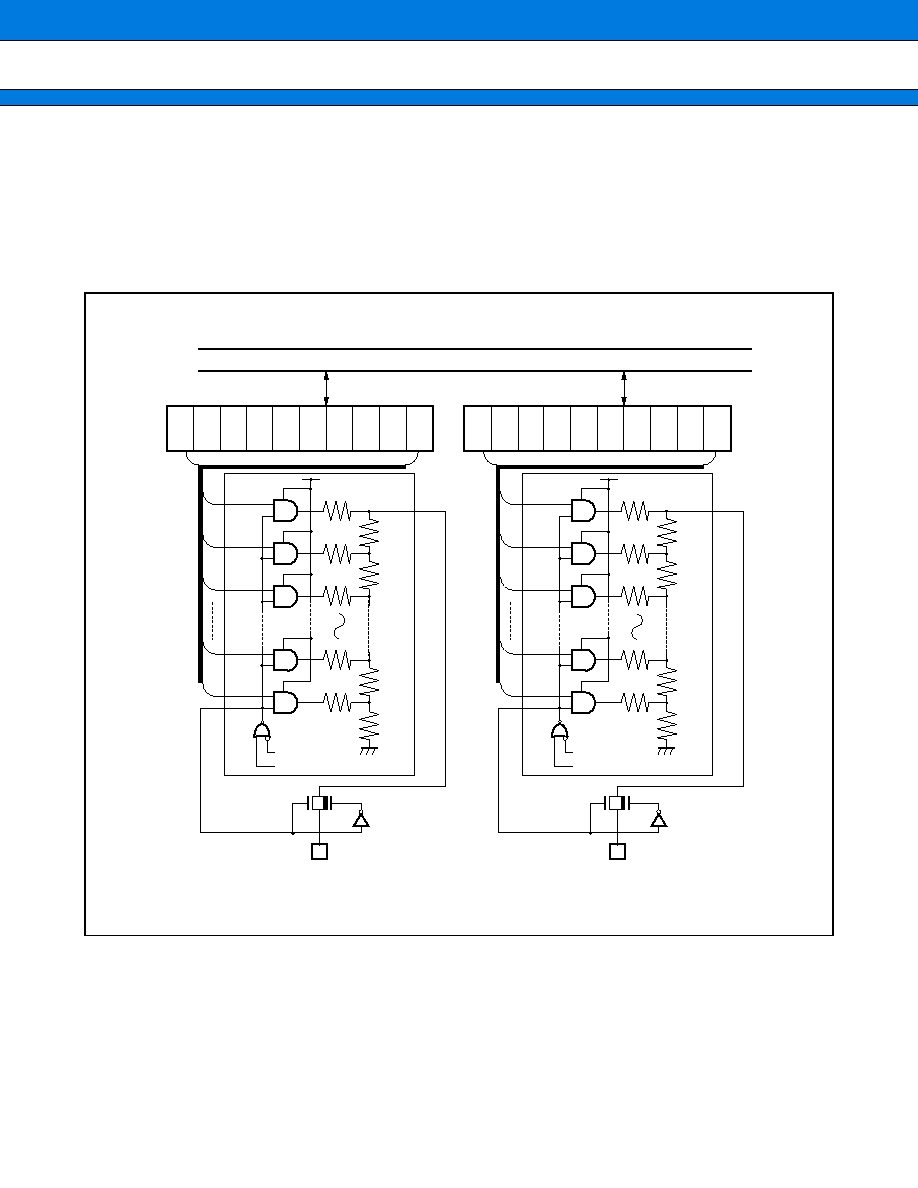

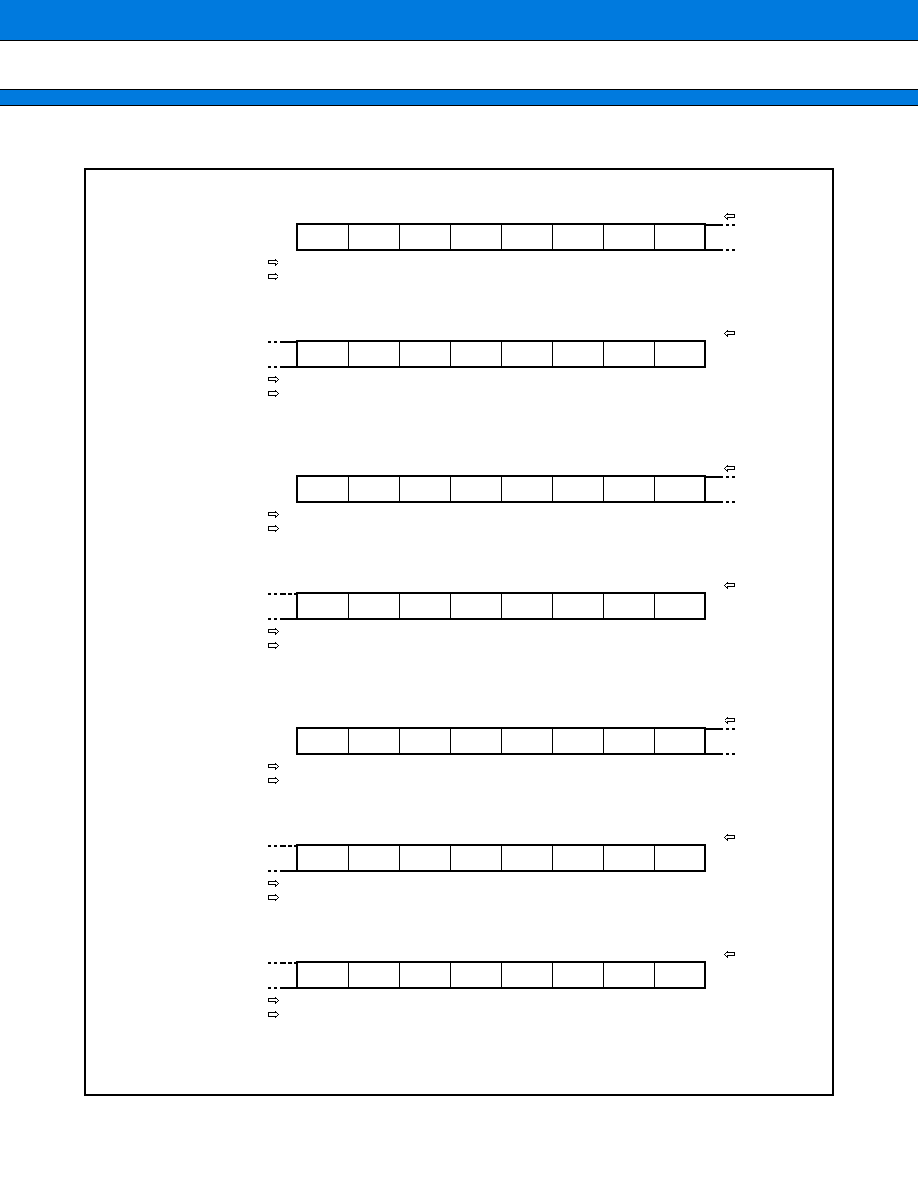

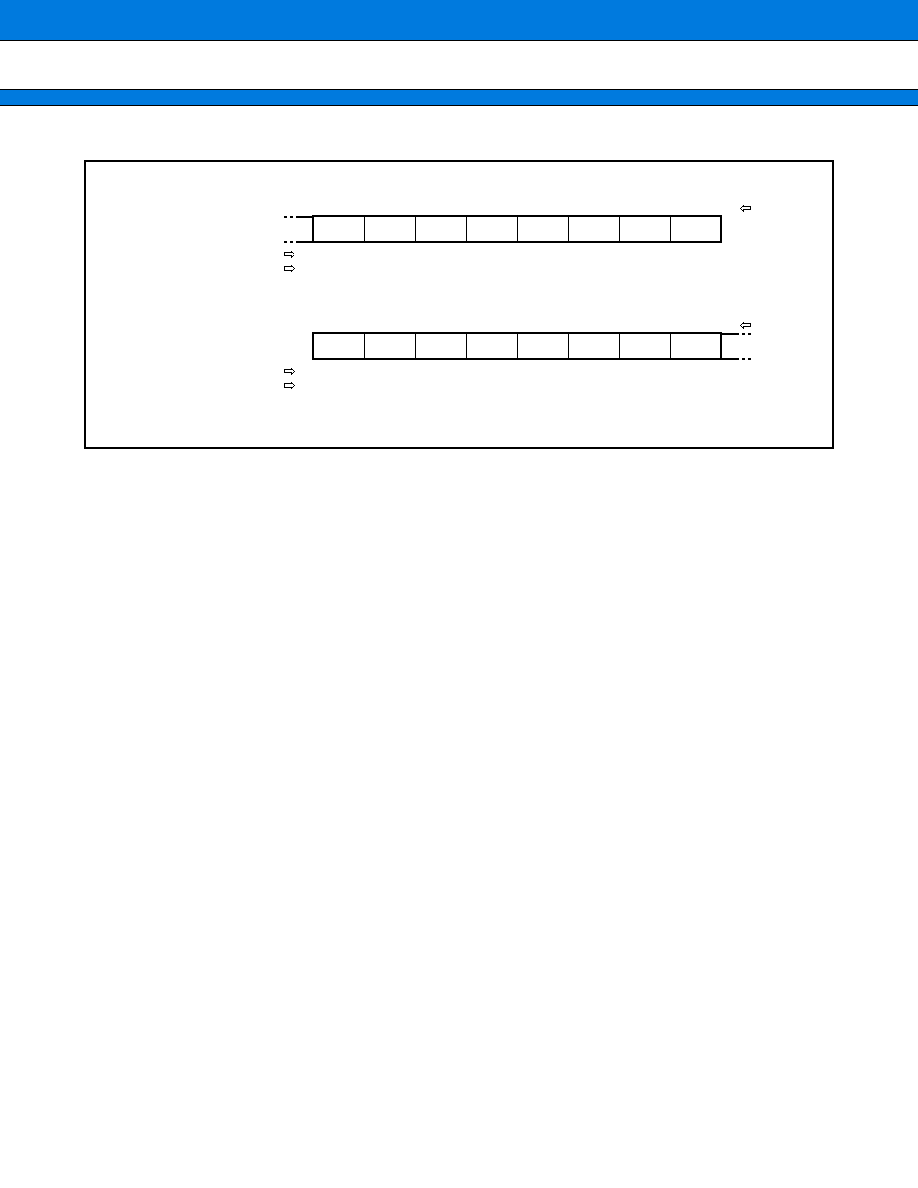

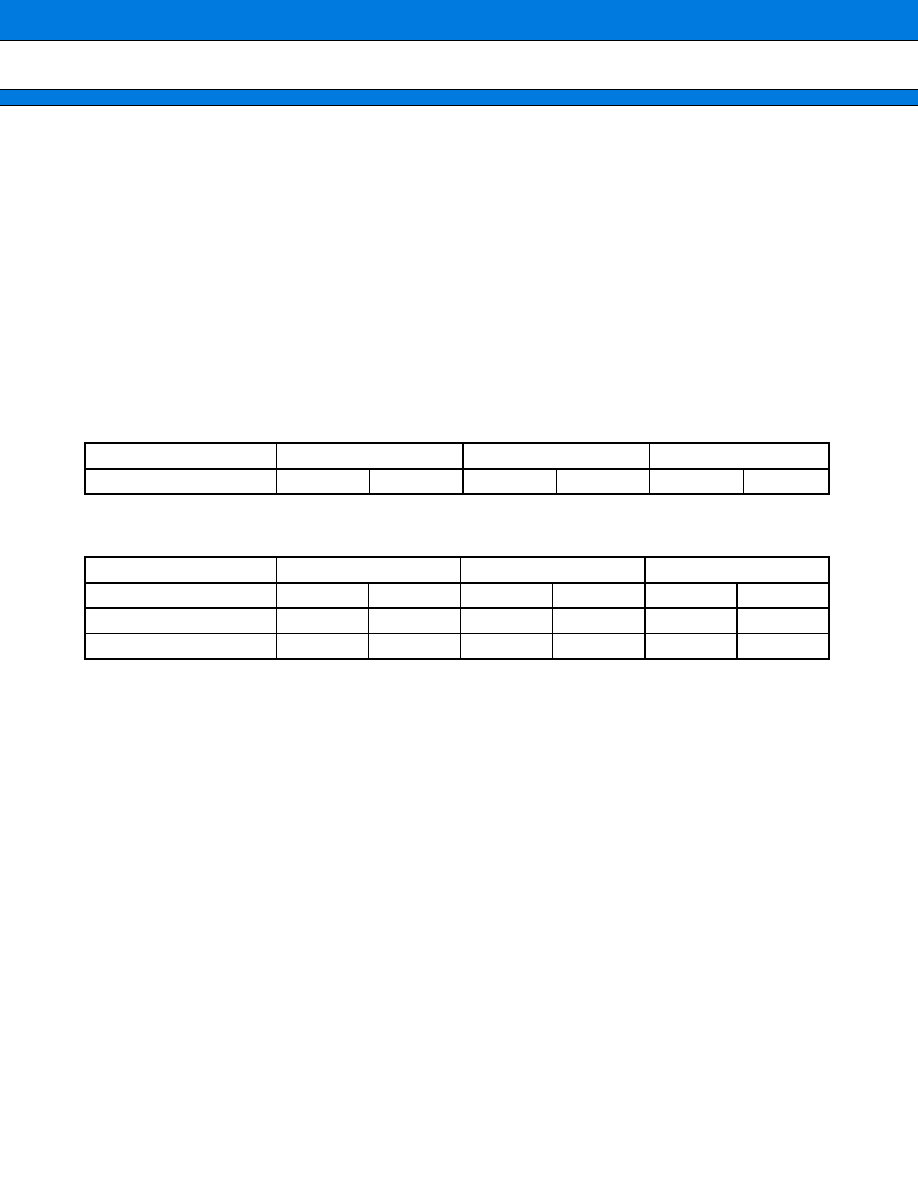

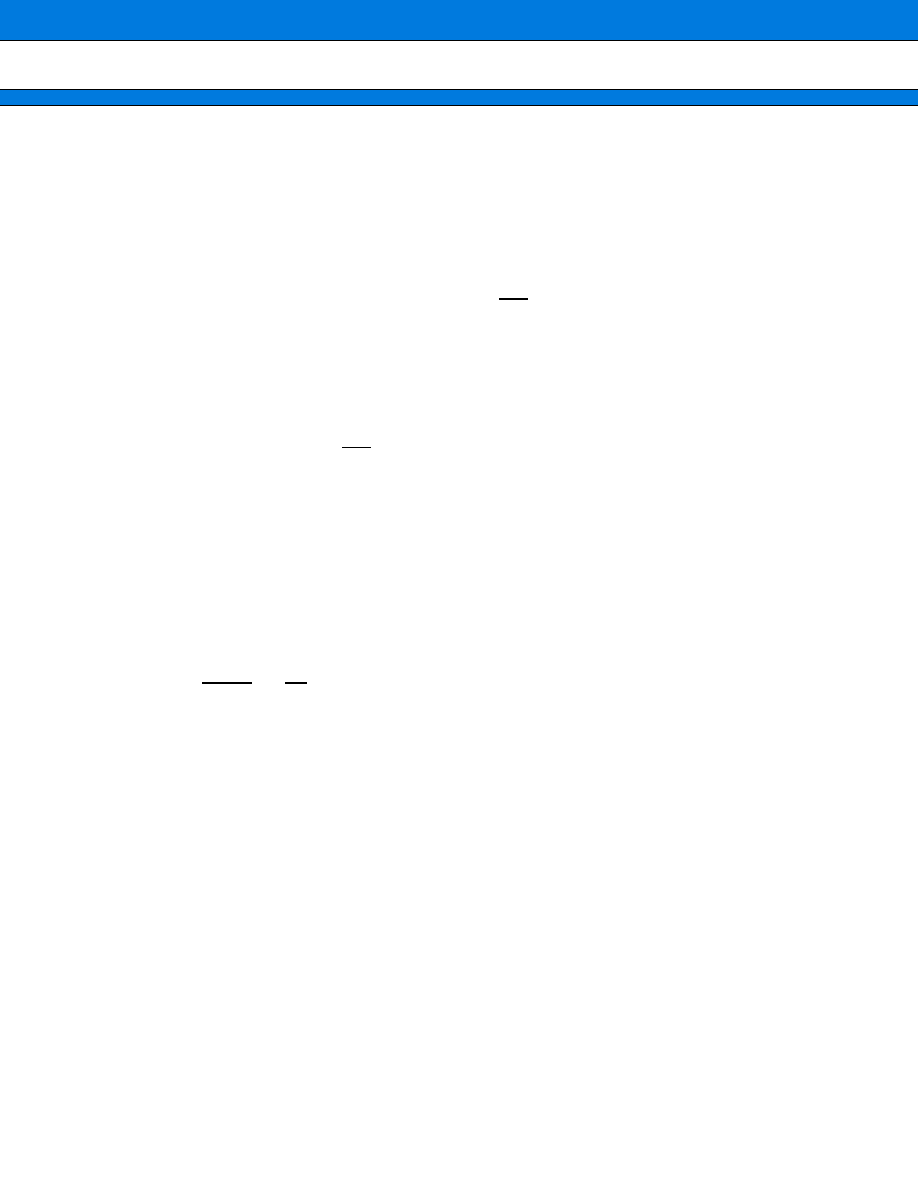

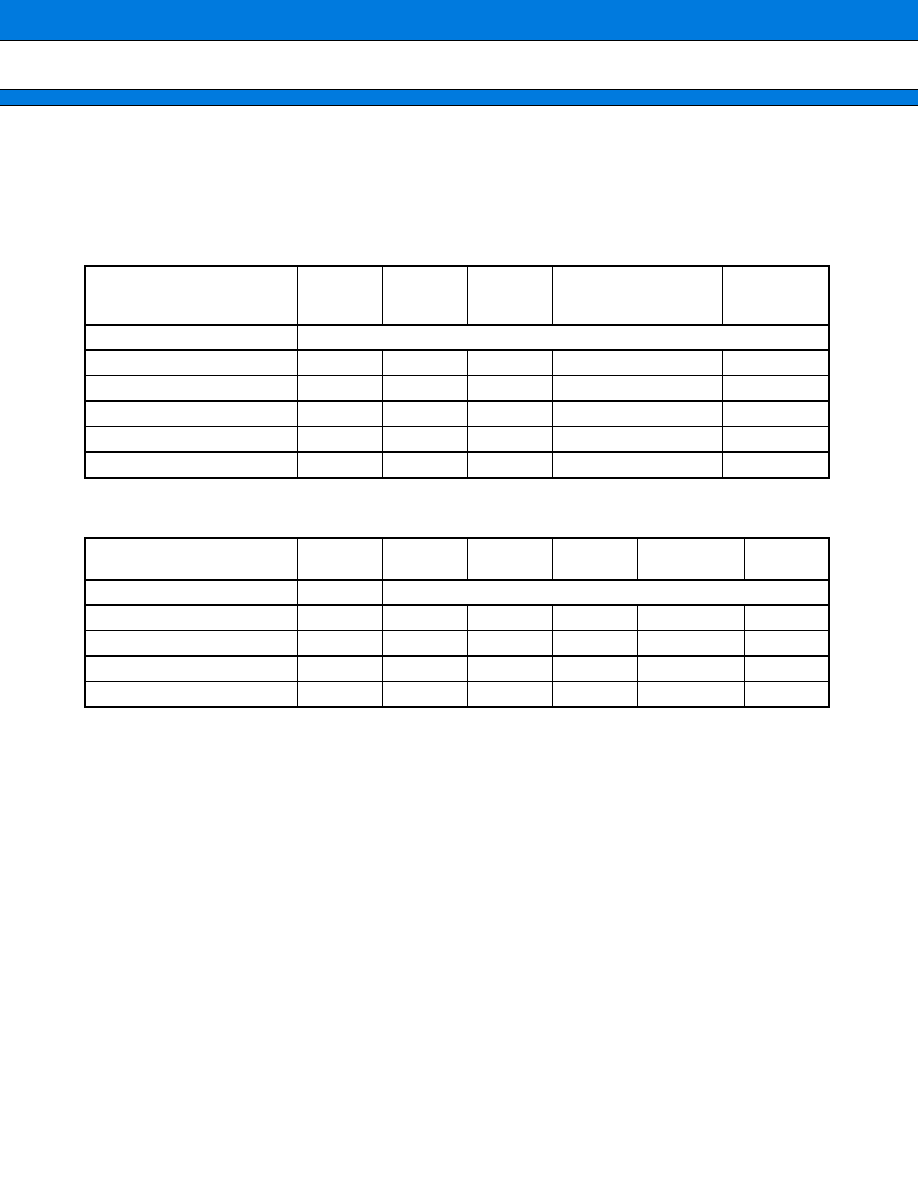

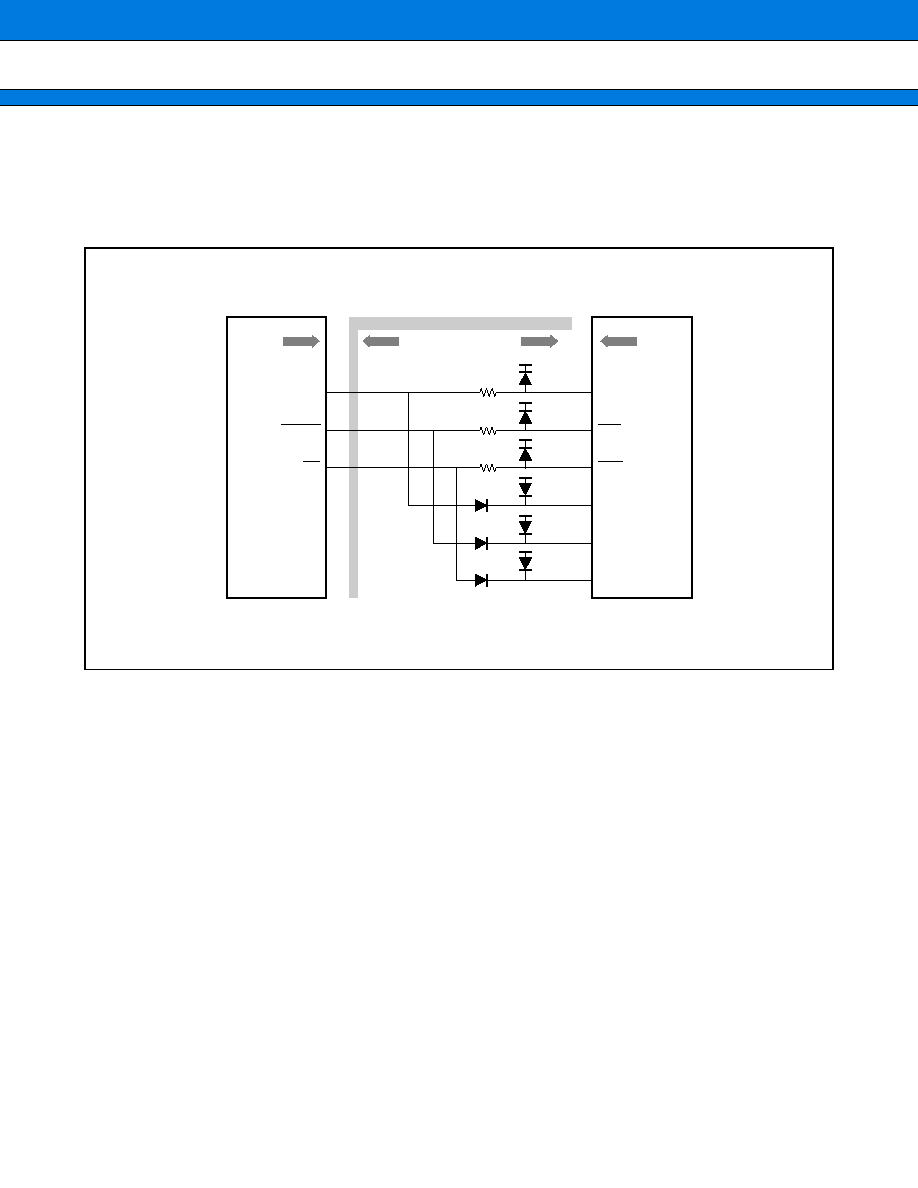

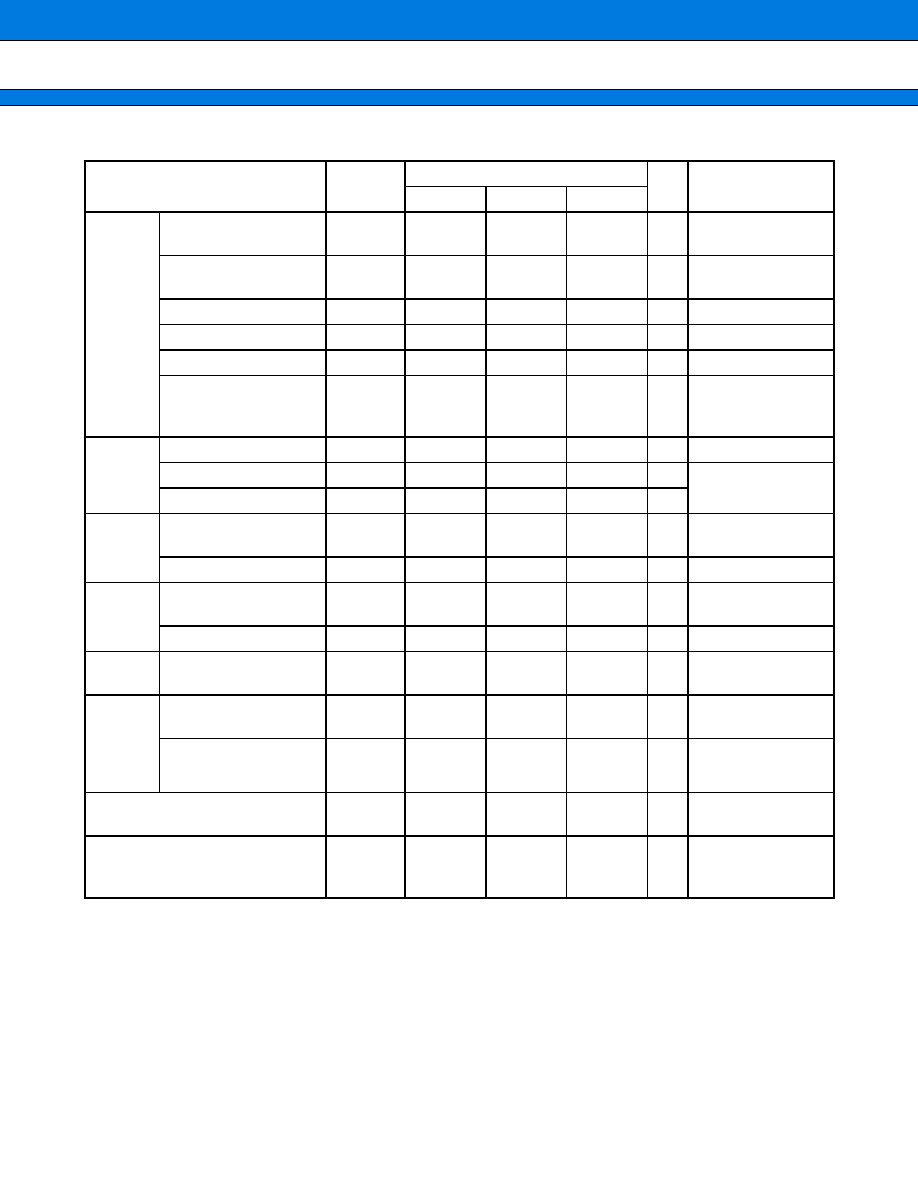

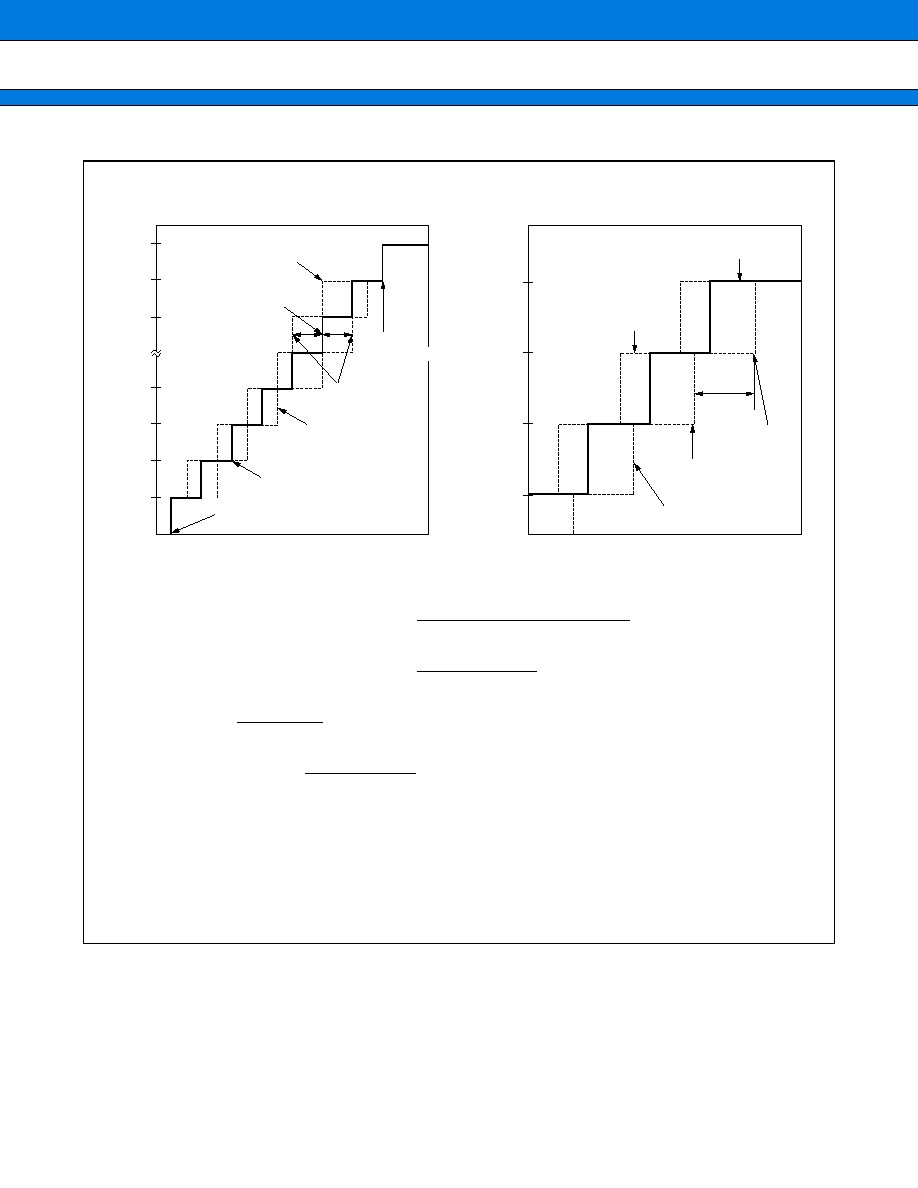

s

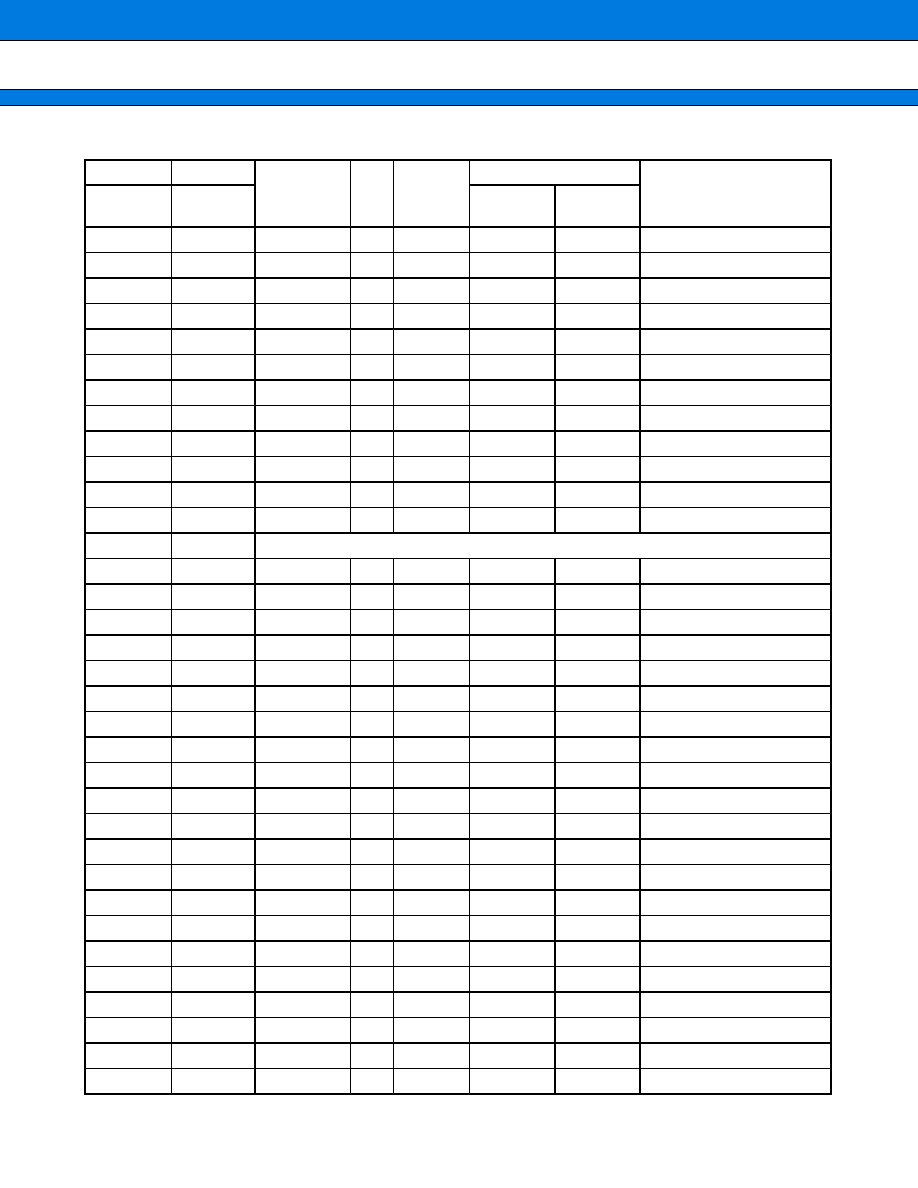

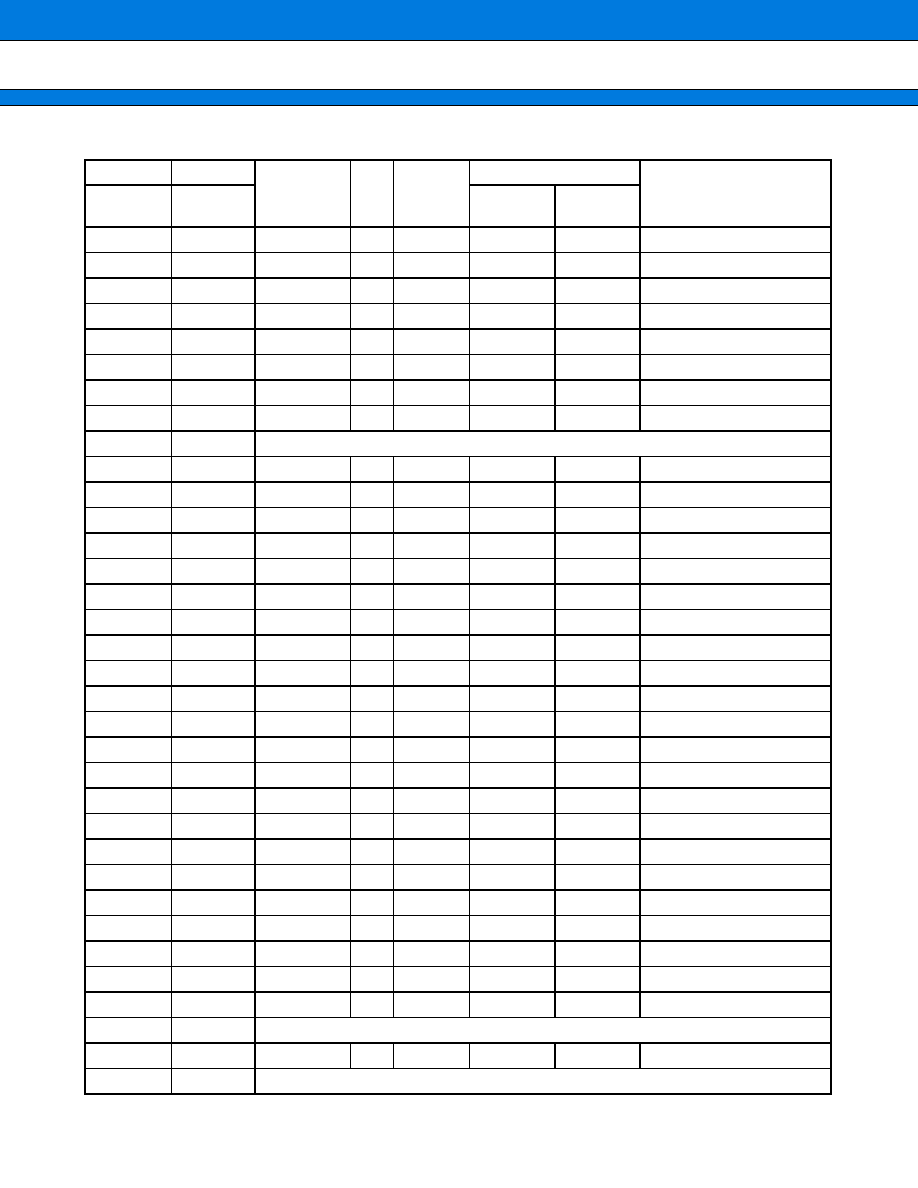

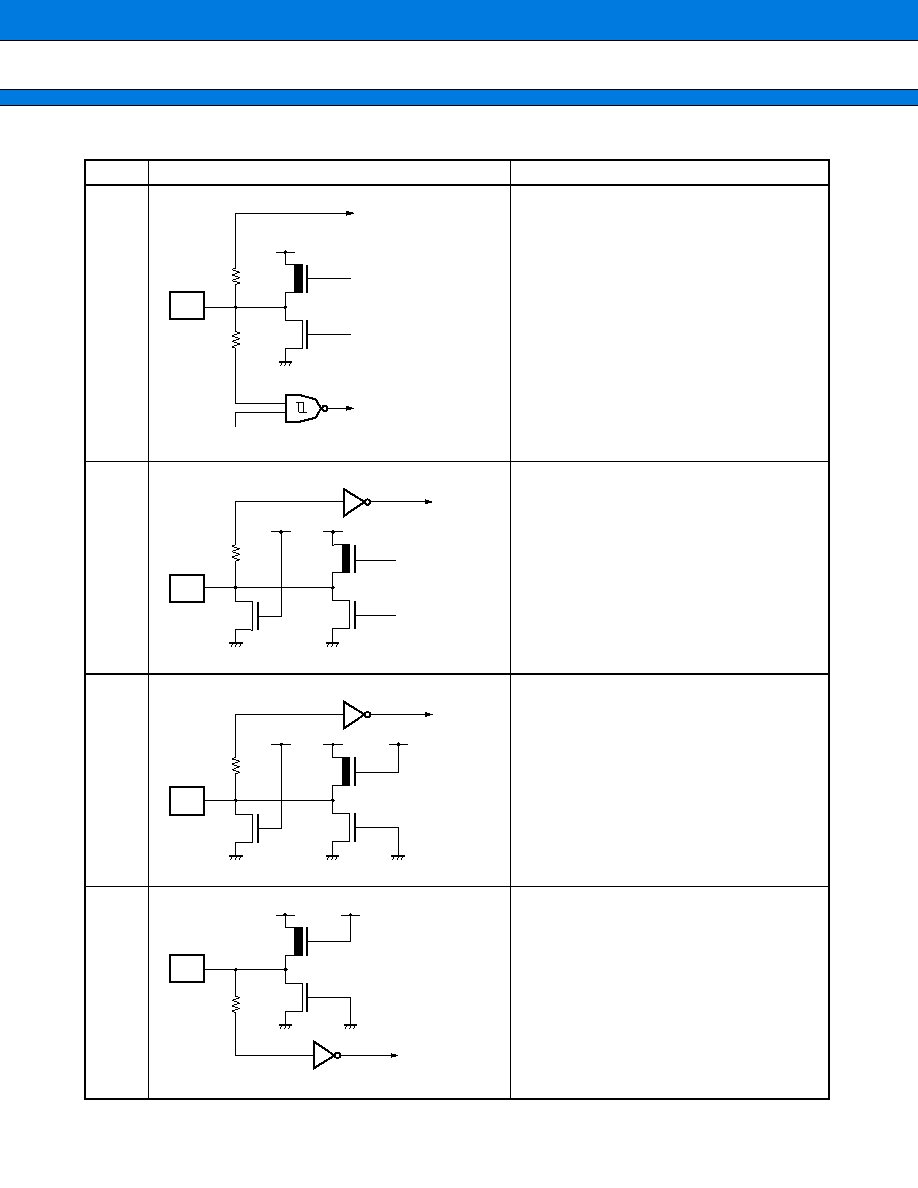

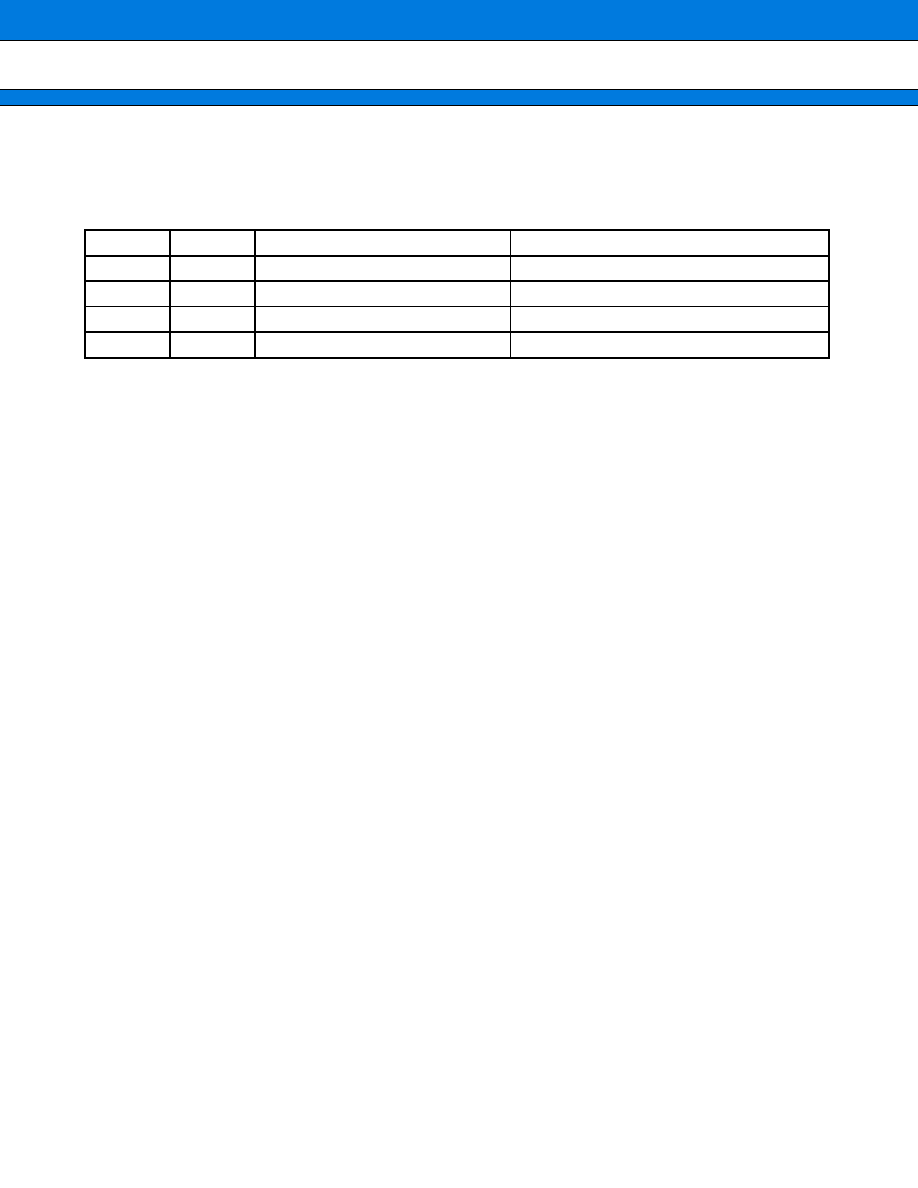

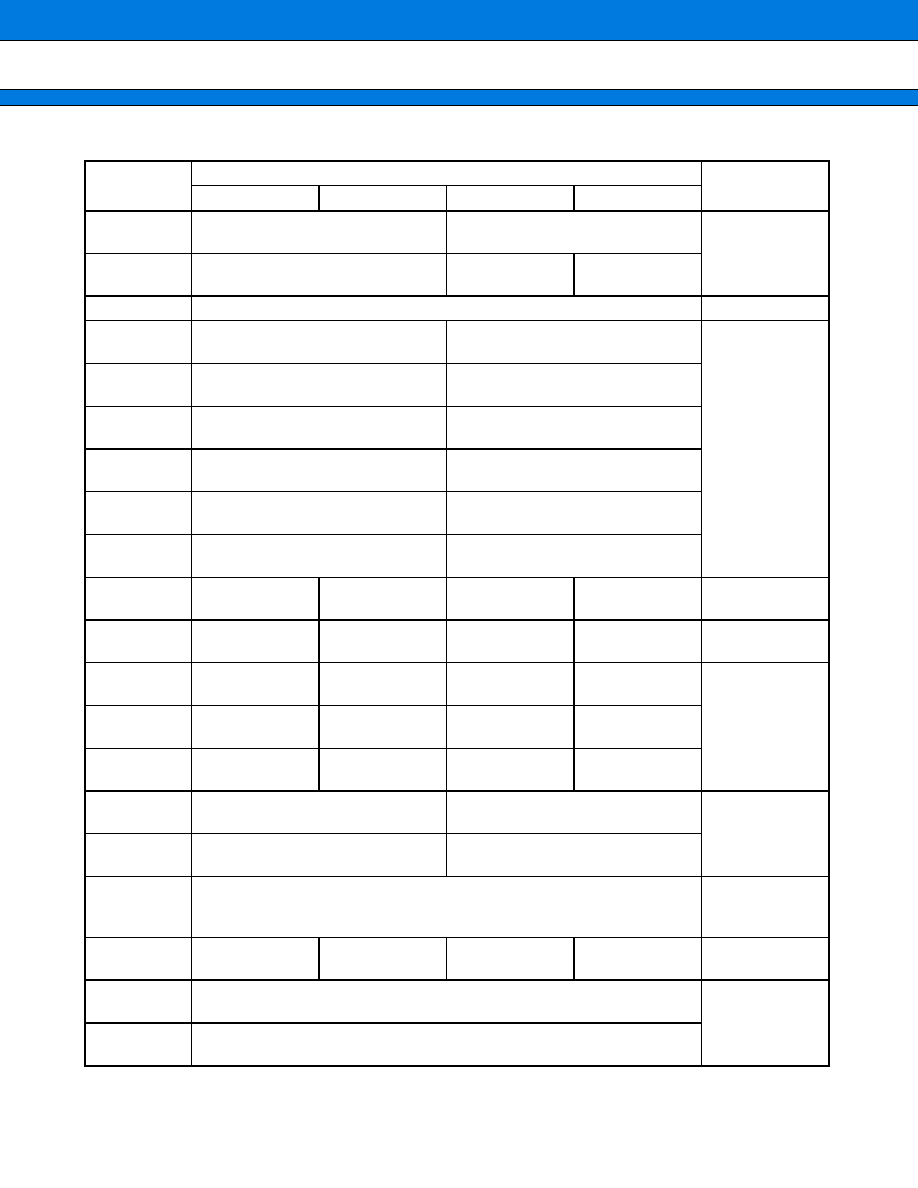

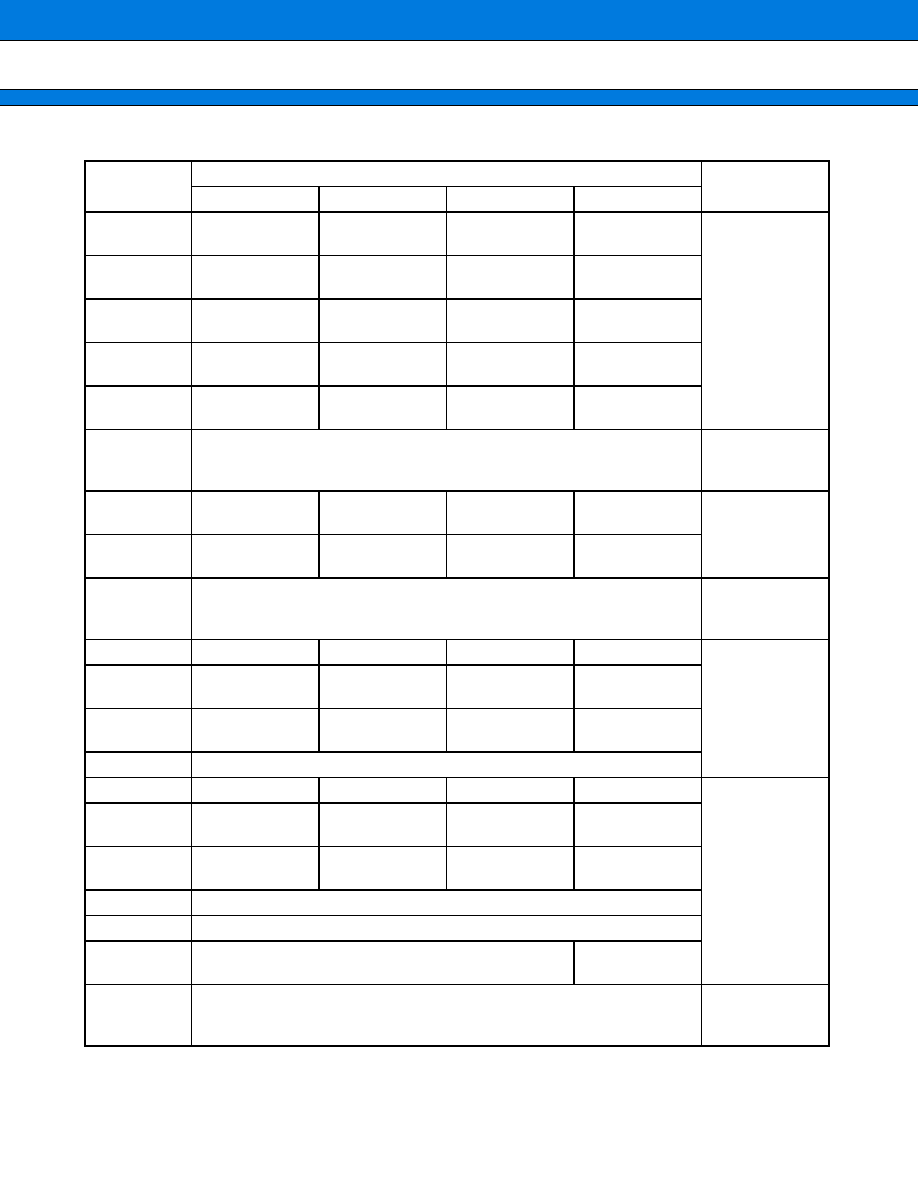

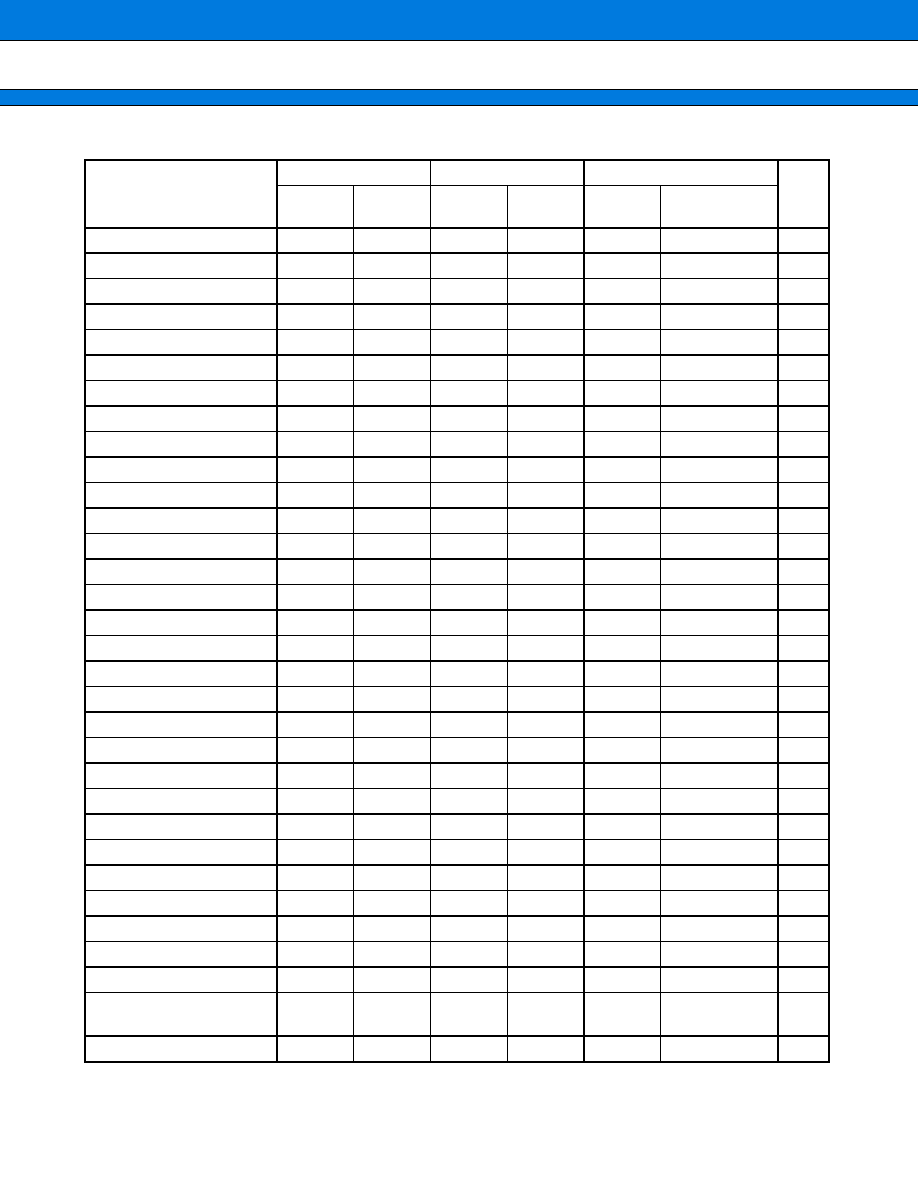

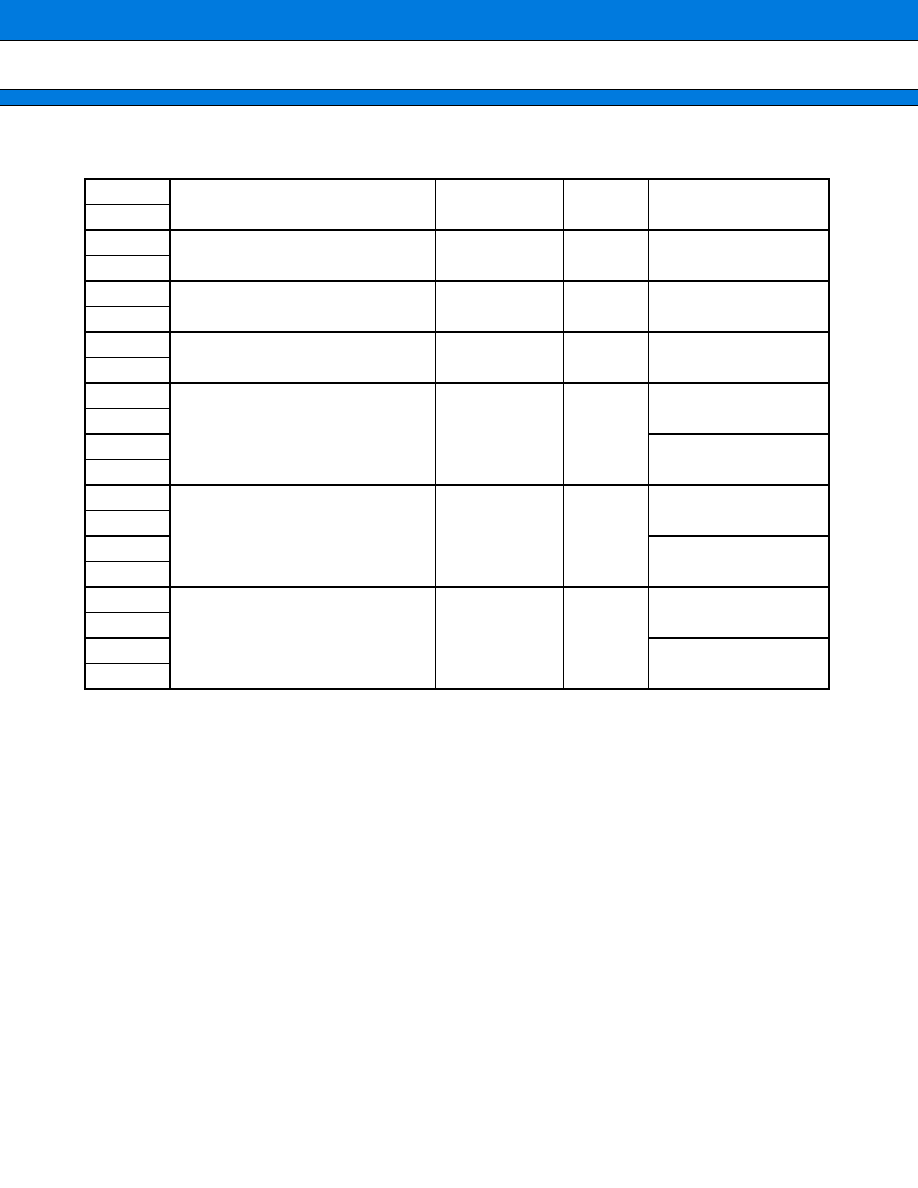

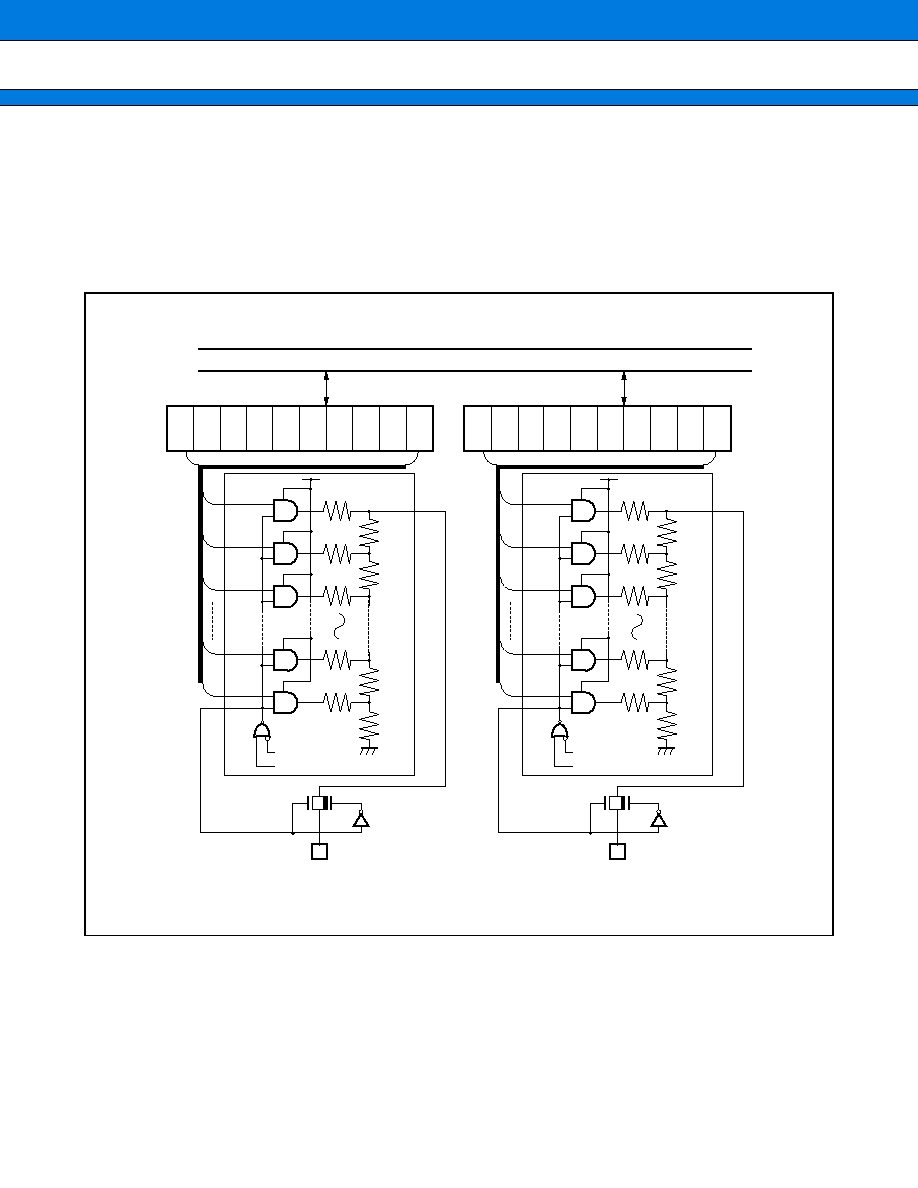

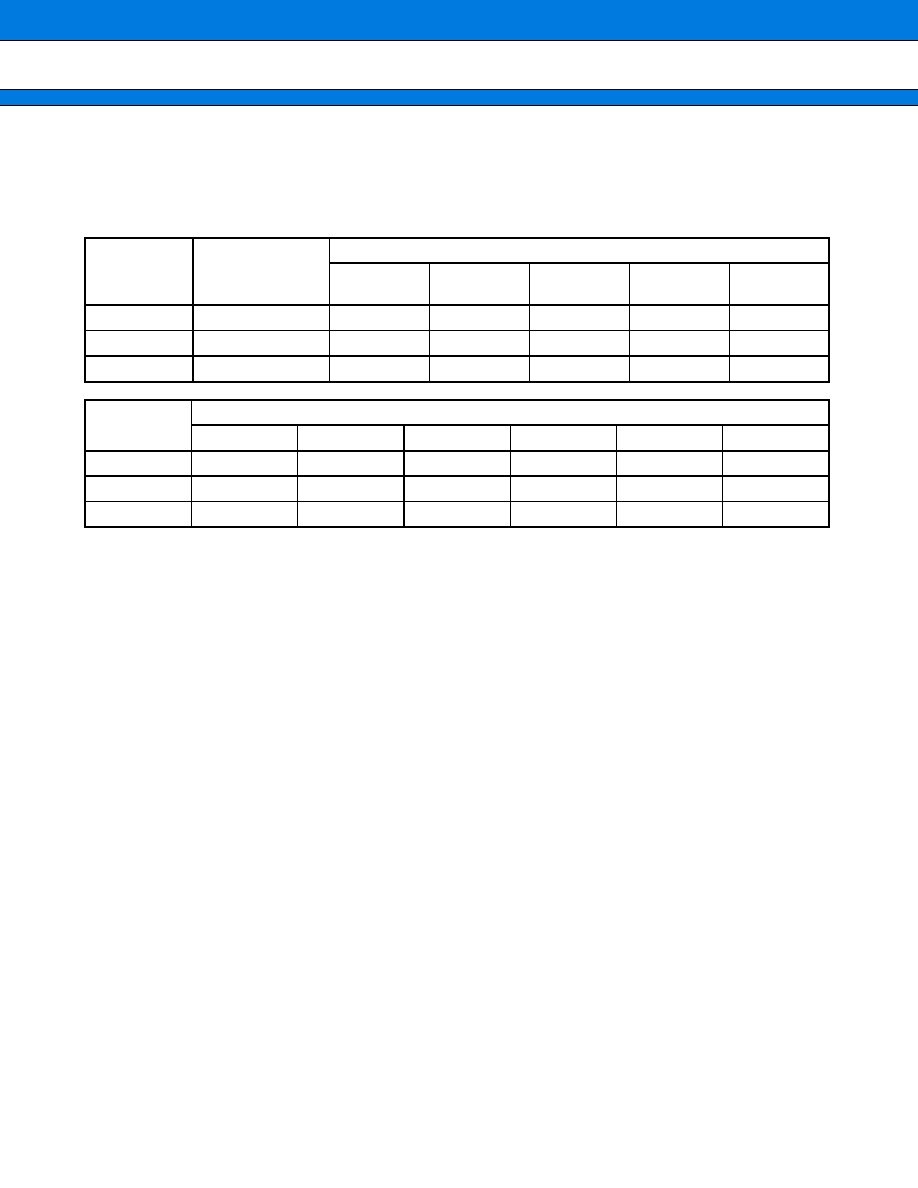

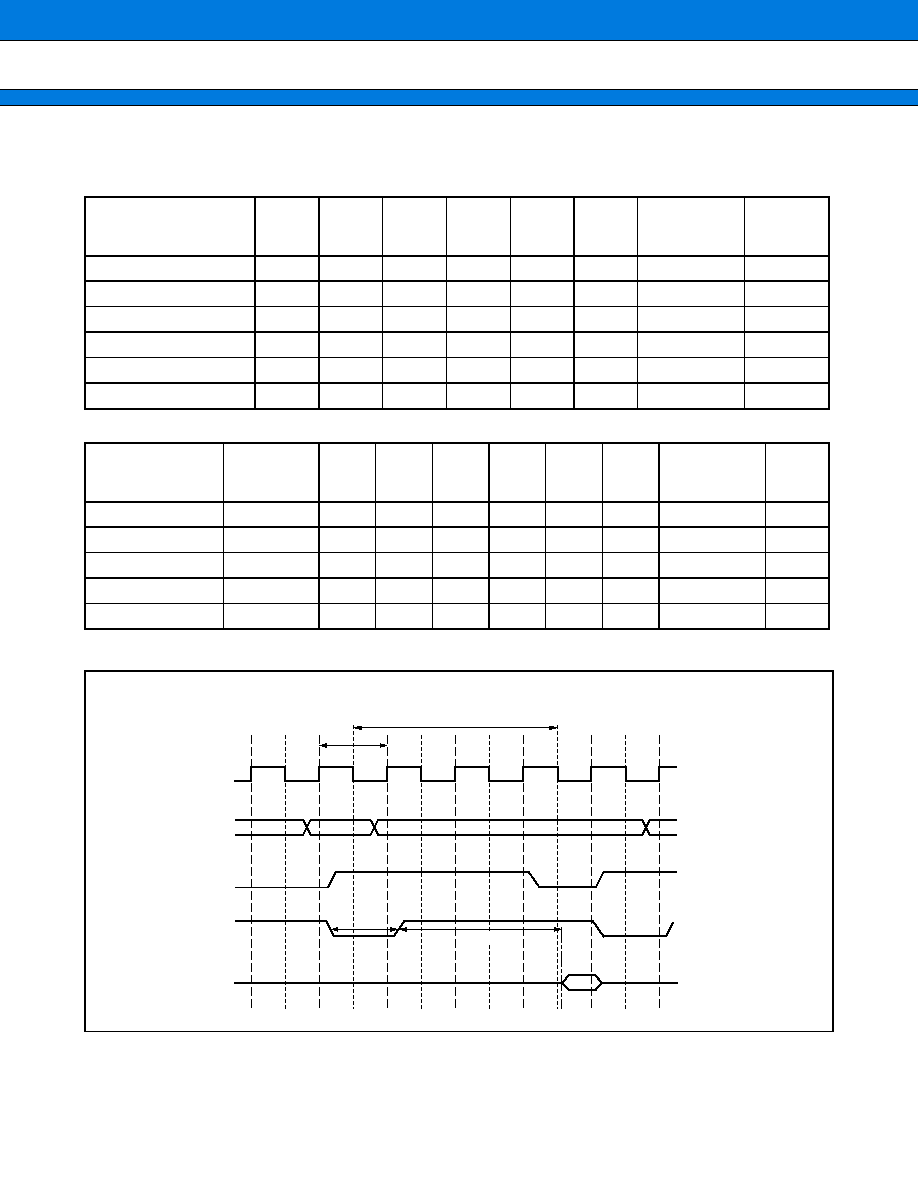

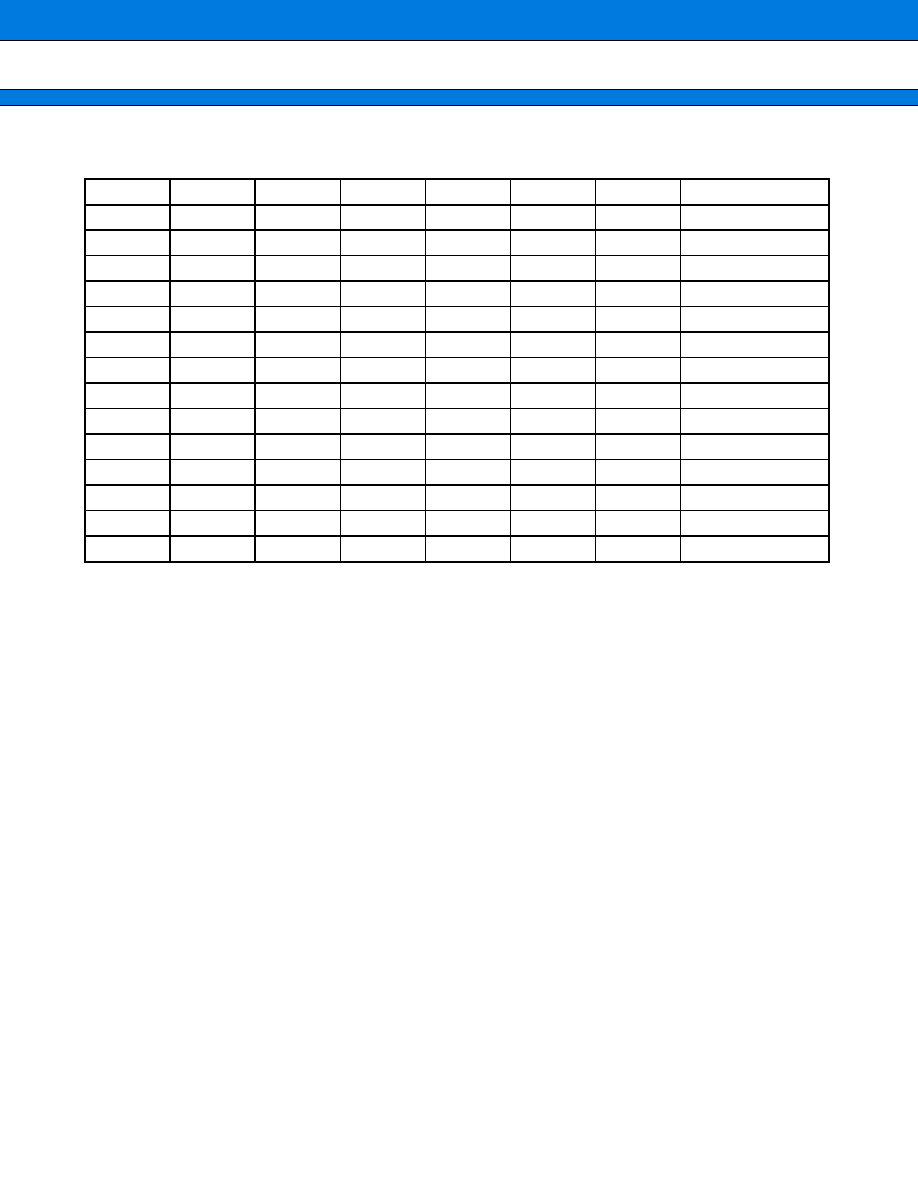

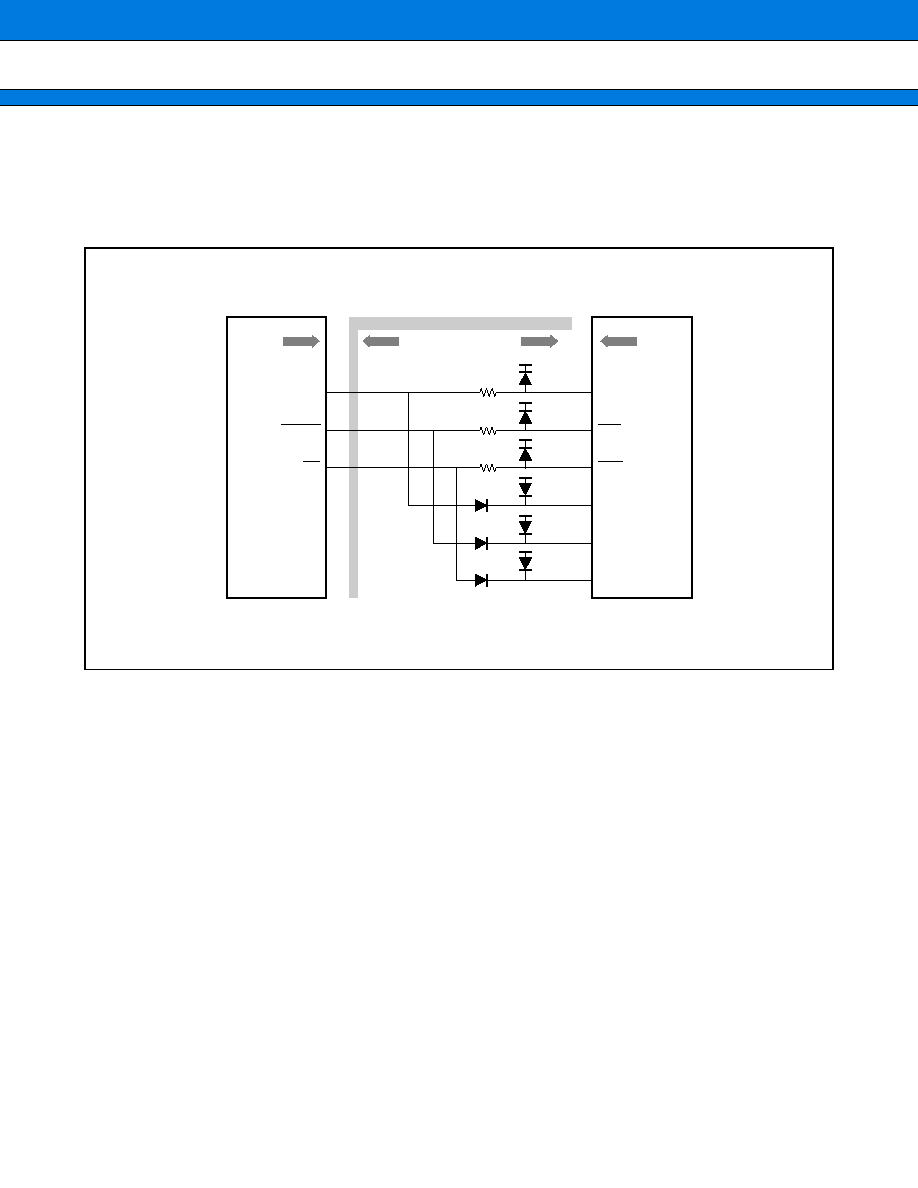

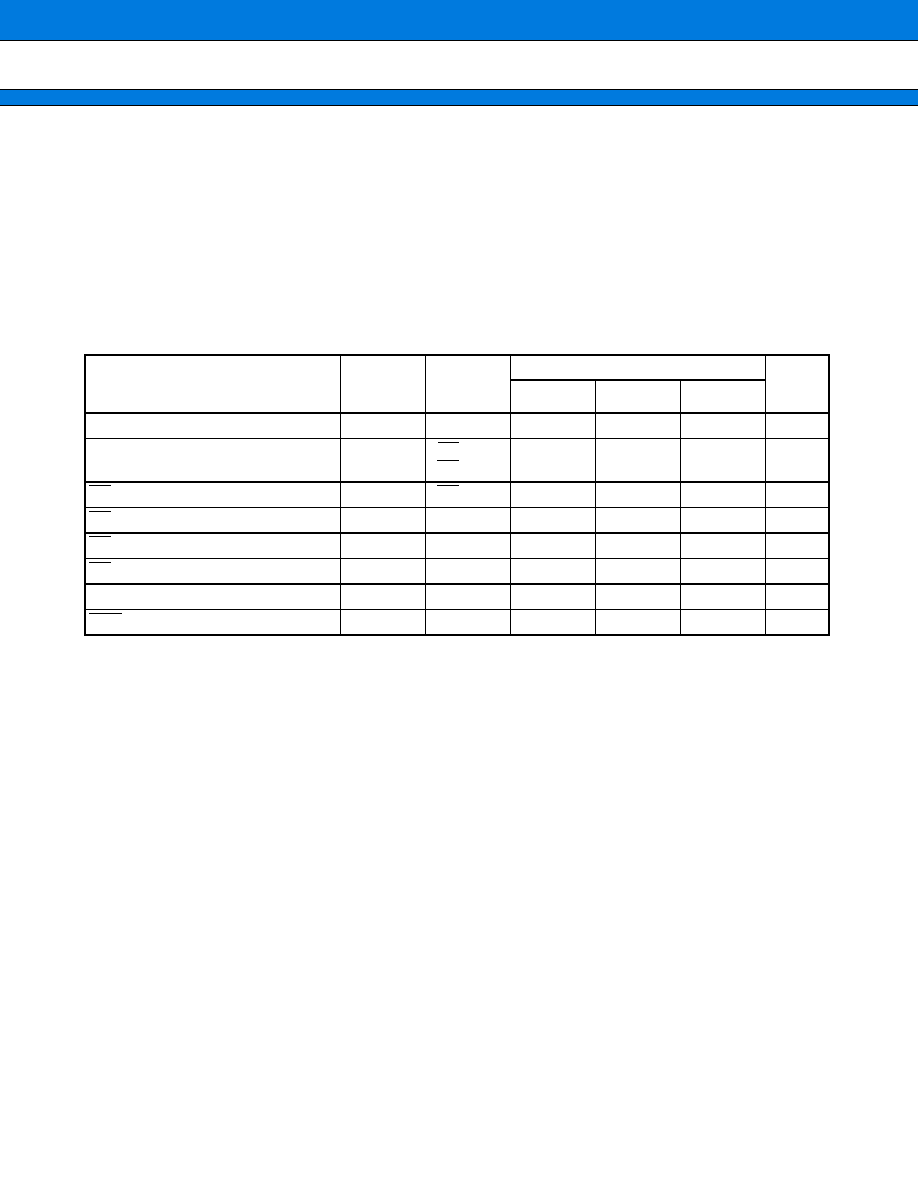

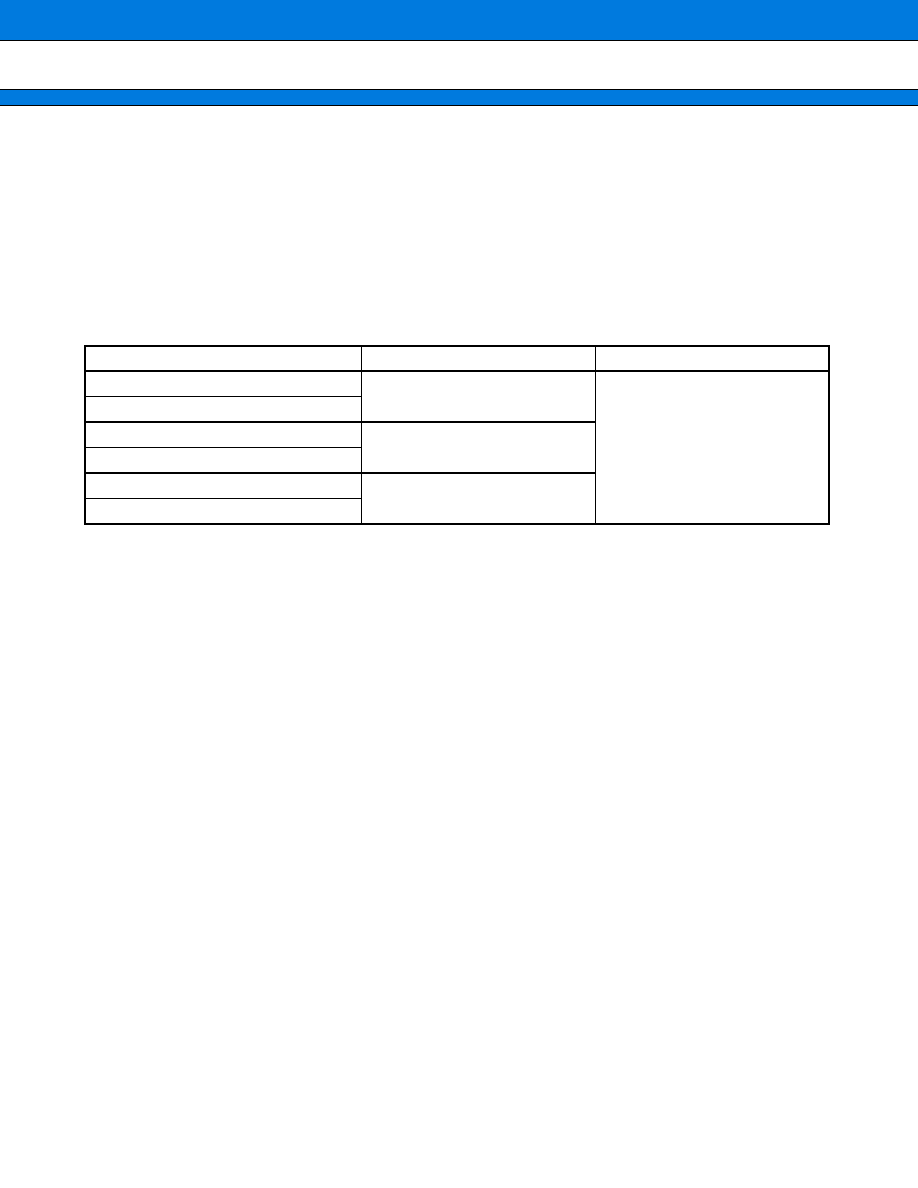

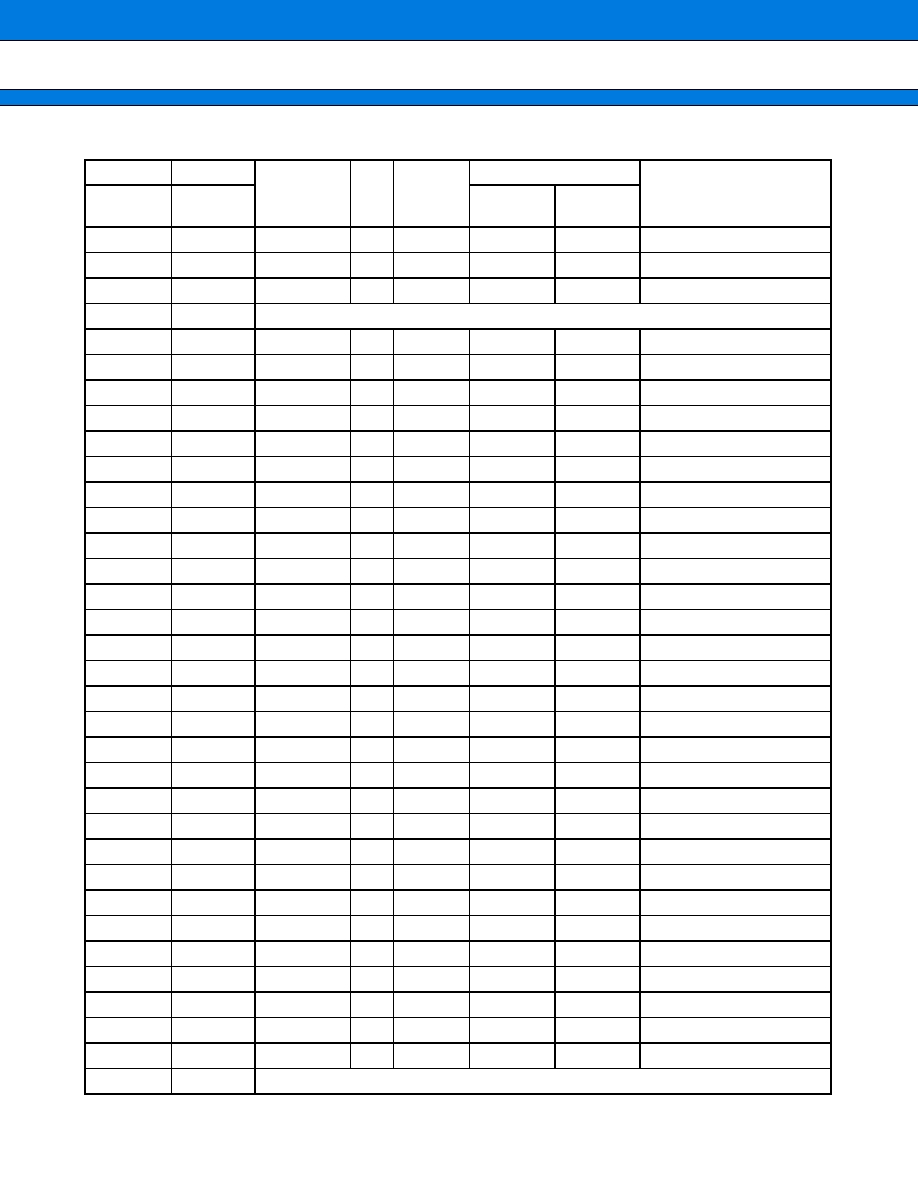

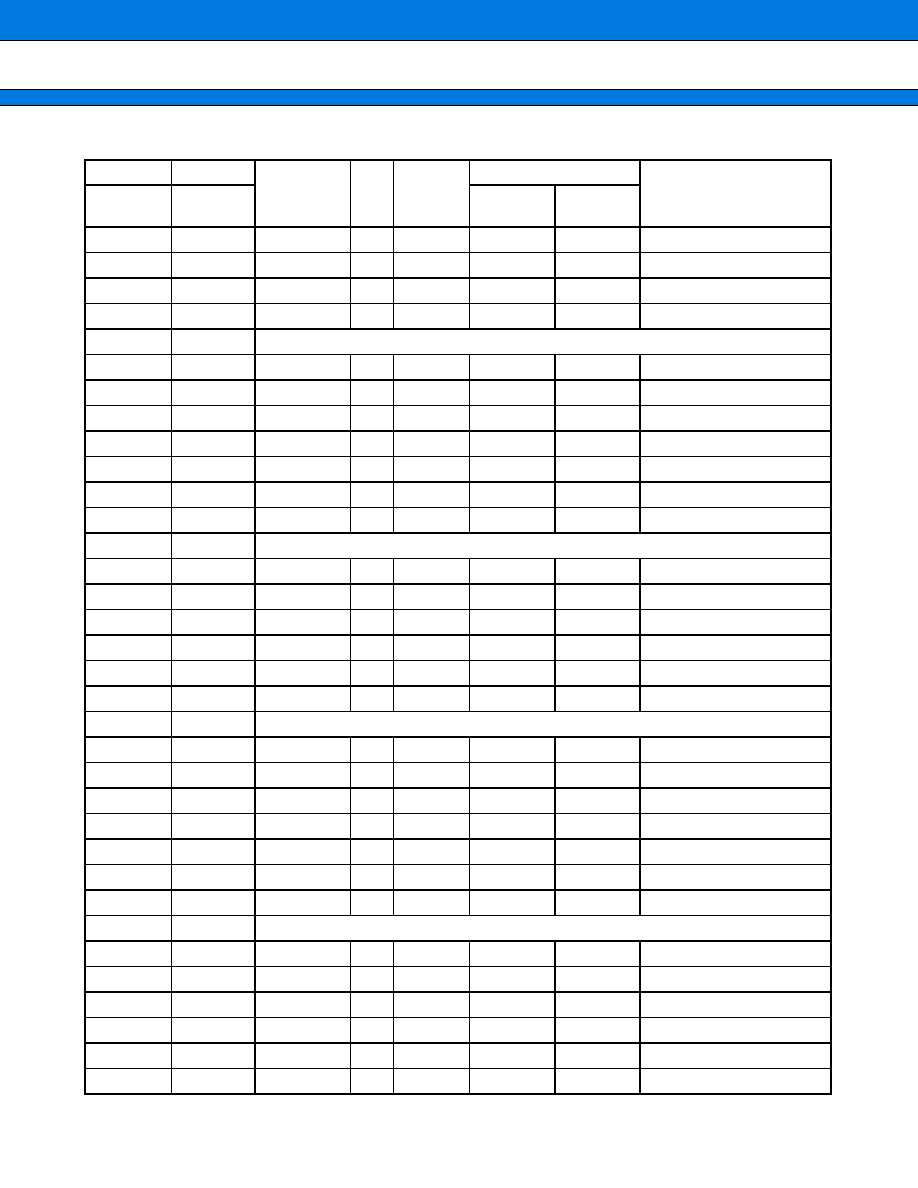

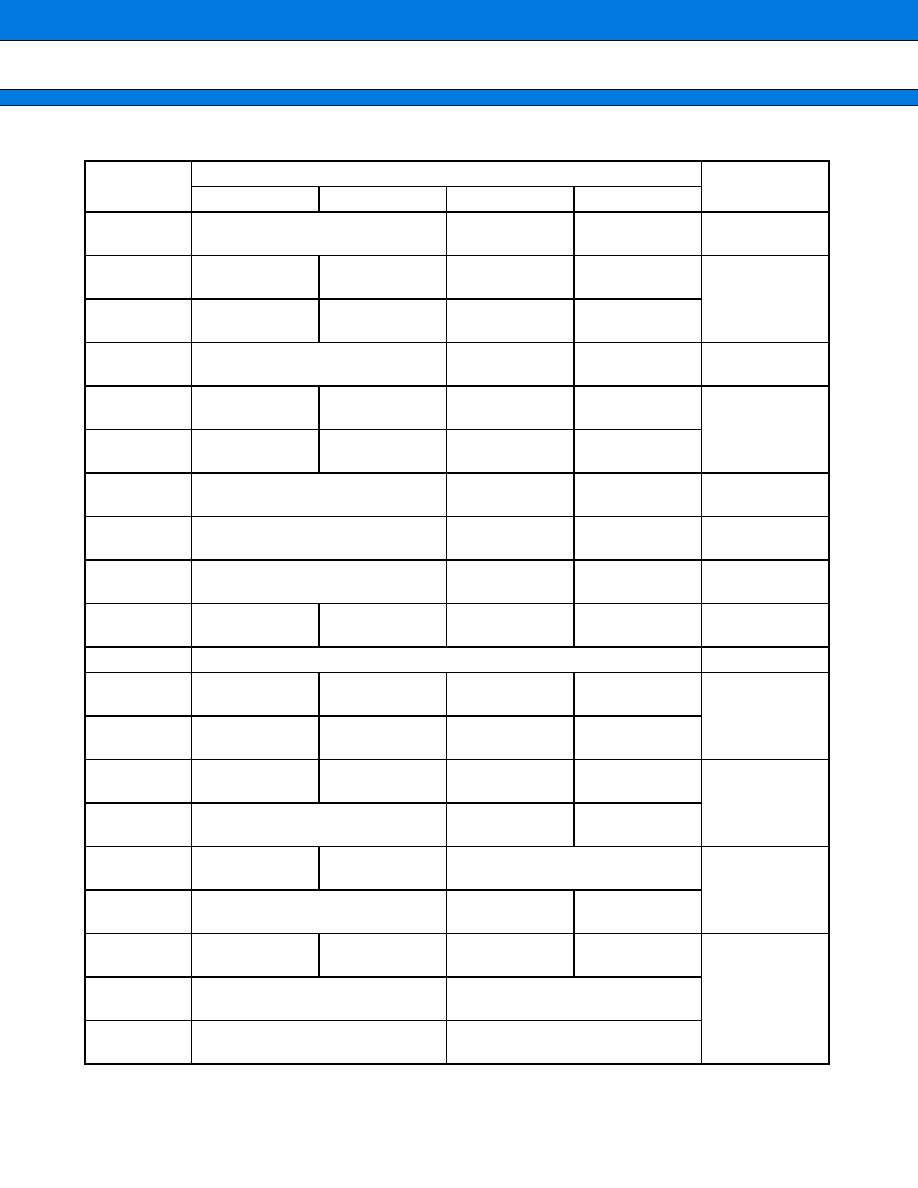

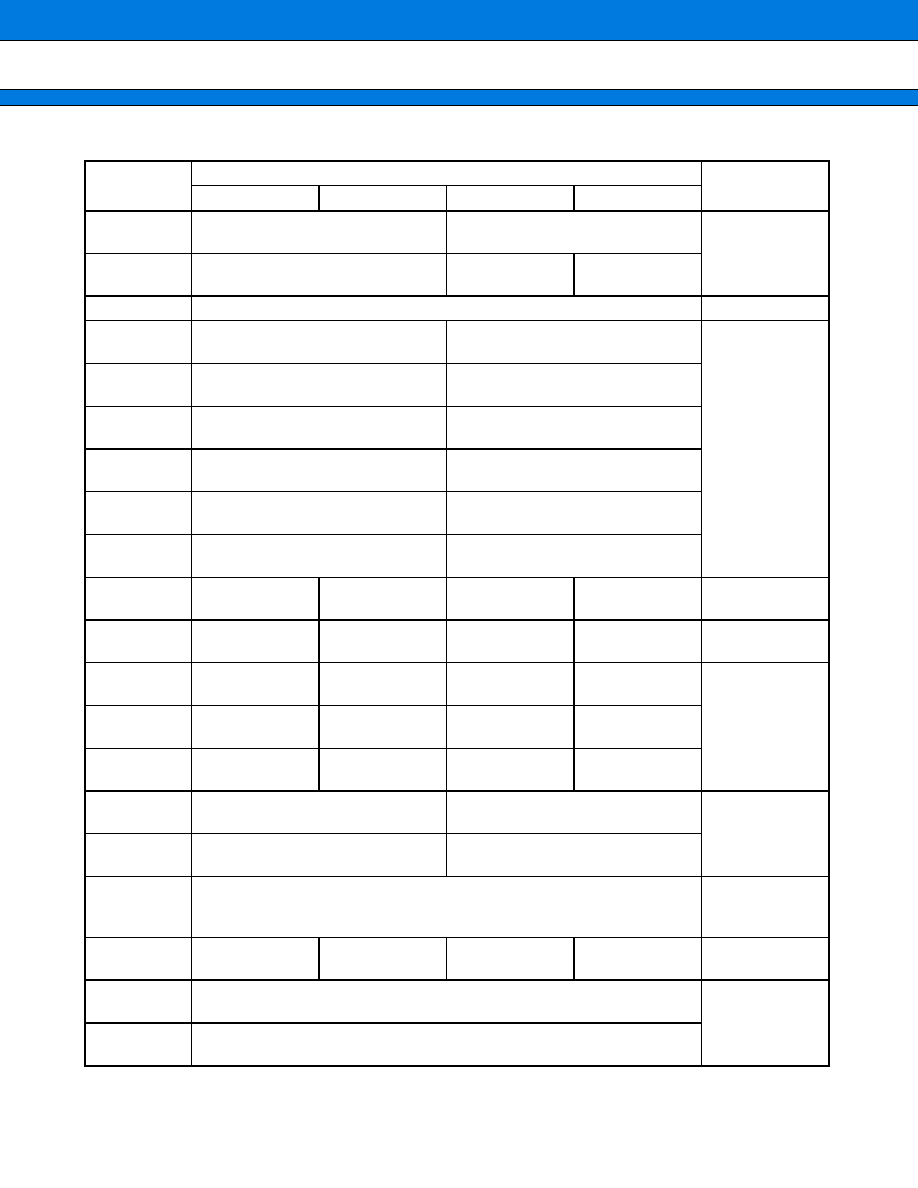

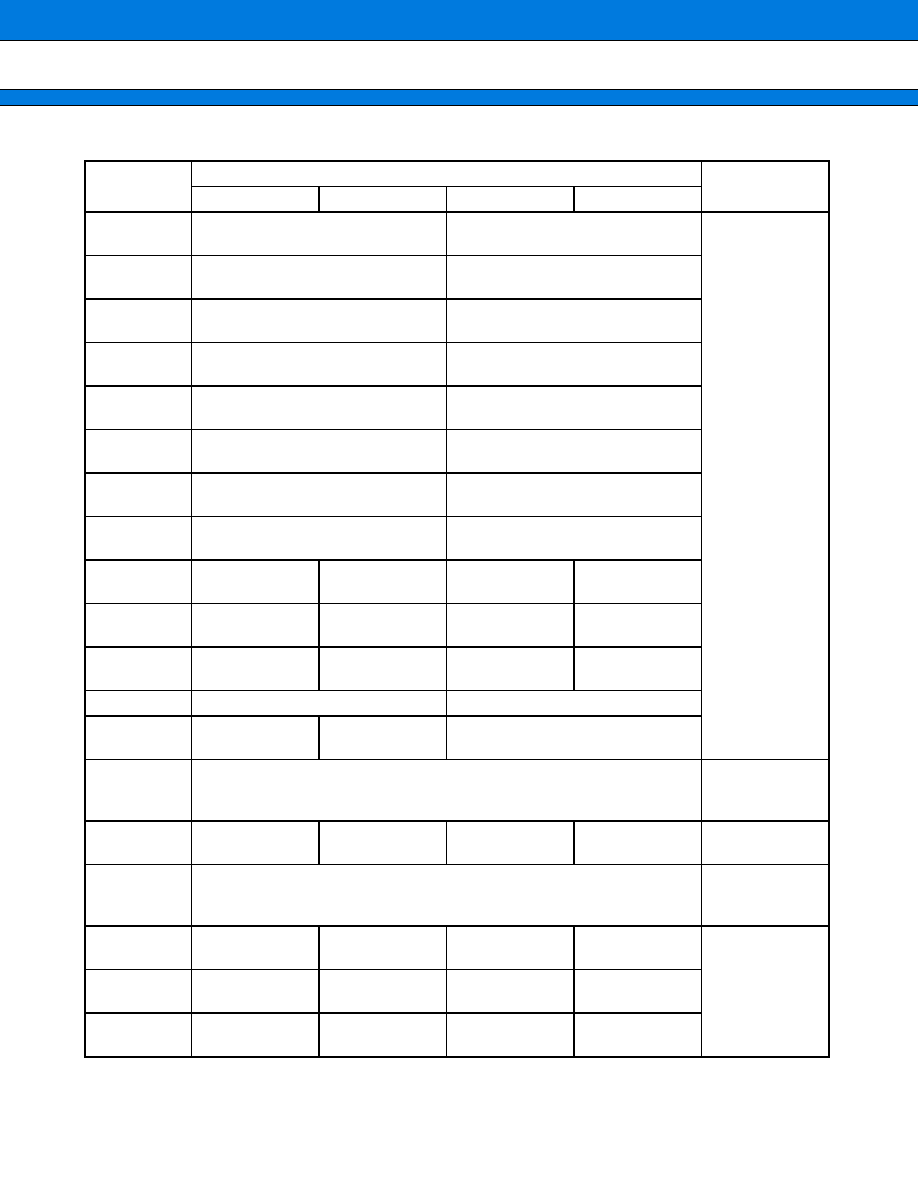

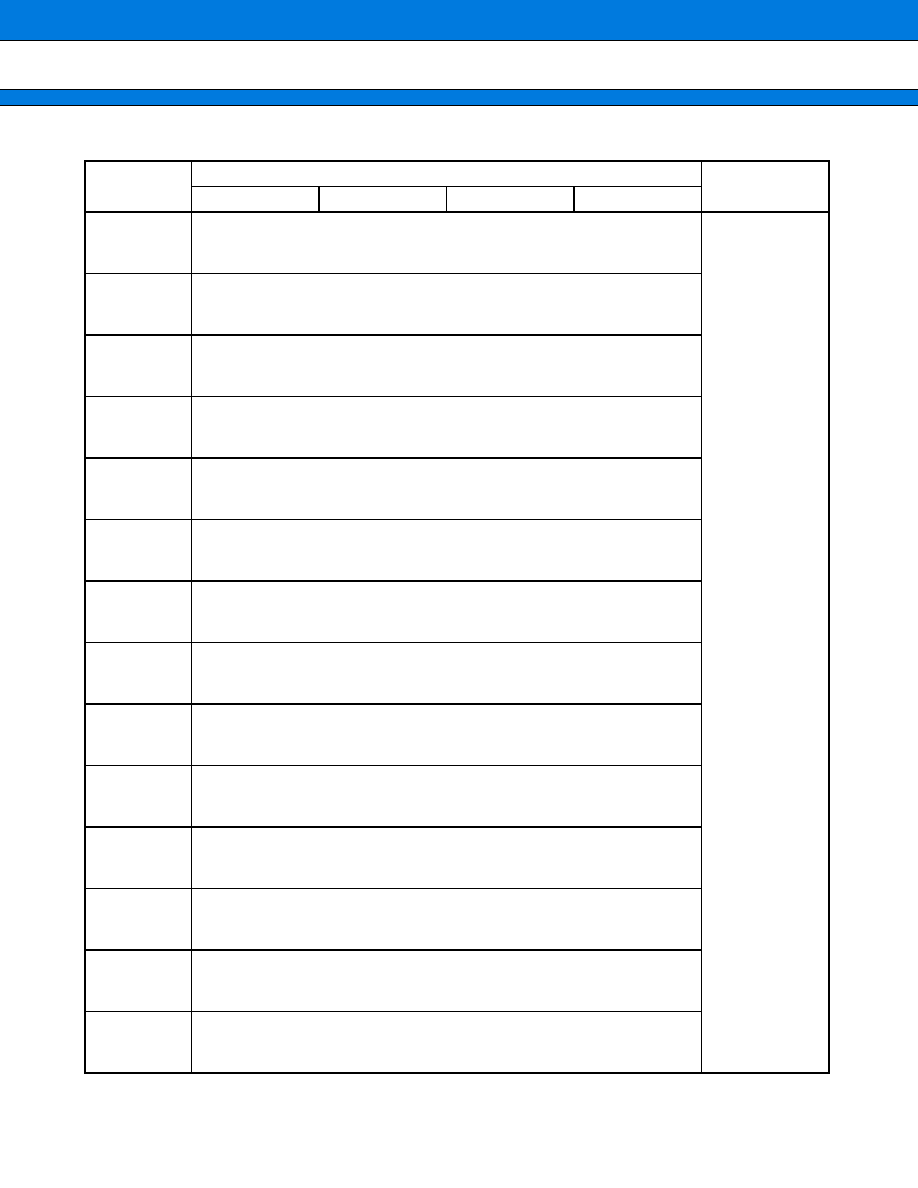

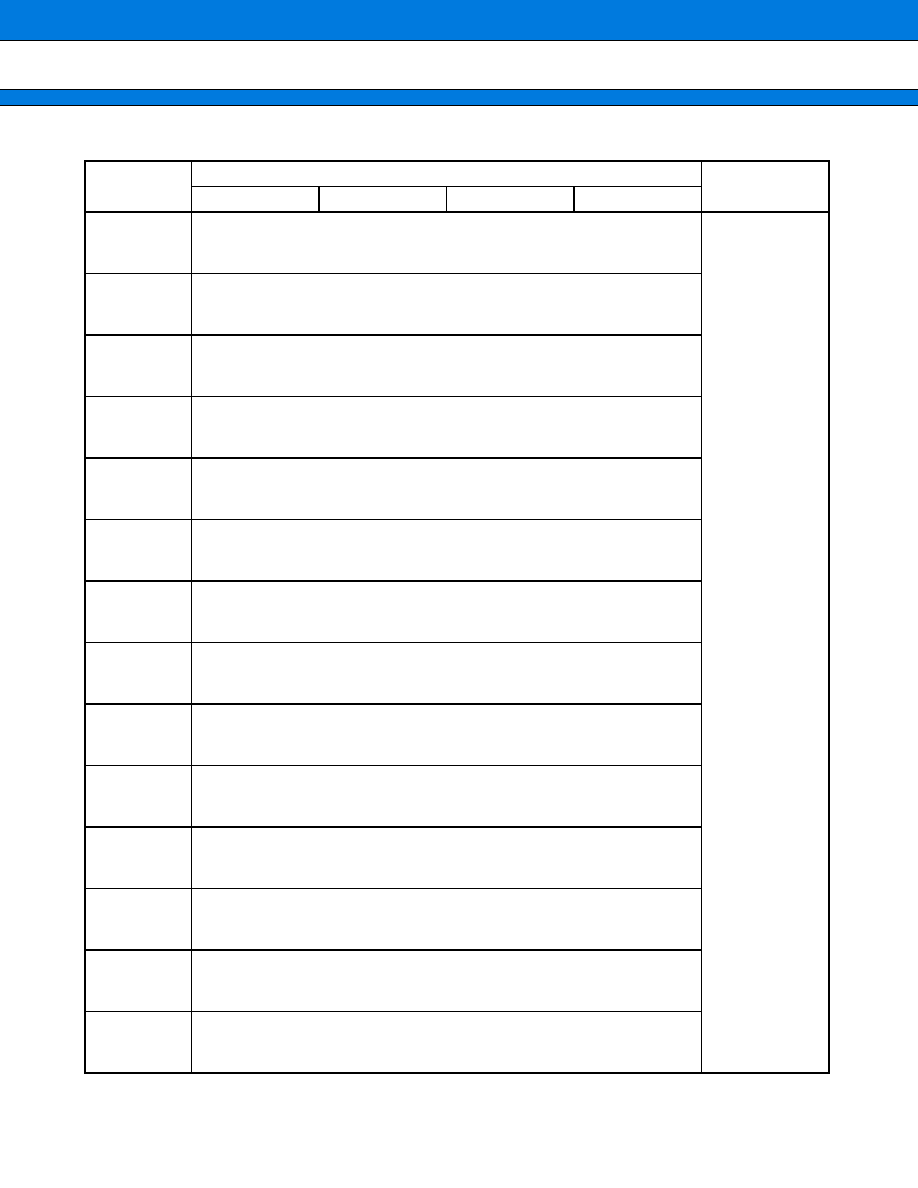

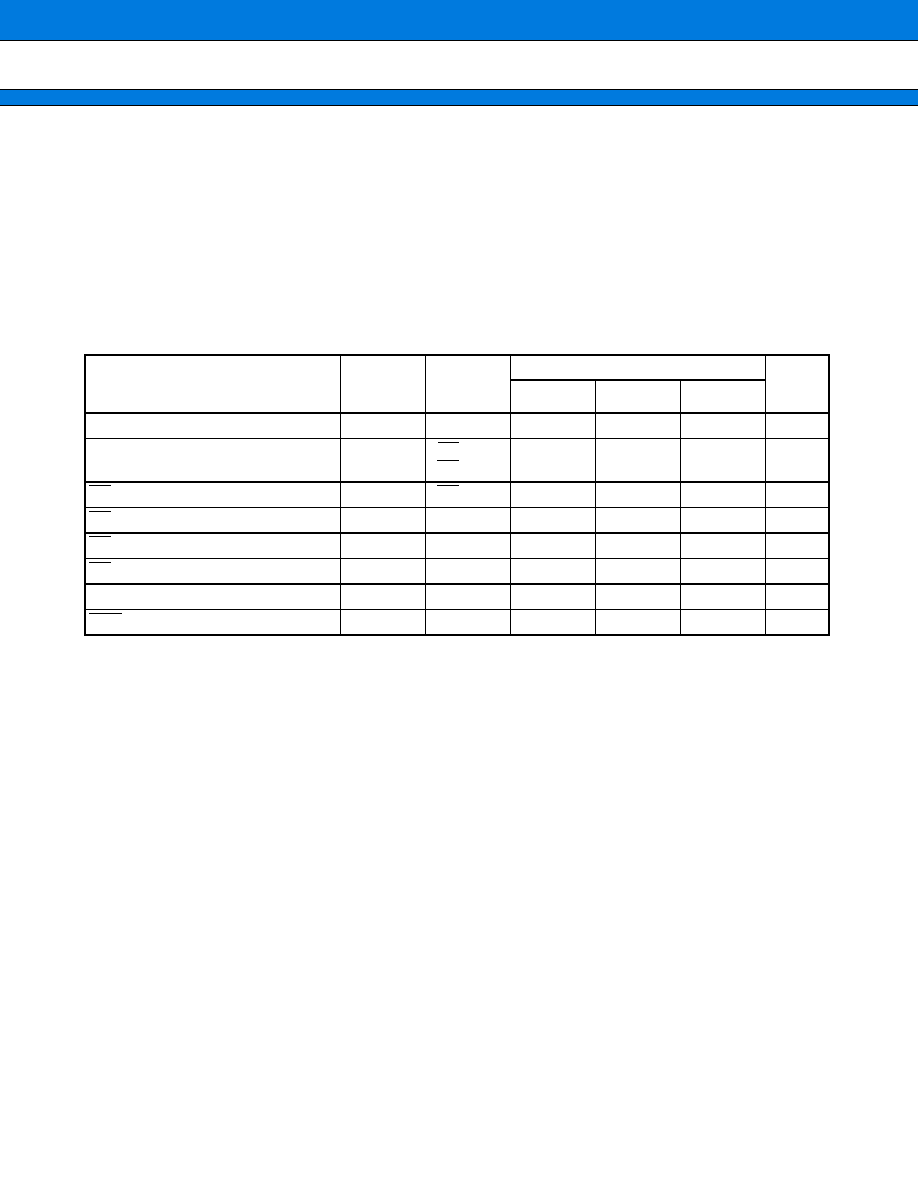

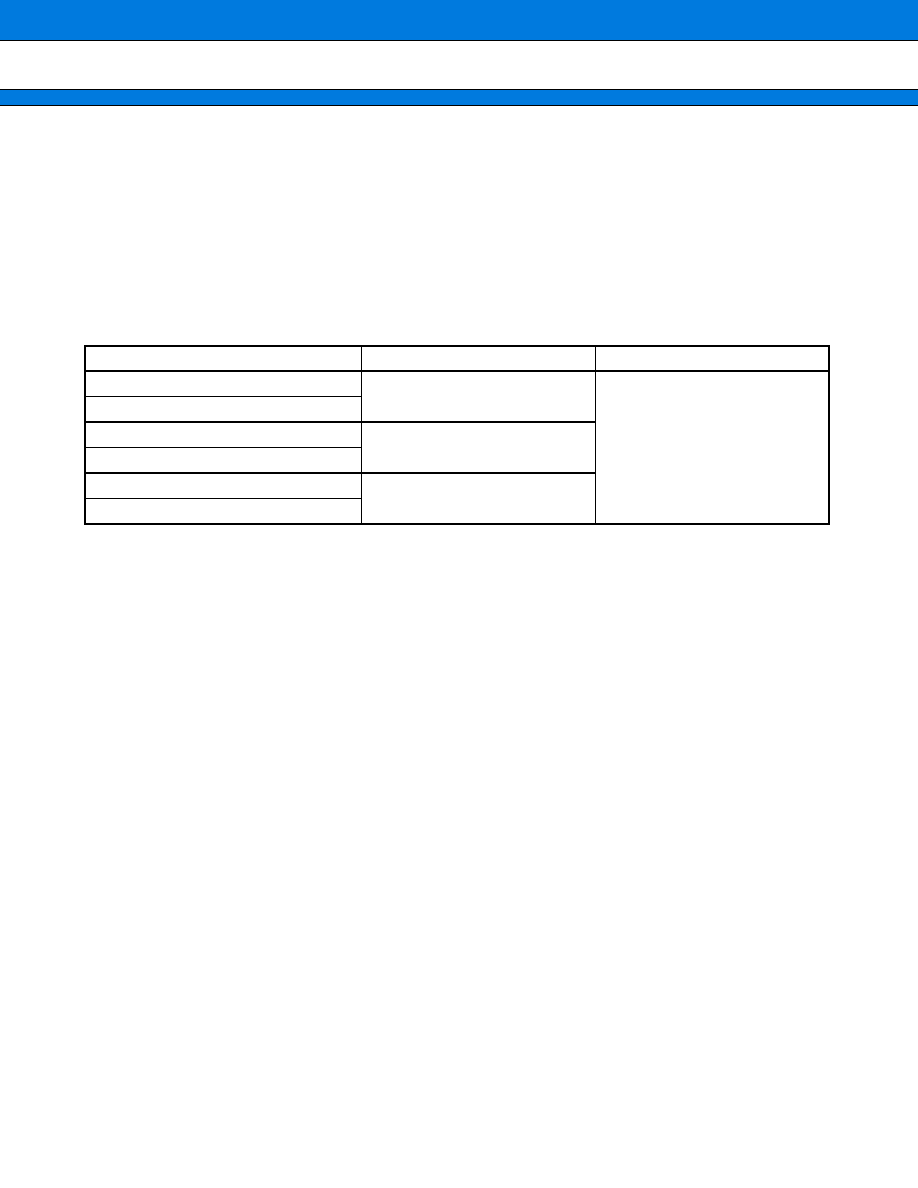

I/O CIRCUIT TYPE

(Continued)

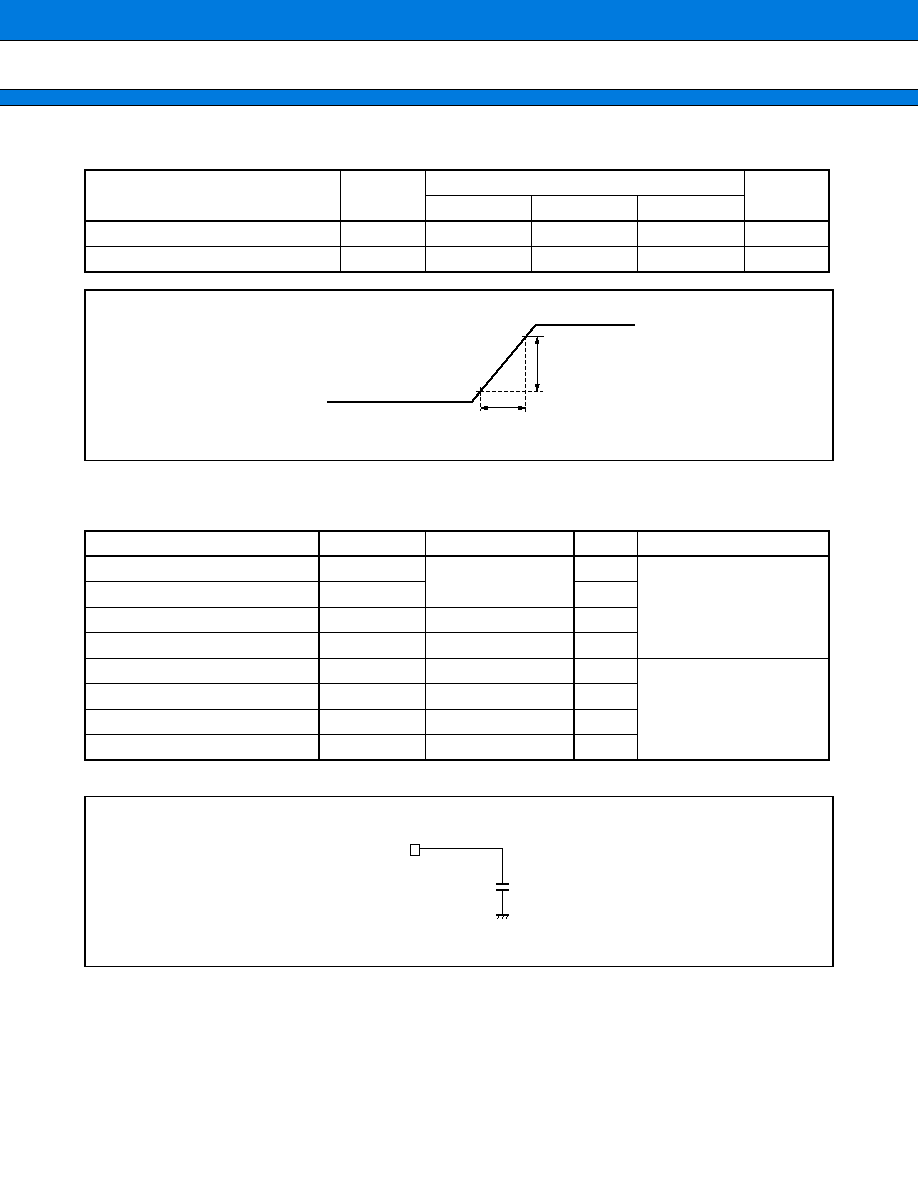

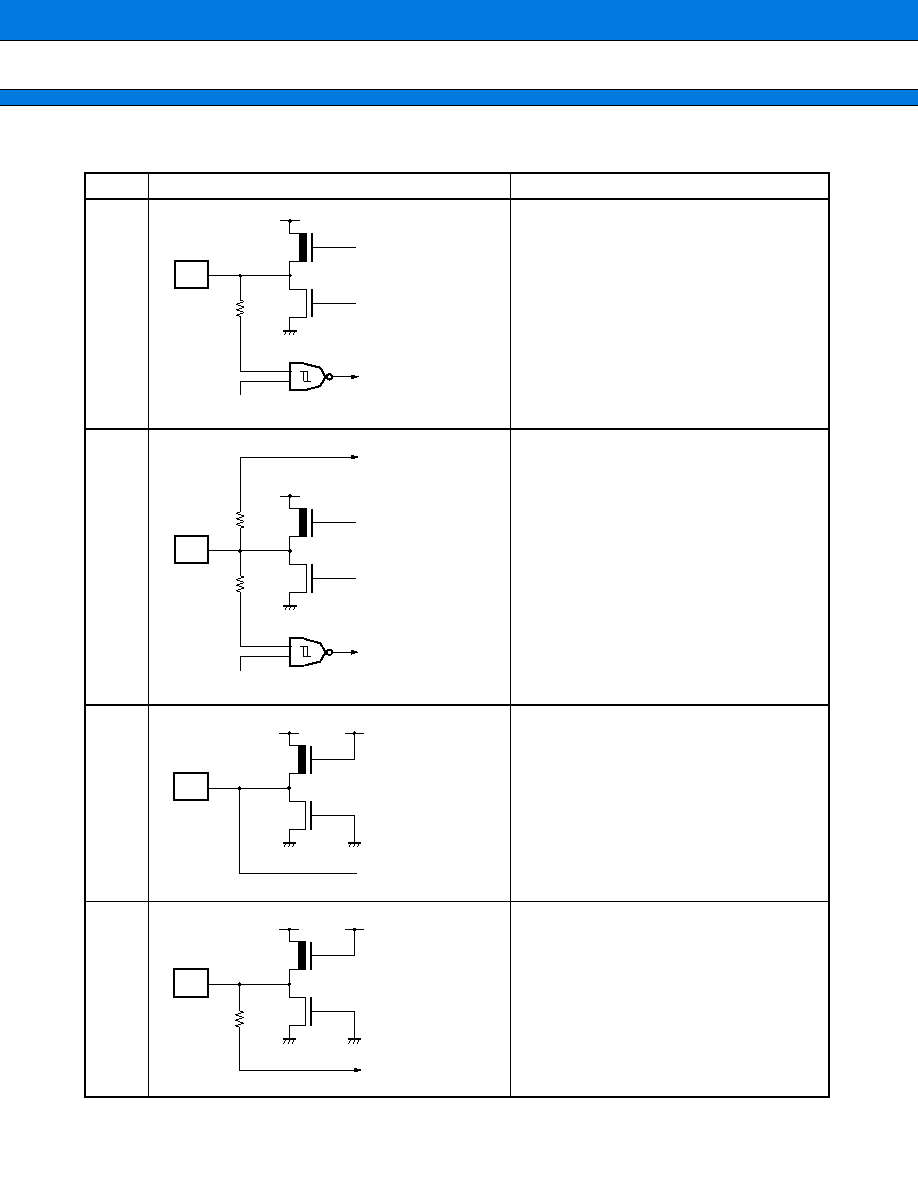

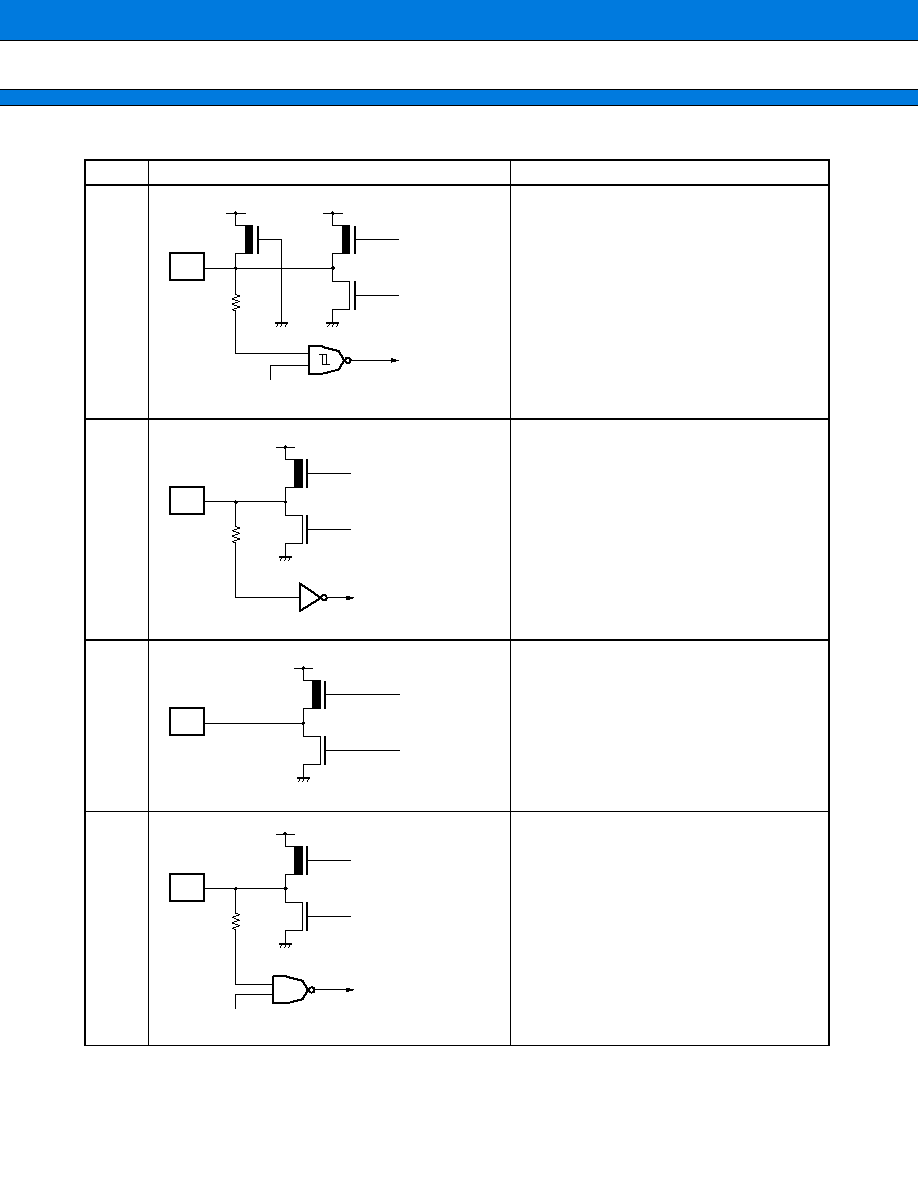

Type

Circuit type

Remarks

A

∑ I/O,

CMOS Automotive Schmitt-Trigger Input,

STOP control,

I

OH

=

4 mA, I

OL

=

4 mA

B

∑ I/O,

CMOS Automotive Schmitt-Trigger Input,

Analog Input,

STOP control,

I

OH

=

4 mA, I

OL

=

4 mA

C

∑ Analog output

D

∑ Analog Input

P

N

R

Stop control

Digital input

Digital output

Digital output

V

SS

P

N

R

R

Stop control

Digital input

Analog input

Digital output

Digital output

V

SS

P

N

Analog output

V

SS

V

CC

P

N

R

Analog input

V

SS

V

CC

MB91360G Series

19

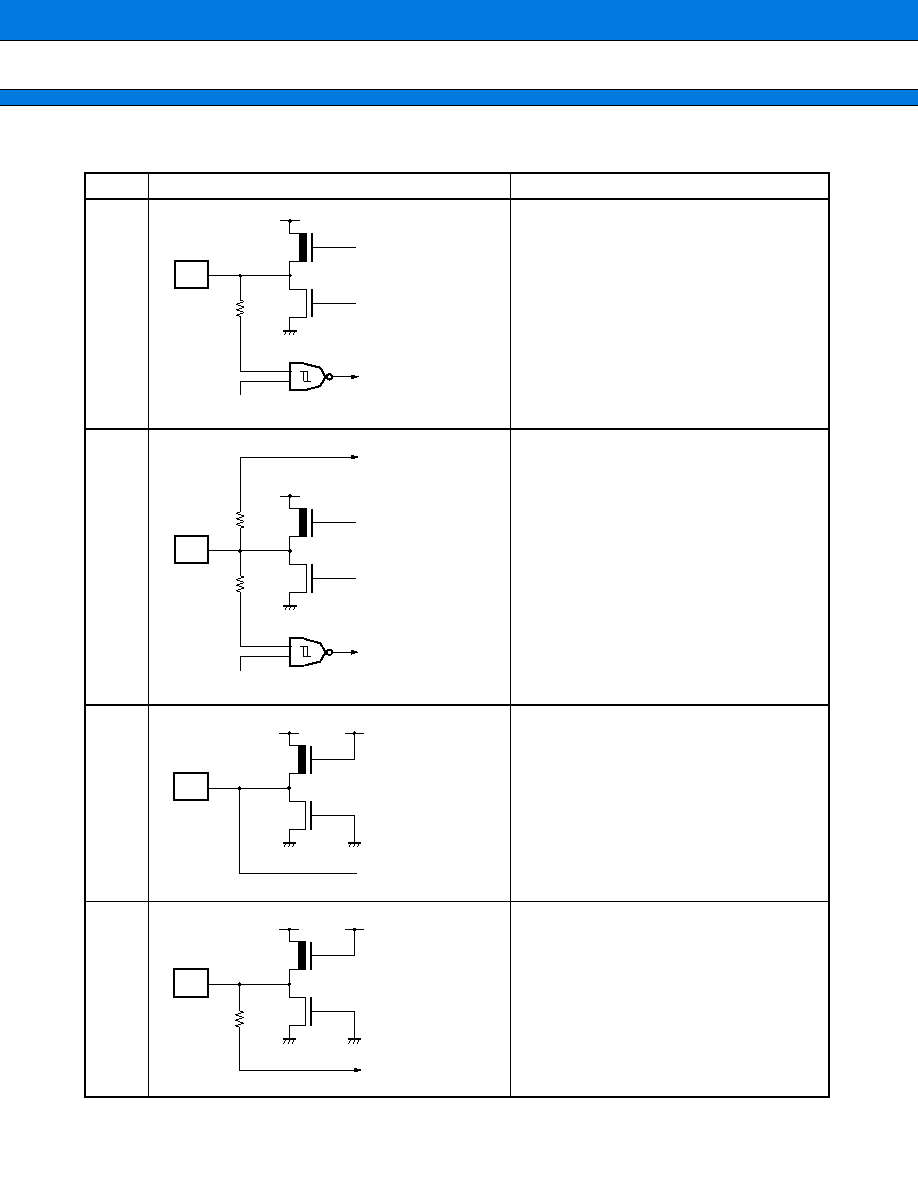

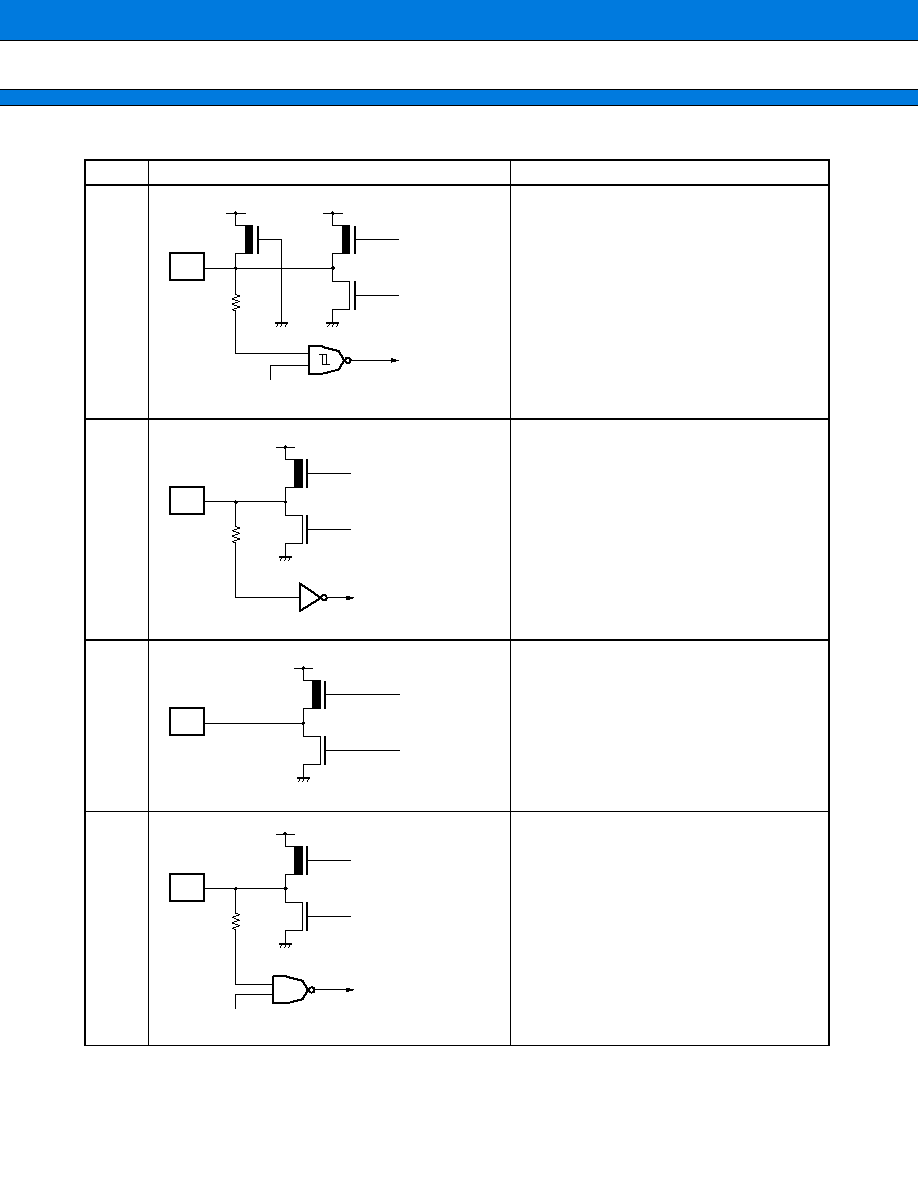

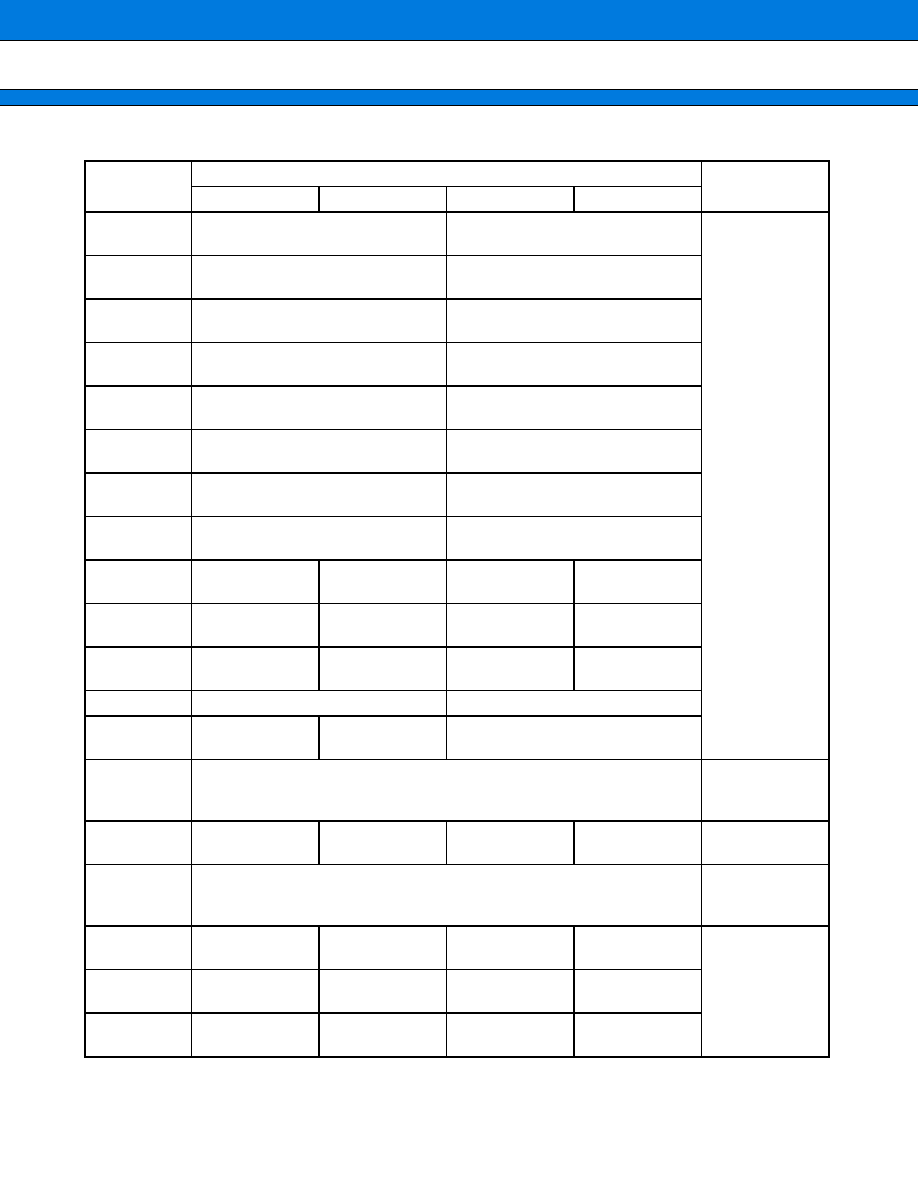

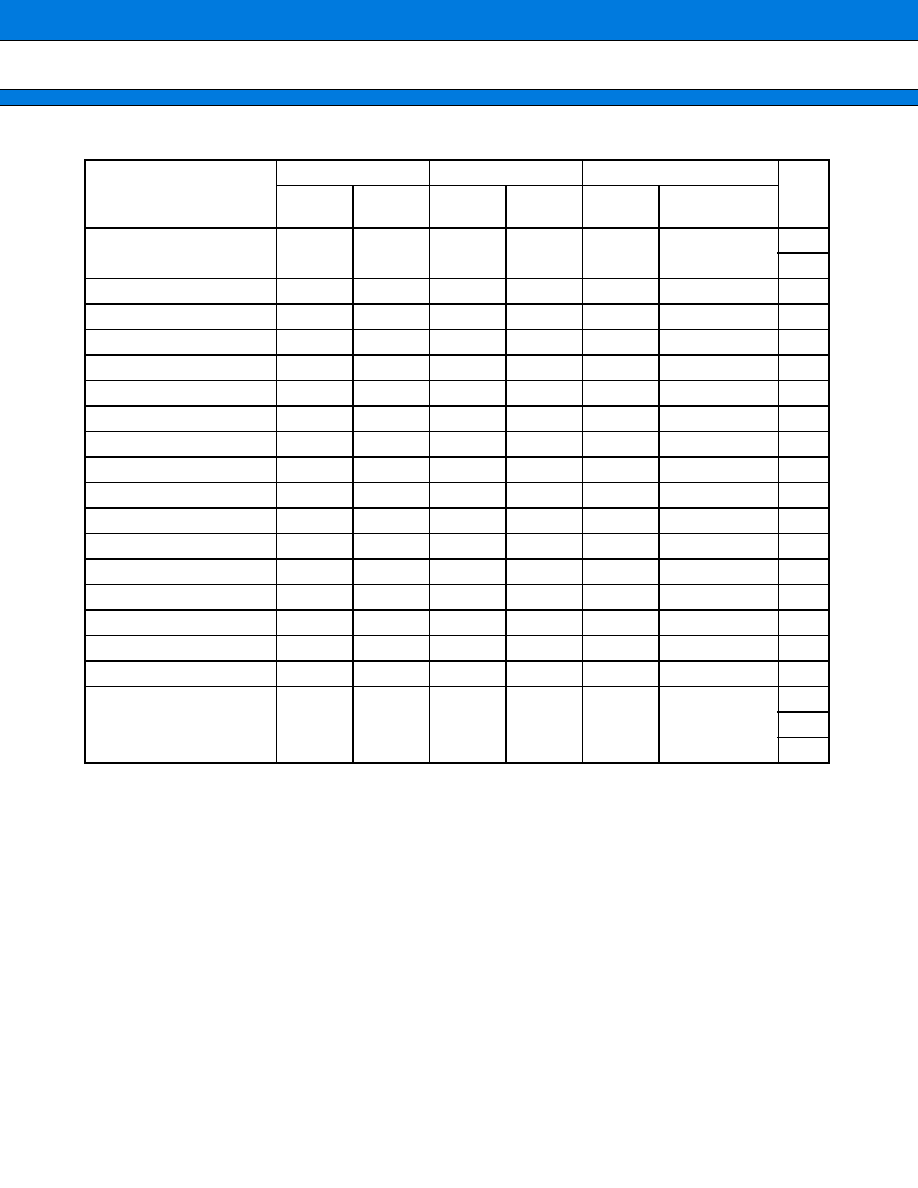

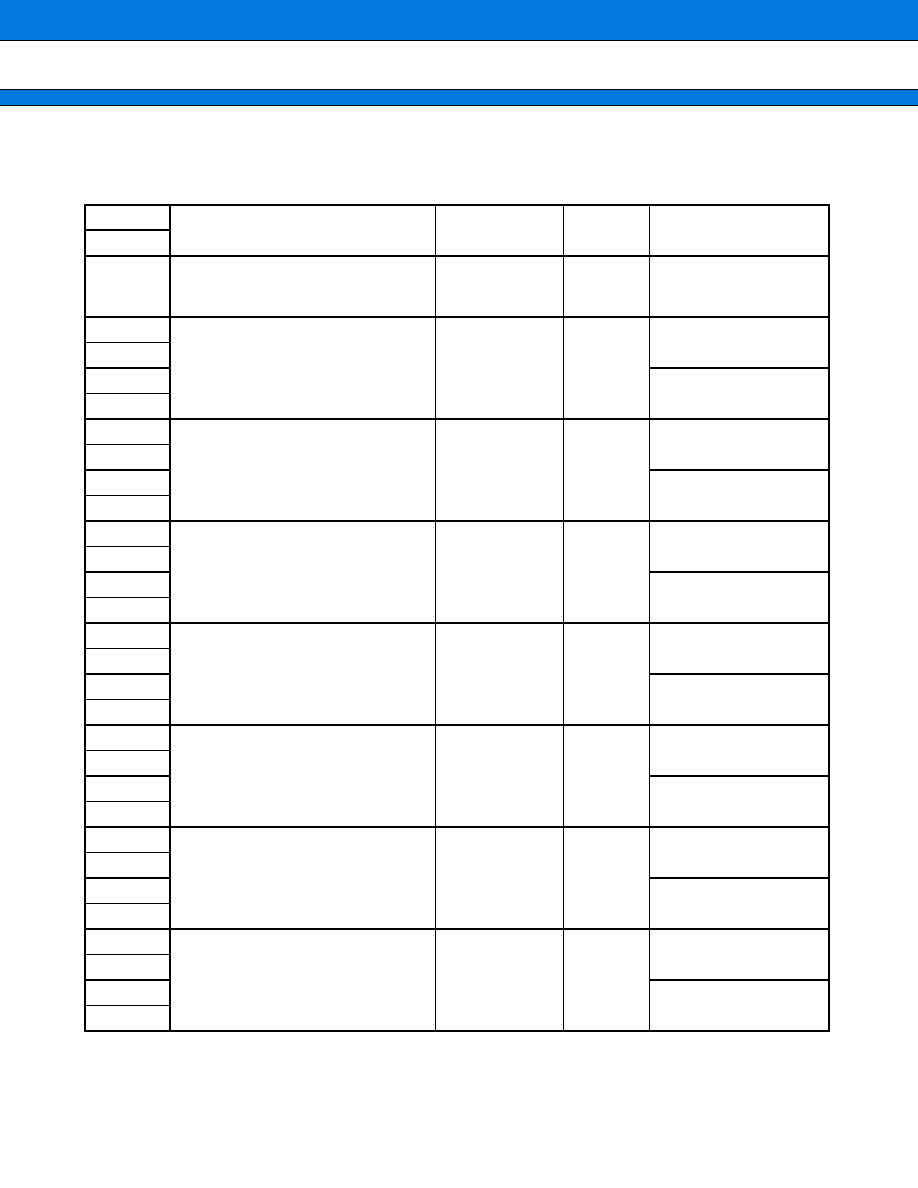

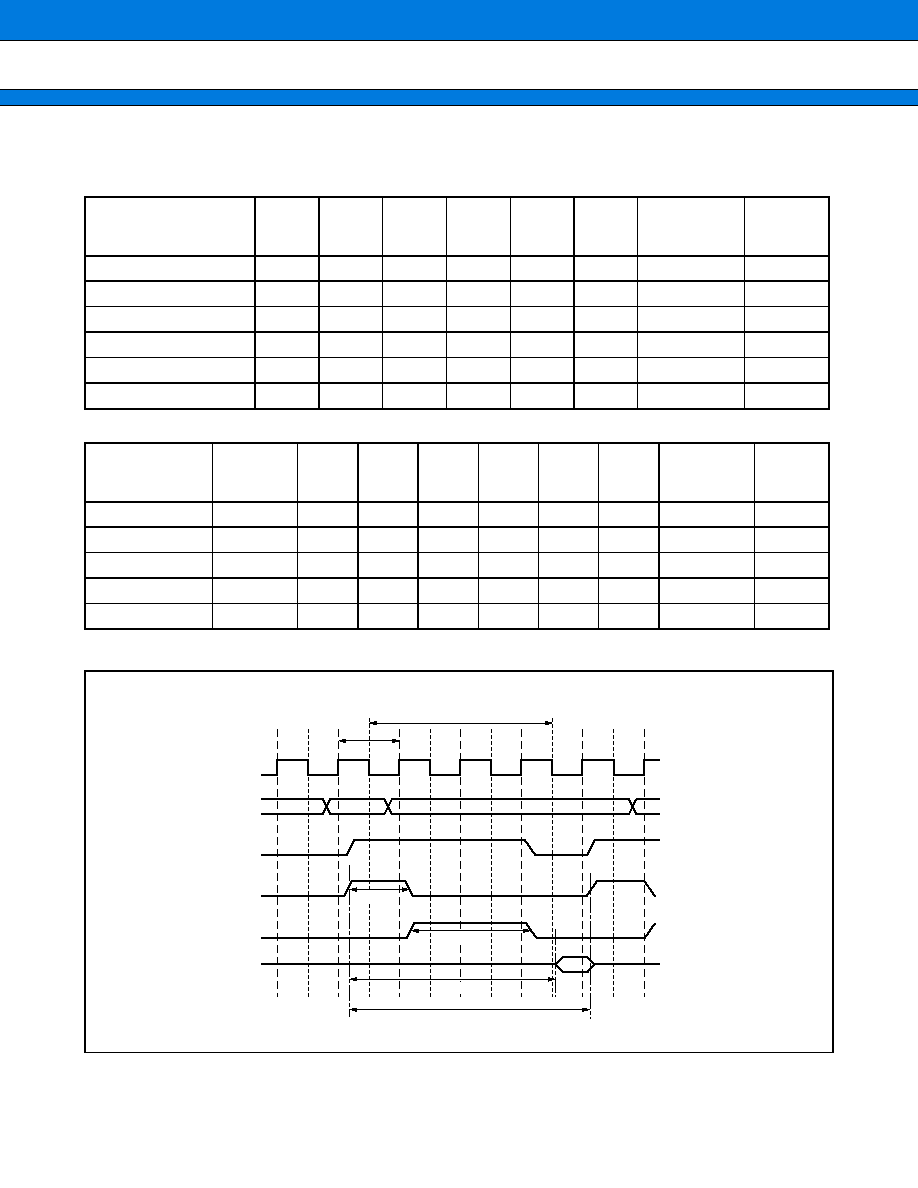

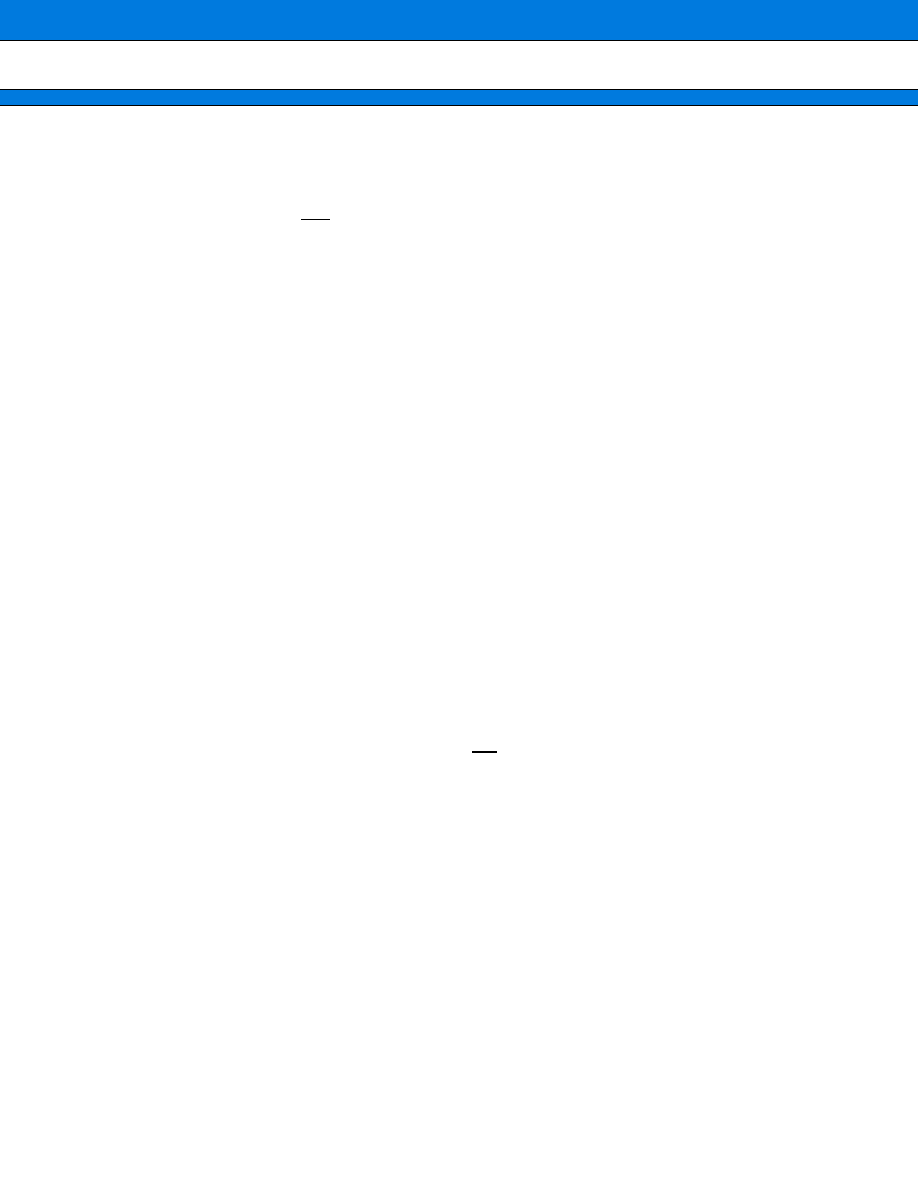

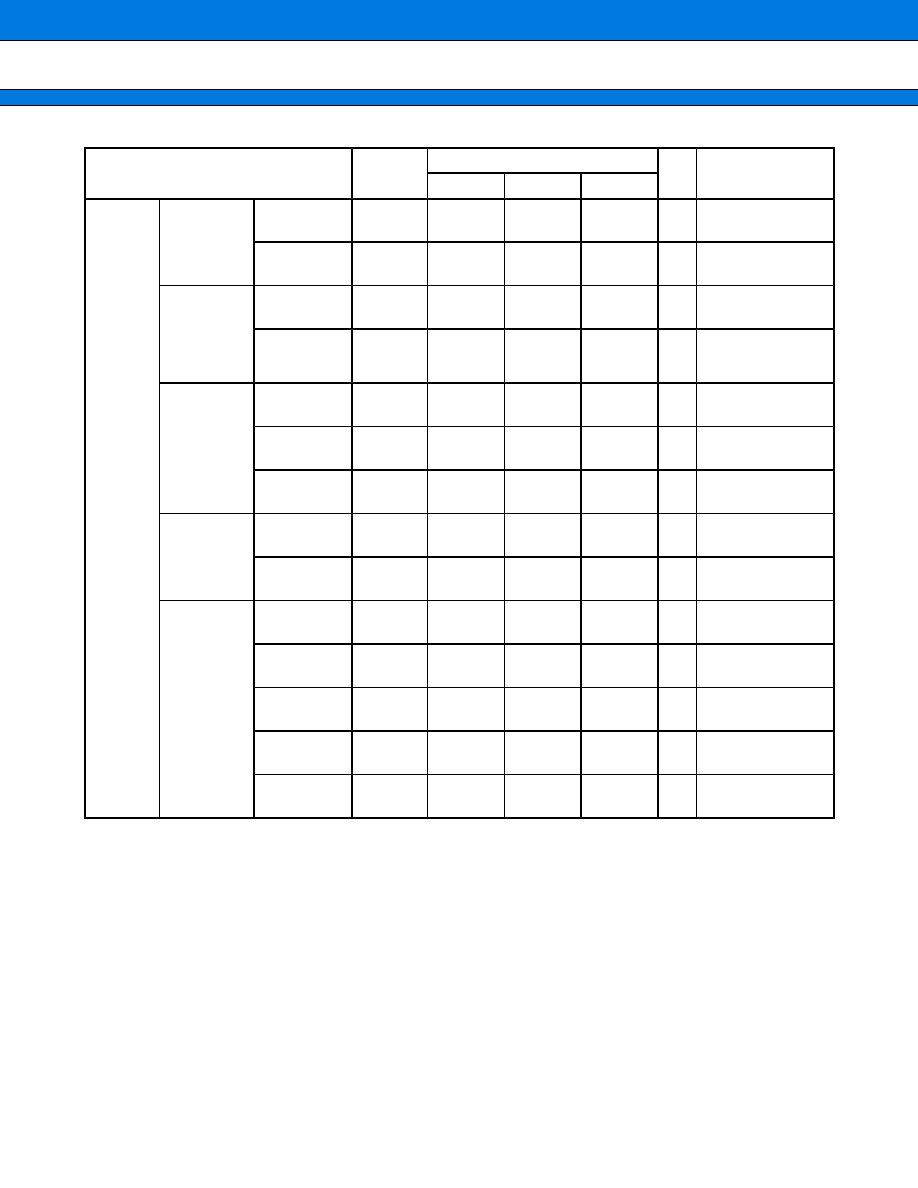

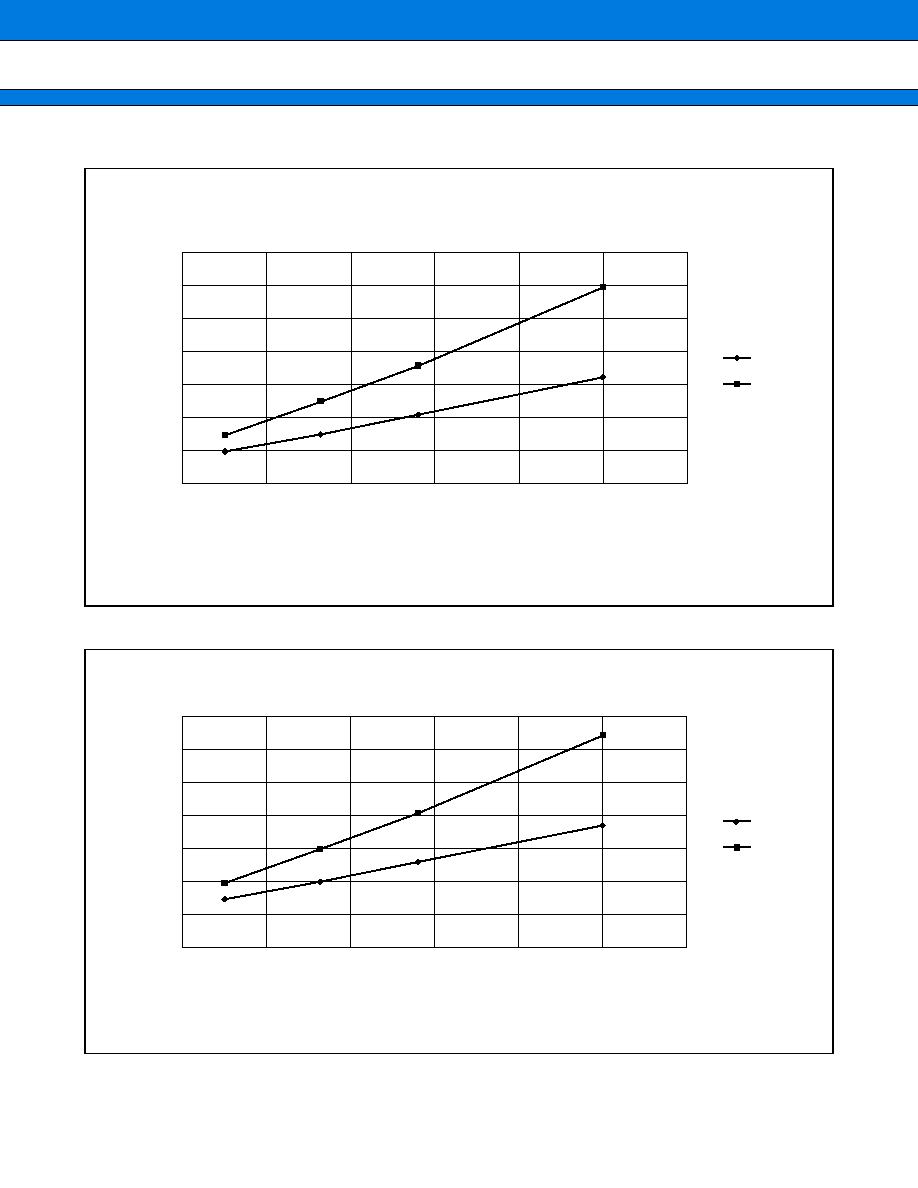

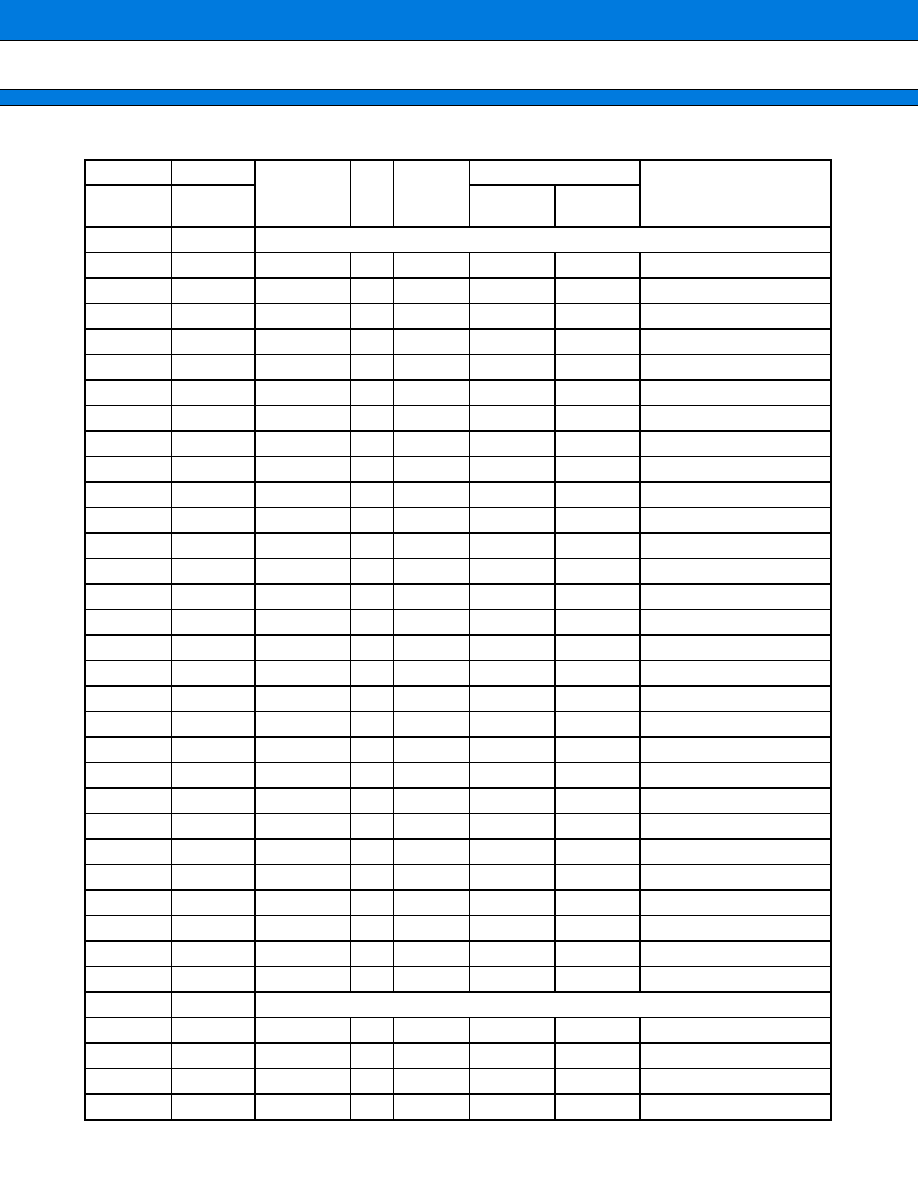

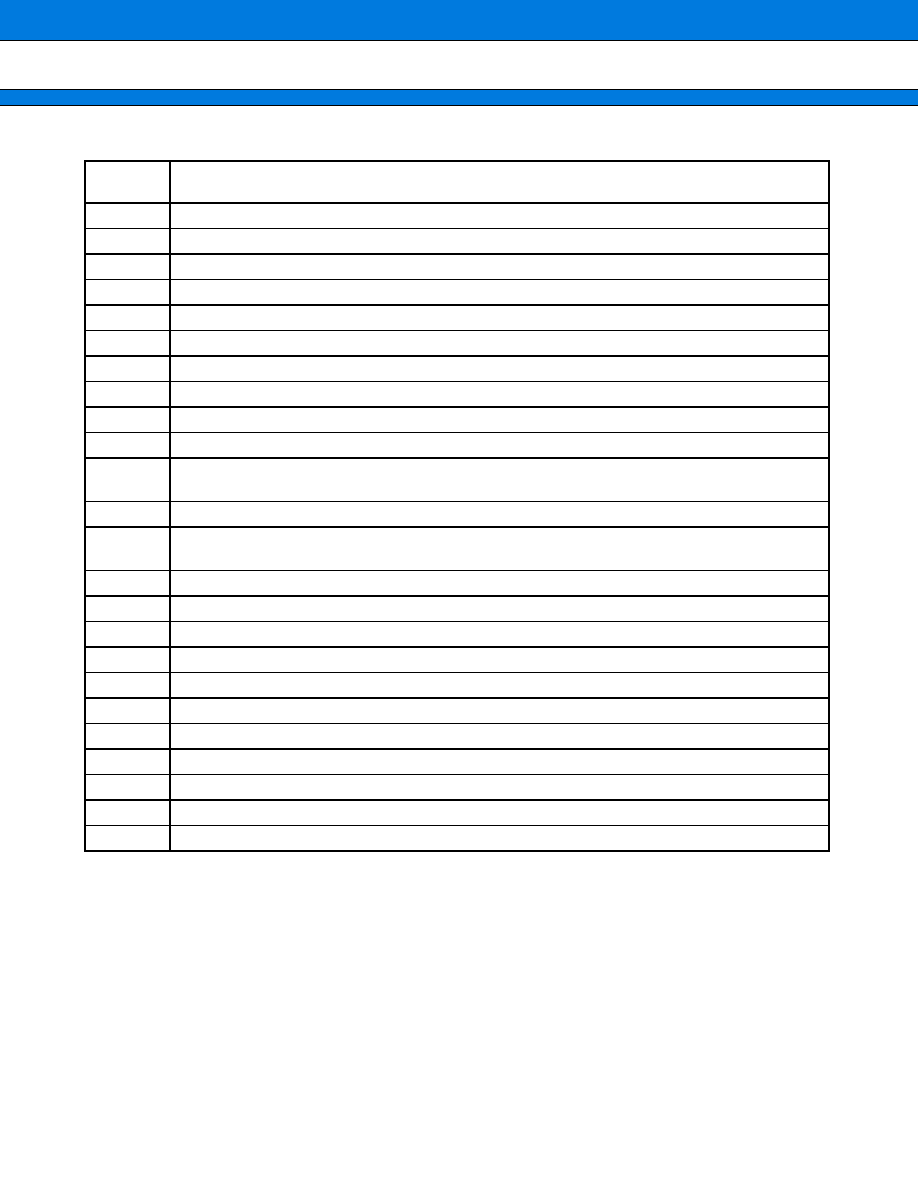

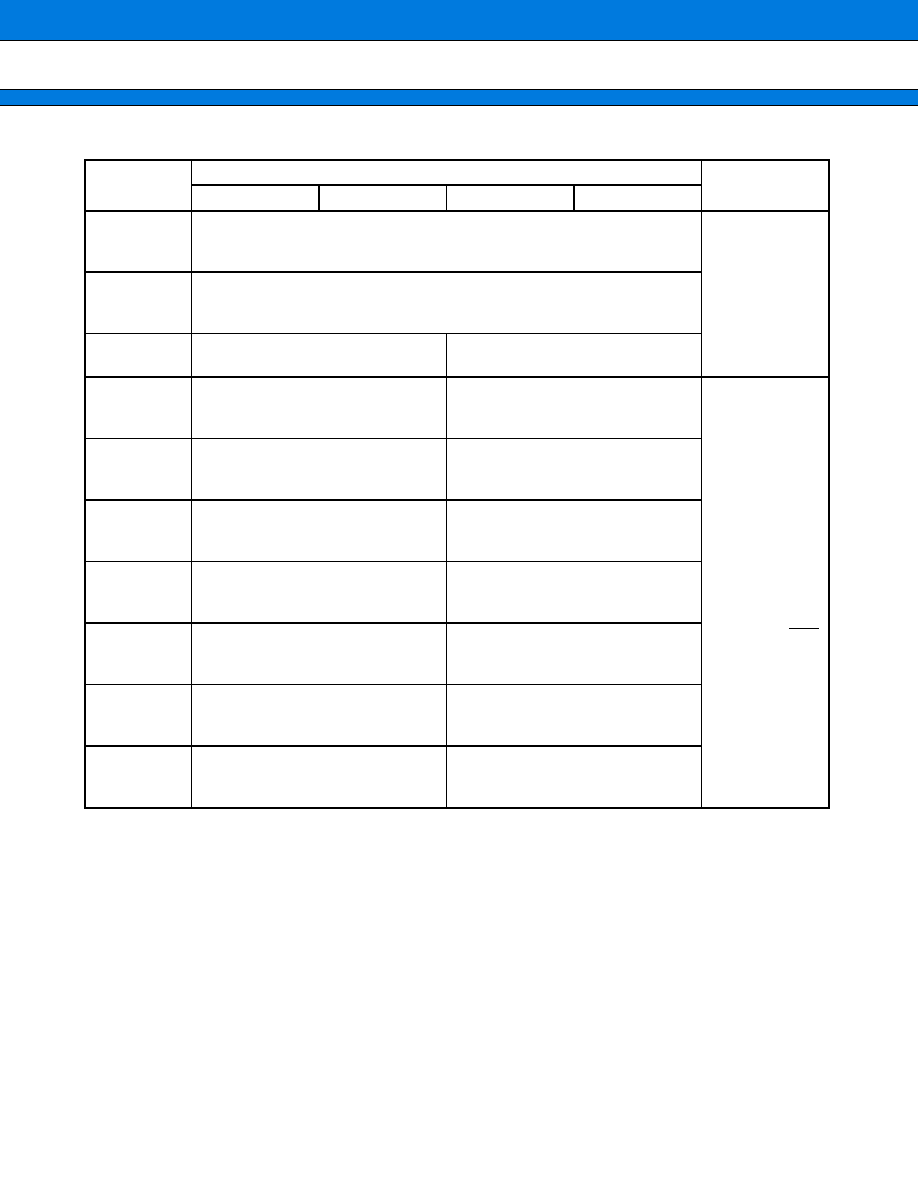

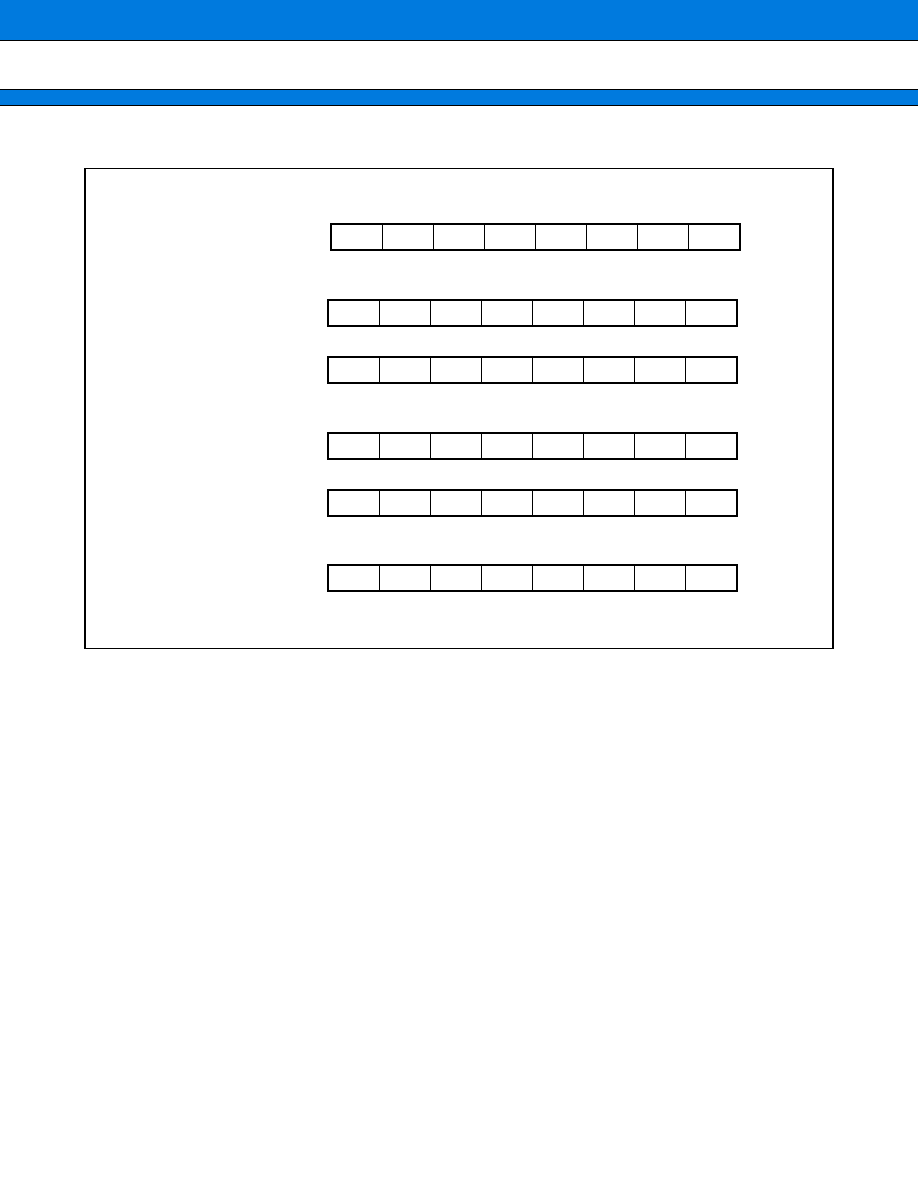

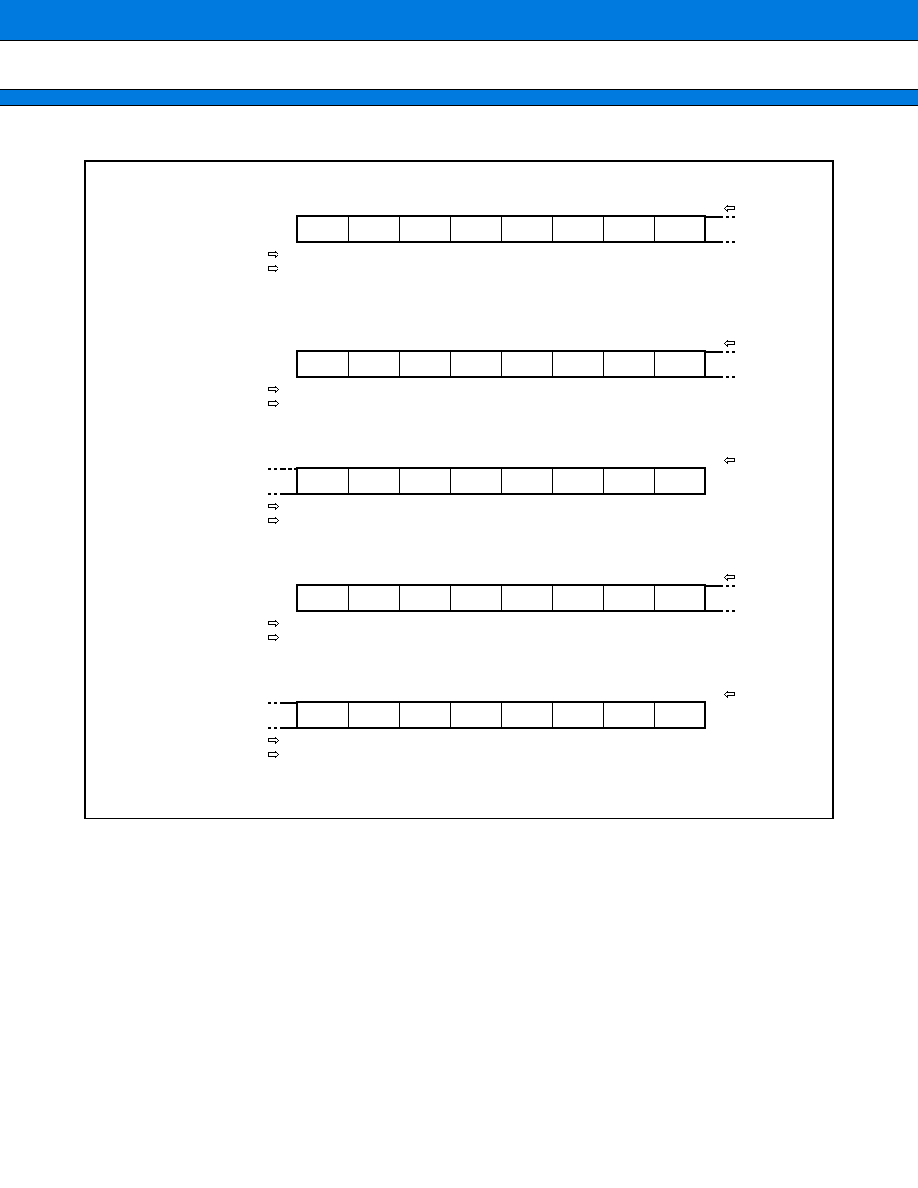

(Continued)

(Continued)

Type

Circuit type

Remarks

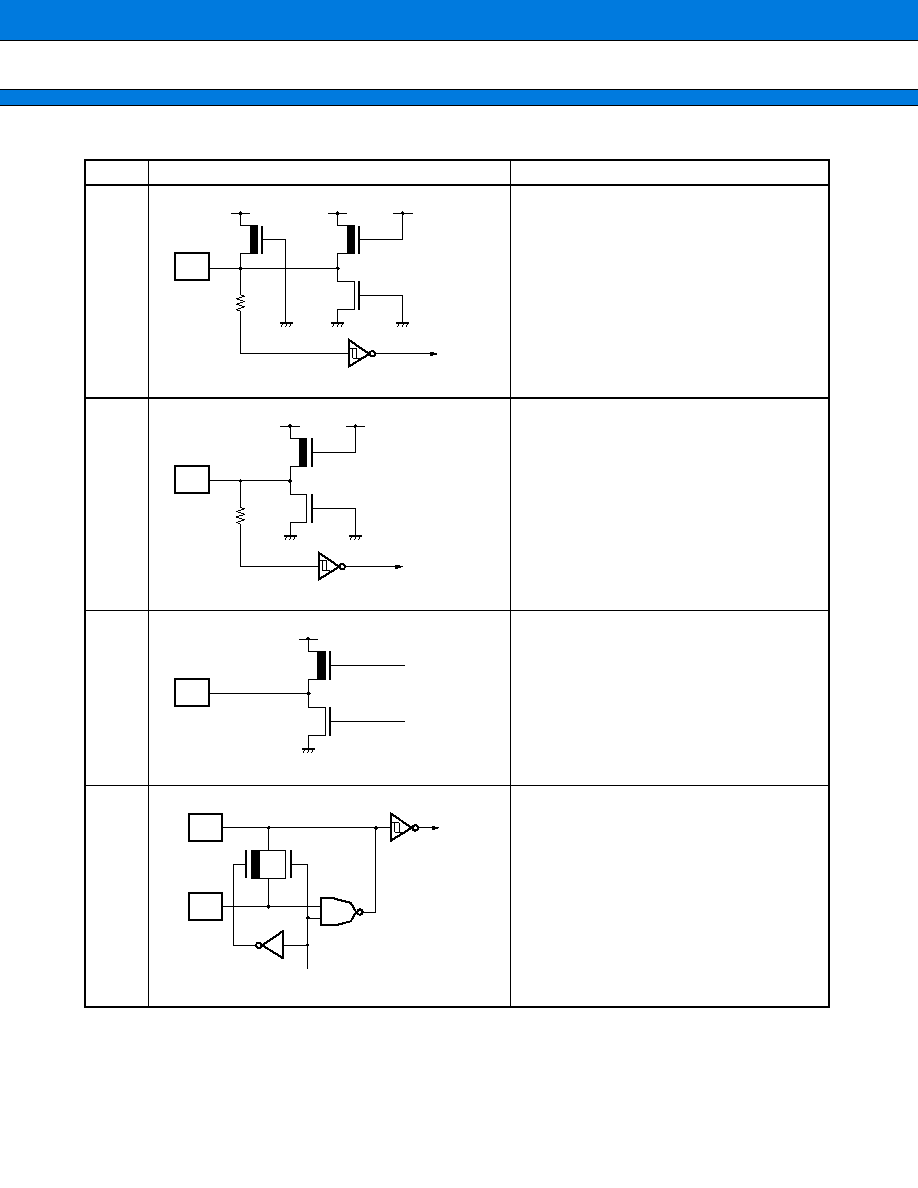

E

∑ CMOS Schmitt-Trigger Input,

Pullup Resistor: 50 k

F

∑ CMOS Schmitt-Trigger Input

G

∑ Tristate Output,

I

OH

=

4 mA, I

OL

=

4 mA

H

∑ 4 MHz Oscillator Pin

P

N

R

Digital input

P

V

SS

V

SS

V

CC

V

CC

P

N

R

Digital input

V

SS

V

CC

P

N

Digital output

Digital output

V

SS

V

CC

Stop control

Clock input

X1

X0

MB91360G Series

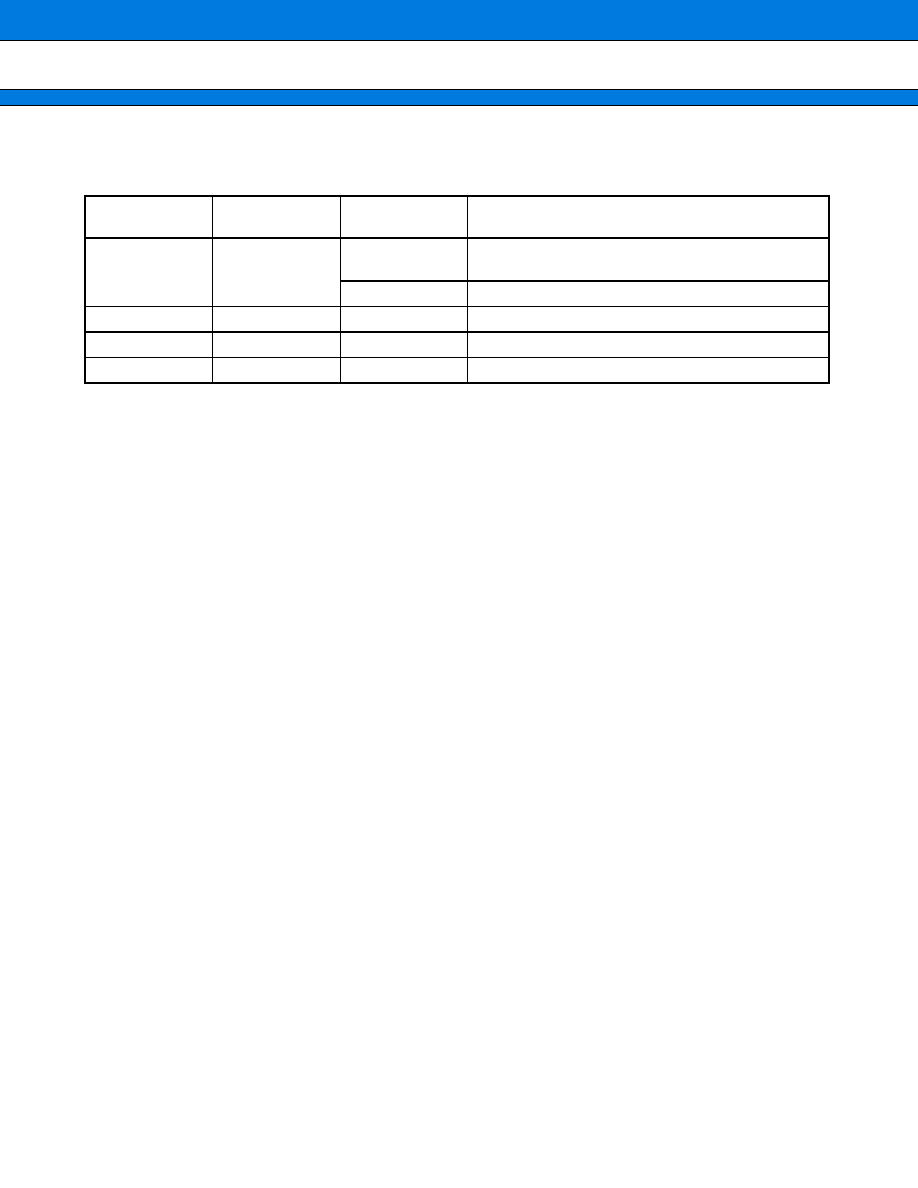

20

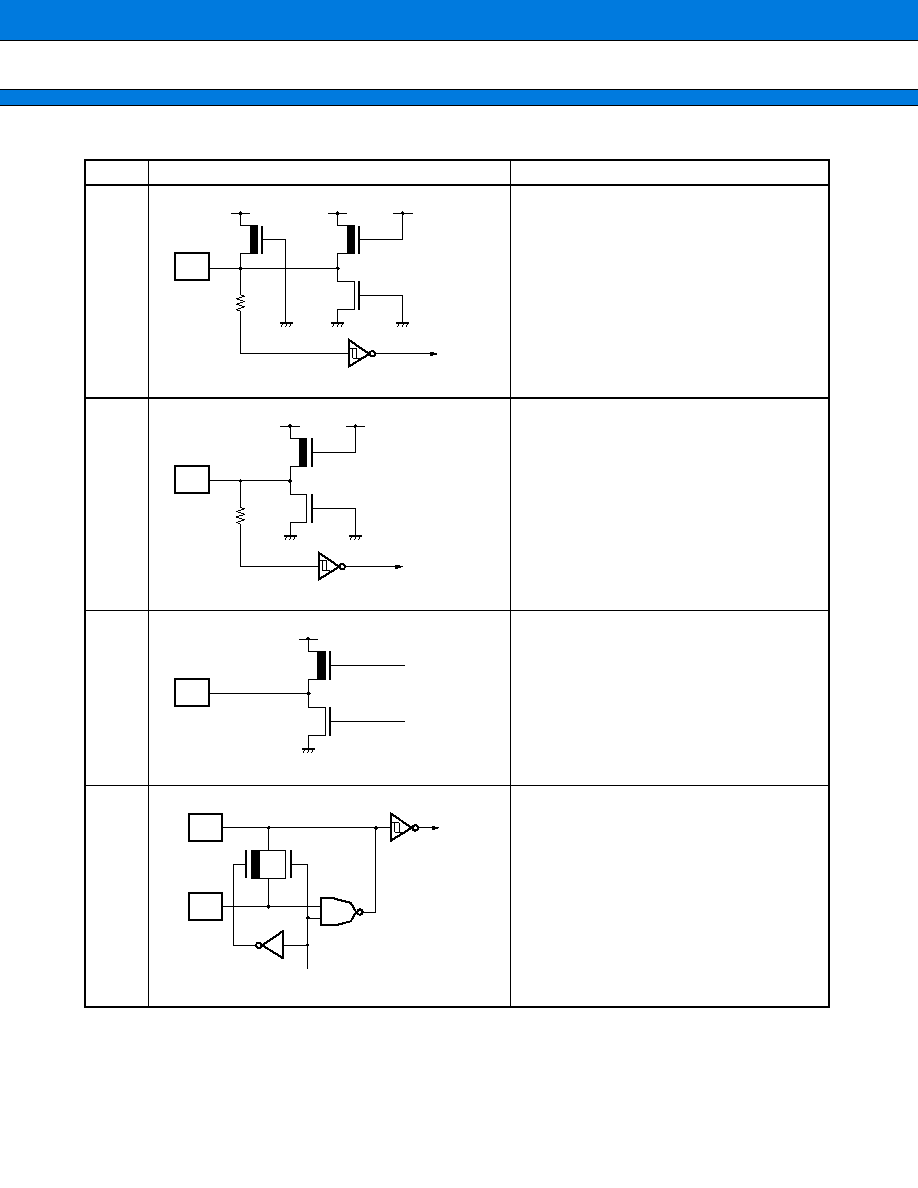

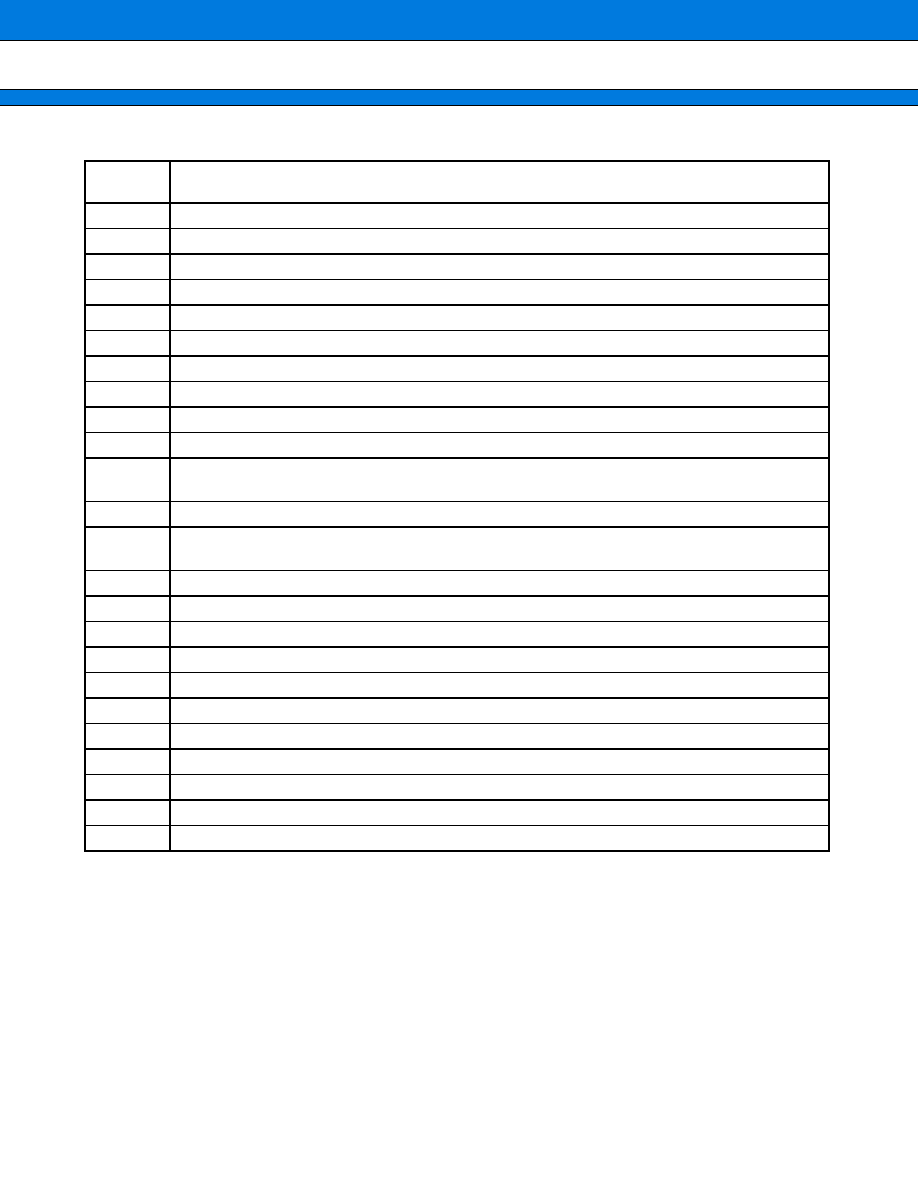

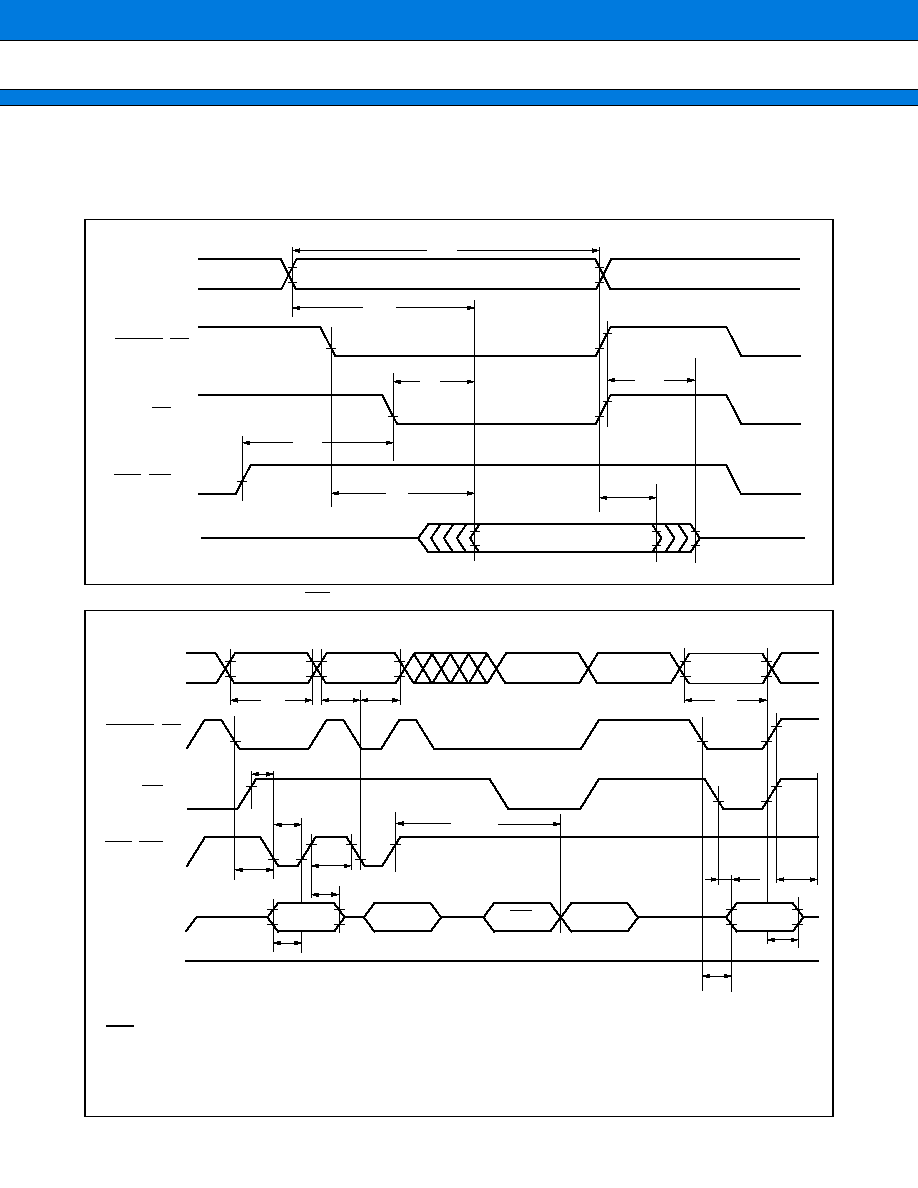

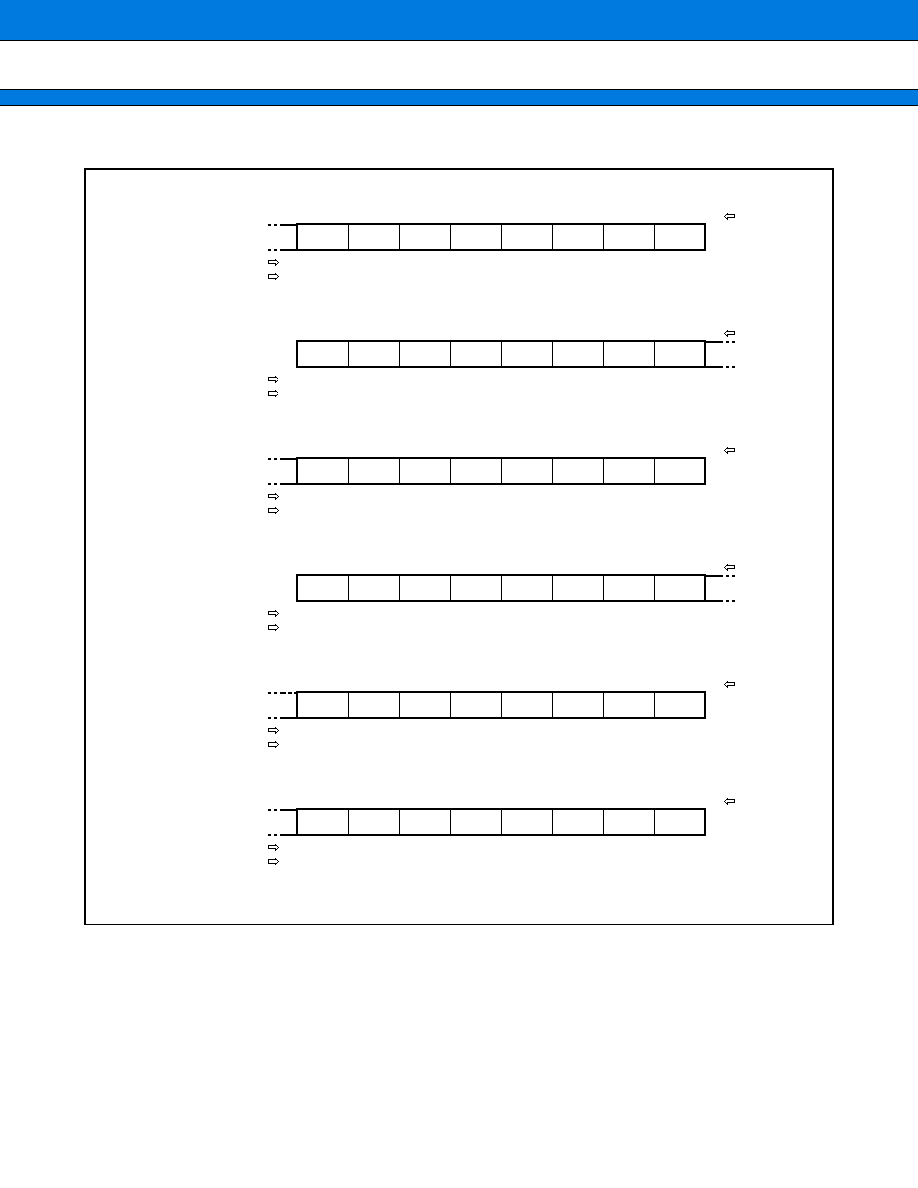

(Continued)

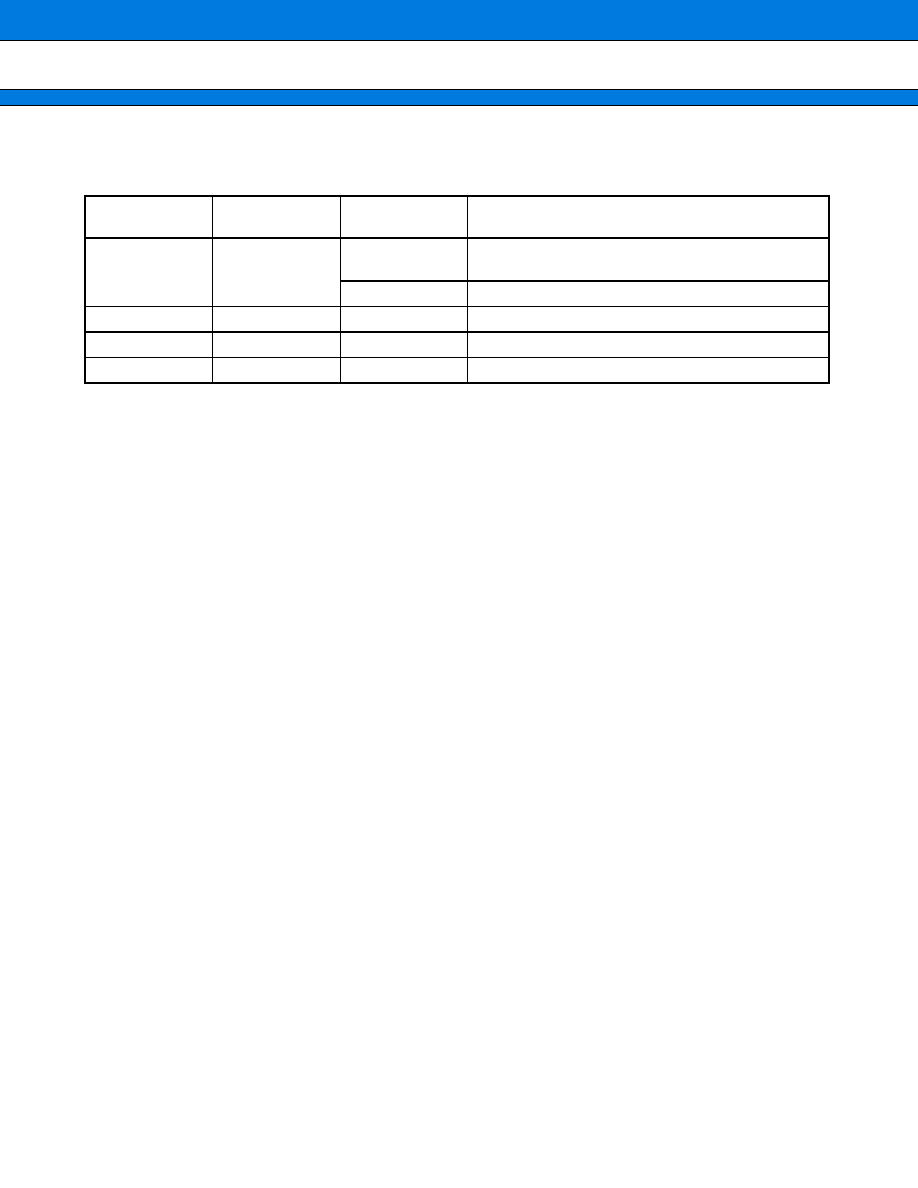

(Continued)

Type

Circuit type

Remarks

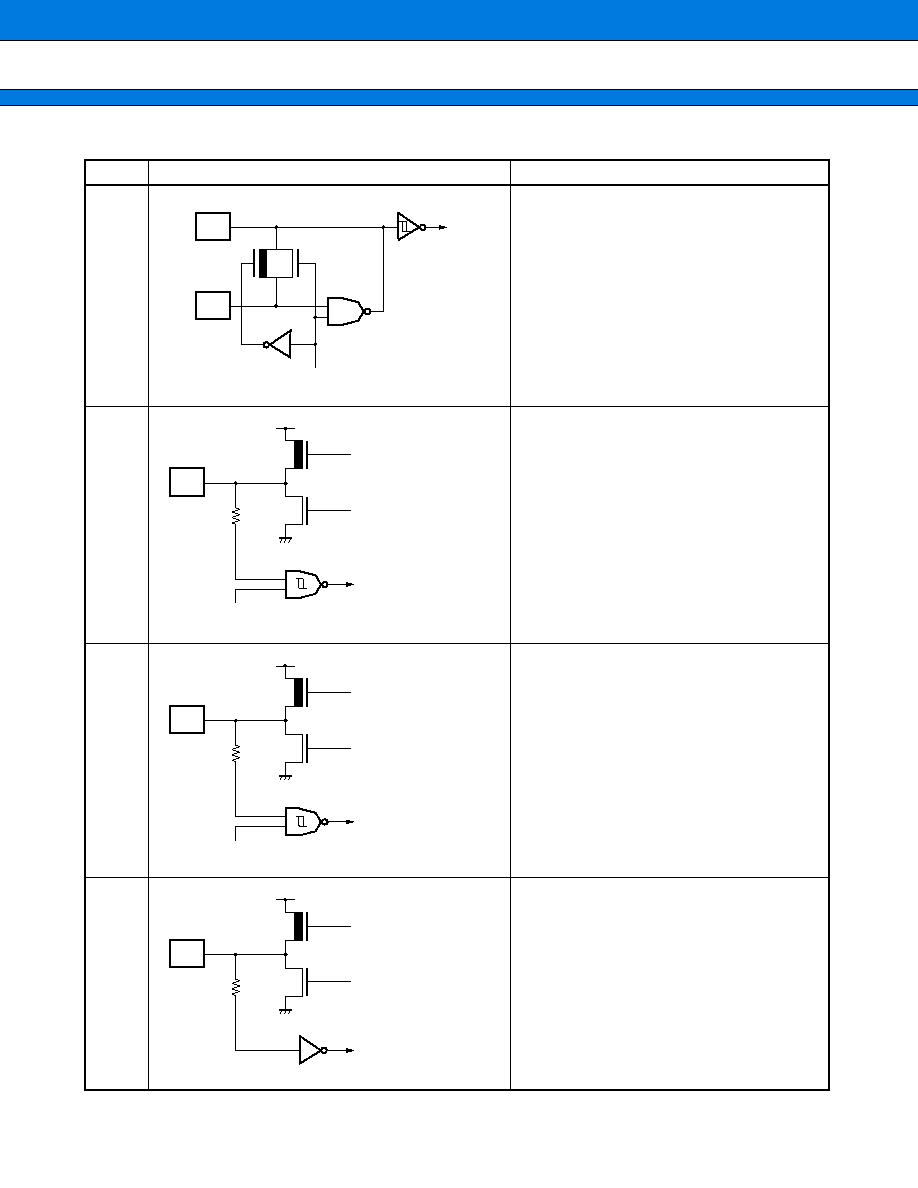

I

∑ 32 kHz Oscillator Pin

J

∑ I/O,

CMOS Automotive Schmitt-Trigger Input,

STOP control (LED) ,

I

OH

=

14 mA, I

OL

=

24 mA

K

∑ I/O,

CMOS Automotive Schmitt-Trigger Input,

STOP control (SMC) ,

I

OH

=

30 mA, I

OL

=

30 mA

∑ Typ. slew rate of 40 ns

L

∑ I/O,

CMOS Input; 5 V or 3 V input,

I

OH

=

4 mA, I

OL

=

4 mA

Stop control

Clock input

X1A

X0A

P

N

R

Stop control

Digital input

Digital output

Digital output

V

SS

P

N

R

Stop control

Digital input

Digital output

Digital output

V

SS

P

N

R

Digital input

Digital output

Digital output

V

SS

V

CC

MB91360G Series

21

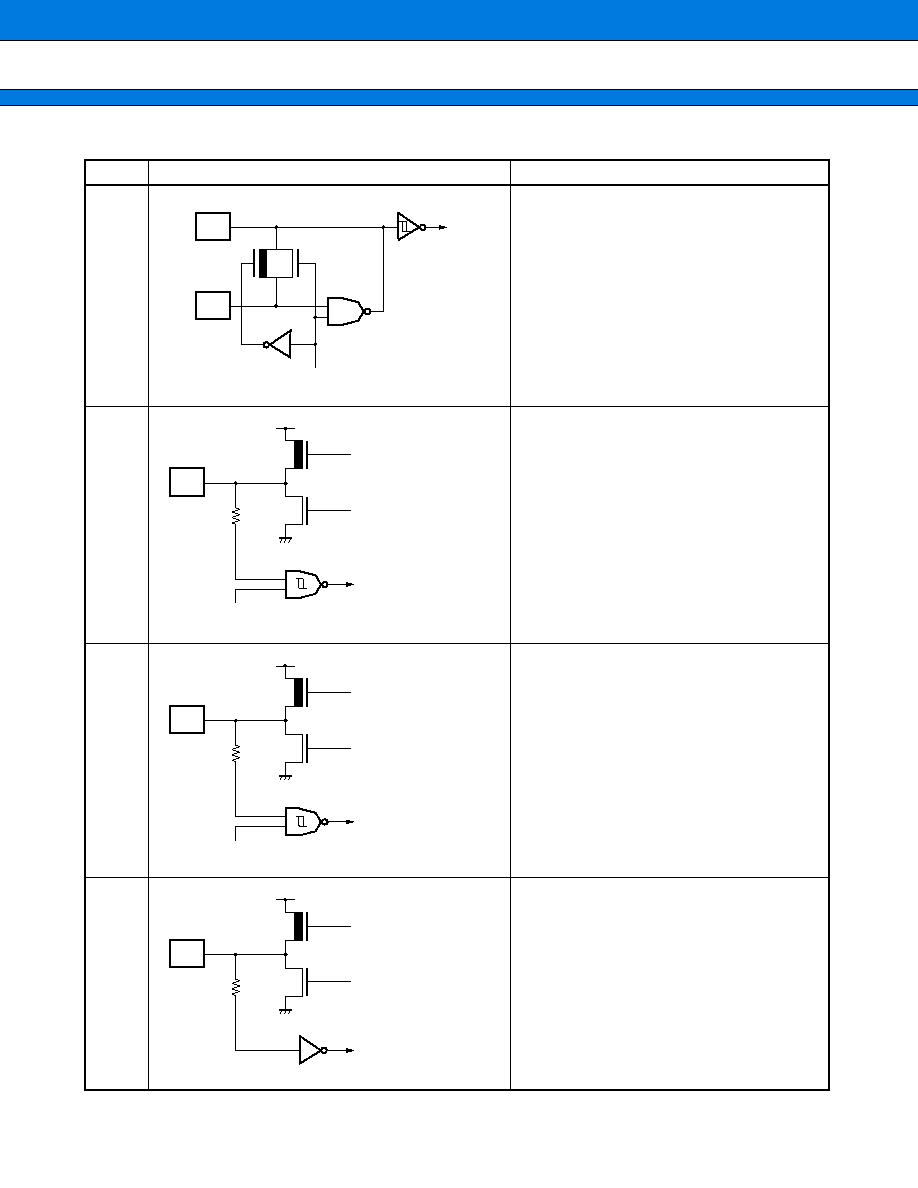

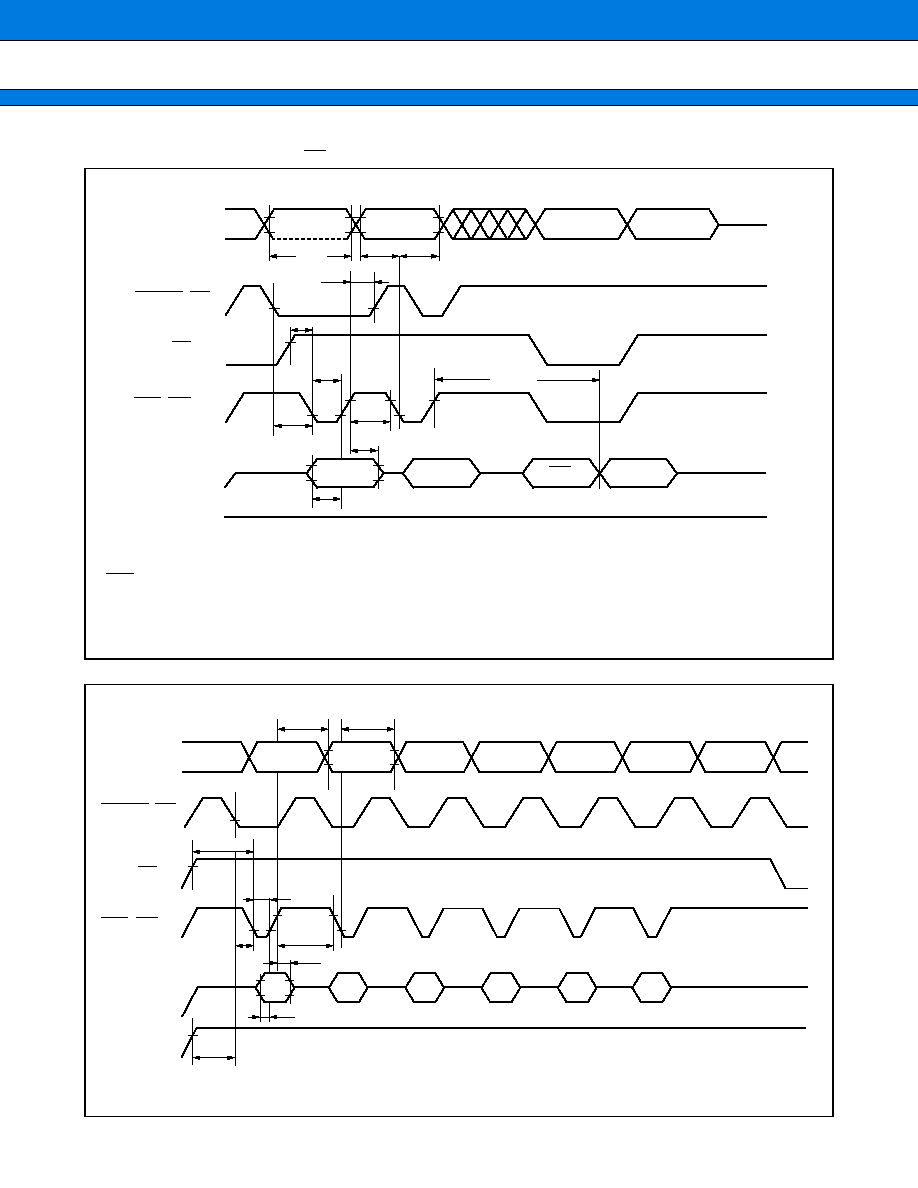

(Continued)

(Continued)

Type

Circuit type

Remarks

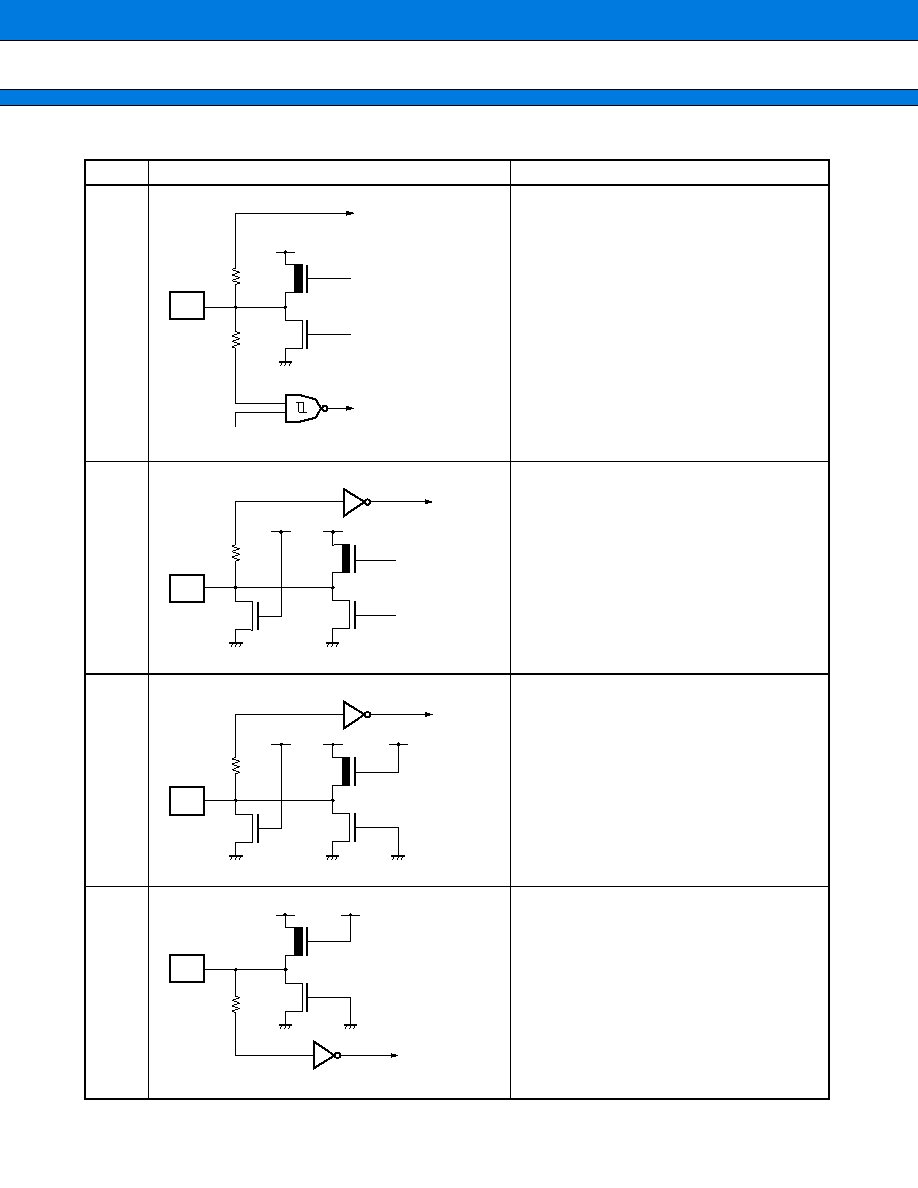

M

∑ I/O,

CMOS Automotive Schmitt-Trigger Input,

Analog Input, STOP control (SMC) ,

I

OH

=

30 mA, I

OL

=

30 mA

∑ Typ. slew rate of 40 ns

N

∑ I/O,

CMOS Input,

Pulldown Resistor: 50 k

,

5 V or 3 V input,

I

OH

=

4 mA, I

OL

=

4 mA

O

∑ CMOS Input,

Pulldown Resistor: 50 k

,

5 V or 3 V input

P

∑ CMOS Input; 3 V input

P

N

R

R

Stop control

Digital input

Analog input

Digital output

Digital output

V

SS

P

N

R

Digital input

Digital output

Digital output

N

V

SS

V

CC

P

N

R

Digital input

N

V

SS

V

SS

V

CC

V

CC

P

N

R

Digital input

V

SS

V

CC

MB91360G Series

22

(Continued)

(Continued)

Type

Circuit type

Remarks

Q

∑ I/O CMOS Input,

STOP control,

I

OH

=

4 mA, I

OL

=

4 mA

S

∑ I/O,

CMOS Schmitt-Trigger Input,

STOP control,

Pullup Resistor : 10 k

,

I

OH

=

4 mA, I

OL

=

4 mA

T

∑ CMOS Input

∑ can withstand high V

ID

for flash

programming

U

∑ CMOS Schmitt-Trigger Input,

Pullup Resistor: 50 k

,

3 V and 5 V input to the core

P

N

R

Stop control

Digital input

Digital output

Digital output

V

SS

P

N

R

P

V

SS

V

CC

Digital output

Digital output

Digital input

Stop control

R

Control signal

MD Input

P

N

R

Digital input

P

V

SS

V

SS

V

CC

V

CC

MB91360G Series

23

(Continued)

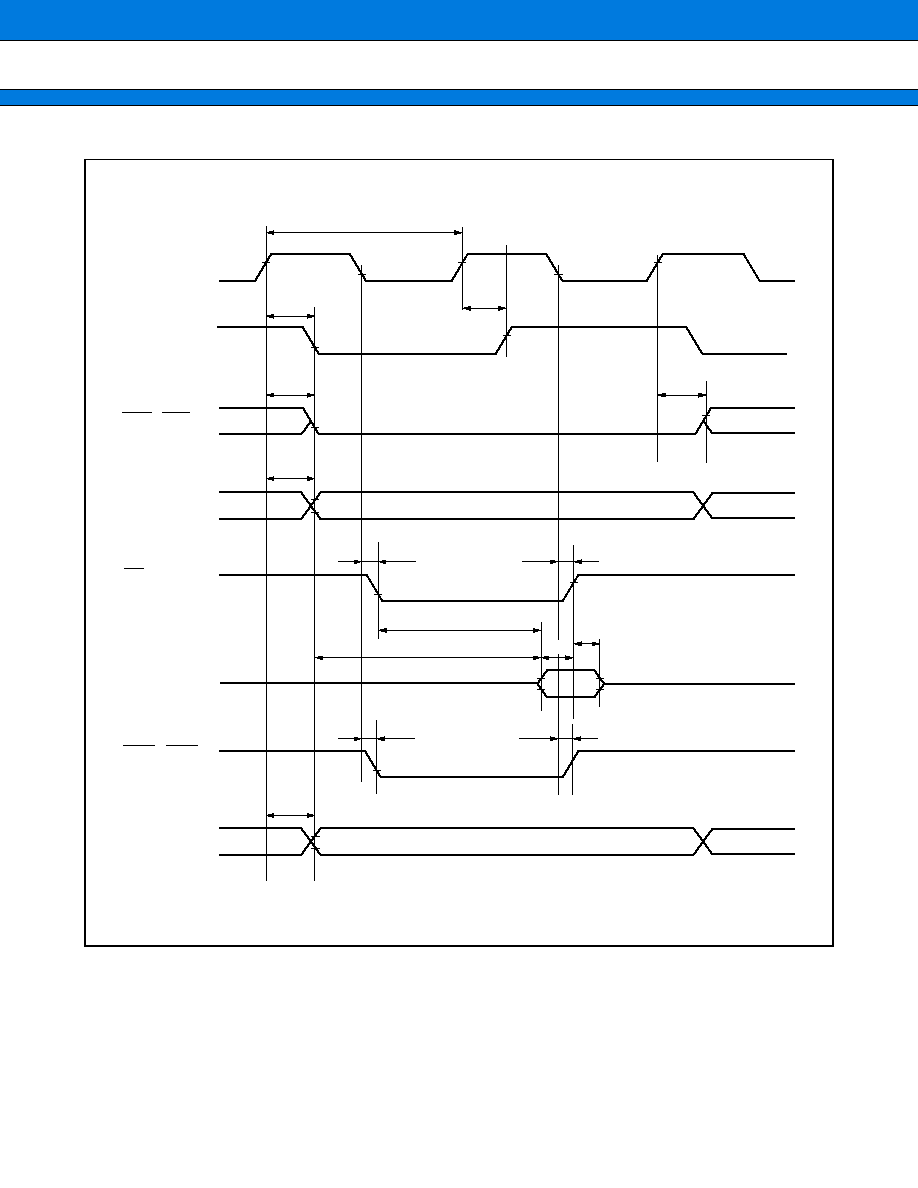

Note : Symbols used in circuit types (Common to all circuit diagrams)

P : P channel transistor

N : N channel transistor

R : Diffusion resistor

Type

Circuit type

Remarks

V

∑ I/O,

CMOS Schmitt-Trigger Input,

STOP control,

Pullup Resistor: 50 k

,,

I

OH

=

4 mA, I

OL

=

4 mA

W

∑ I/O,

CMOS Input; 3 V input

X

∑ Tristate Output, 3 V

Y

∑ I/O CMOS Input,

STOP control,

I

OH

=

3 mA, I

OL

=

3 mA,

in I

2

C mode operating as open drain

outputs

P

N

R

P

V

SS

V

CC

Digital output

Digital output

Digital input

Stop control

P

N

R

Digital input

Digital output

Digital output

V

SS

3 V

P

N

Digital output

Digital output

V

SS

3 V

P

N

R

Stop control

Digital input

Digital output

Digital output

V

SS

MB91360G Series

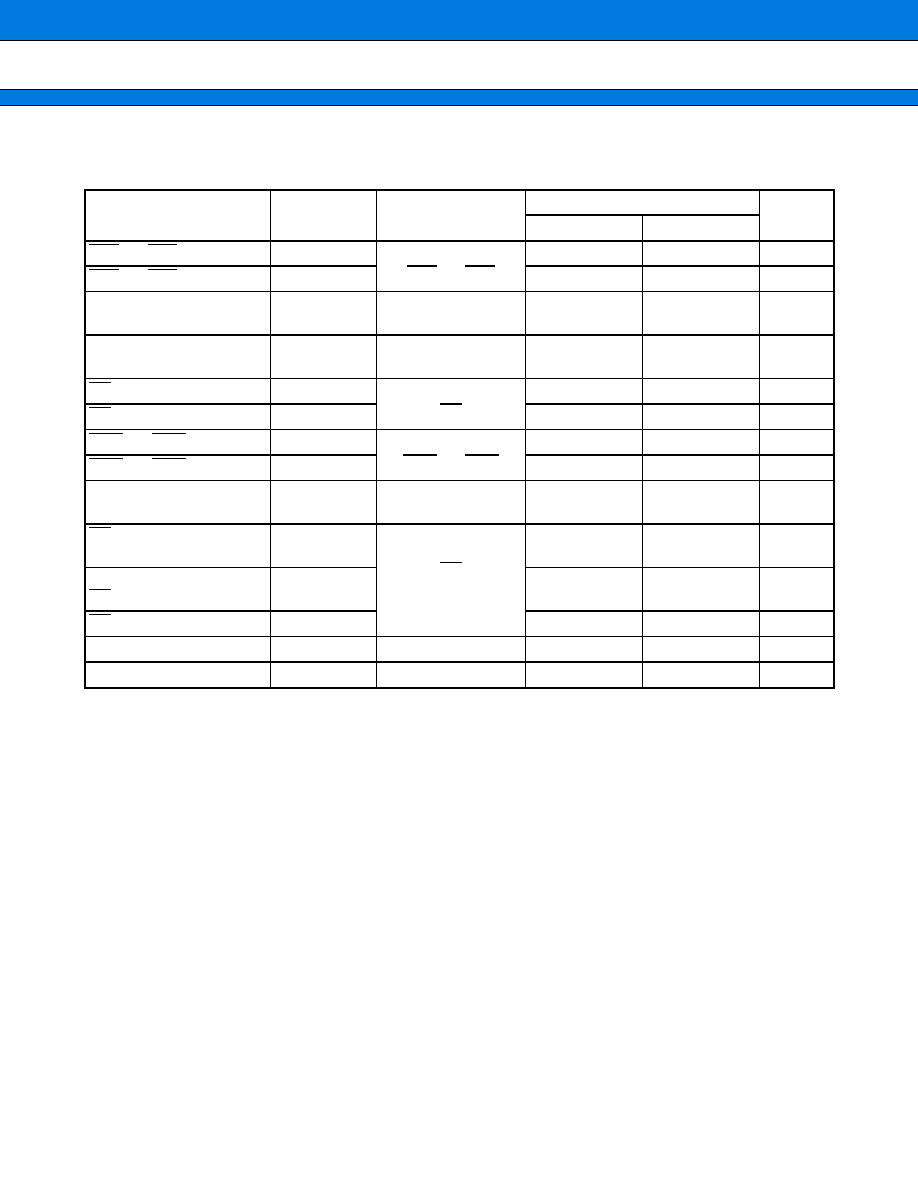

24

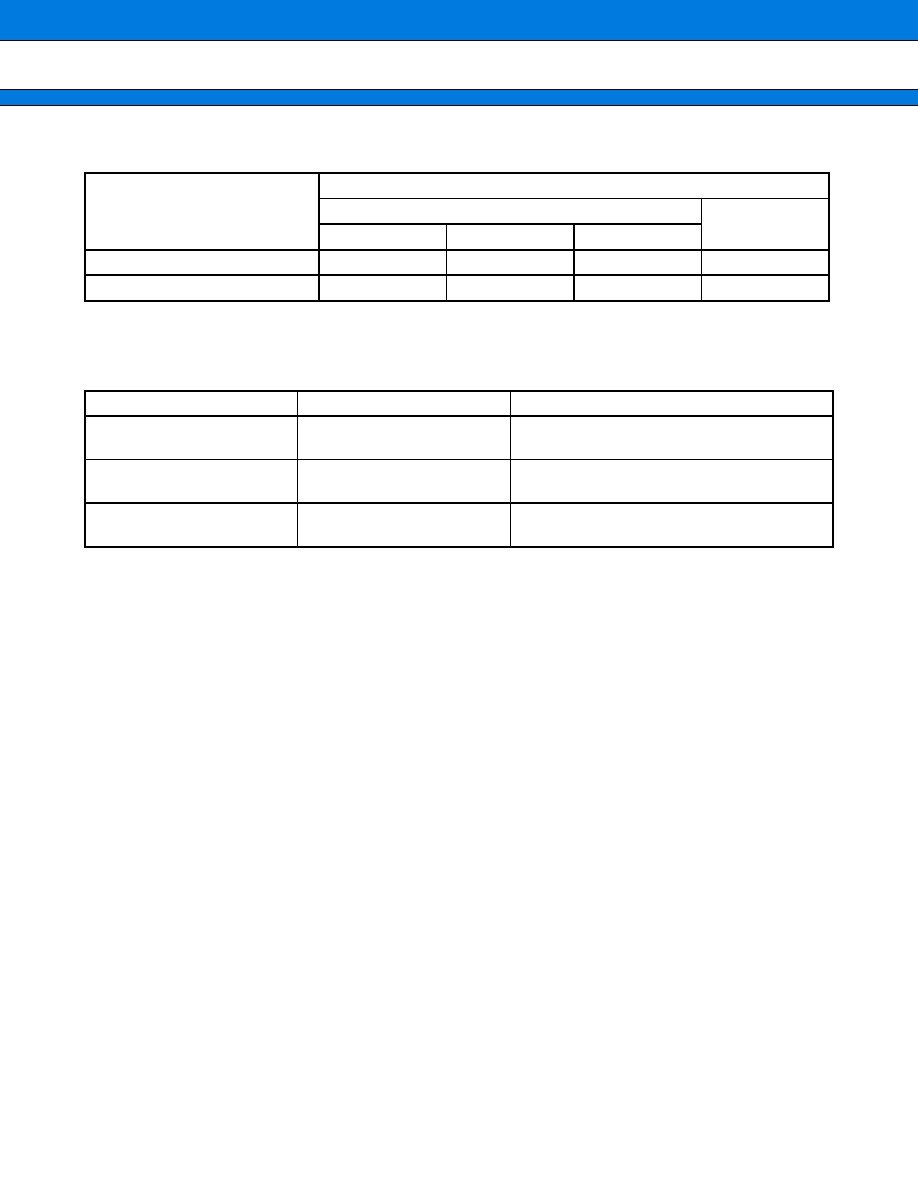

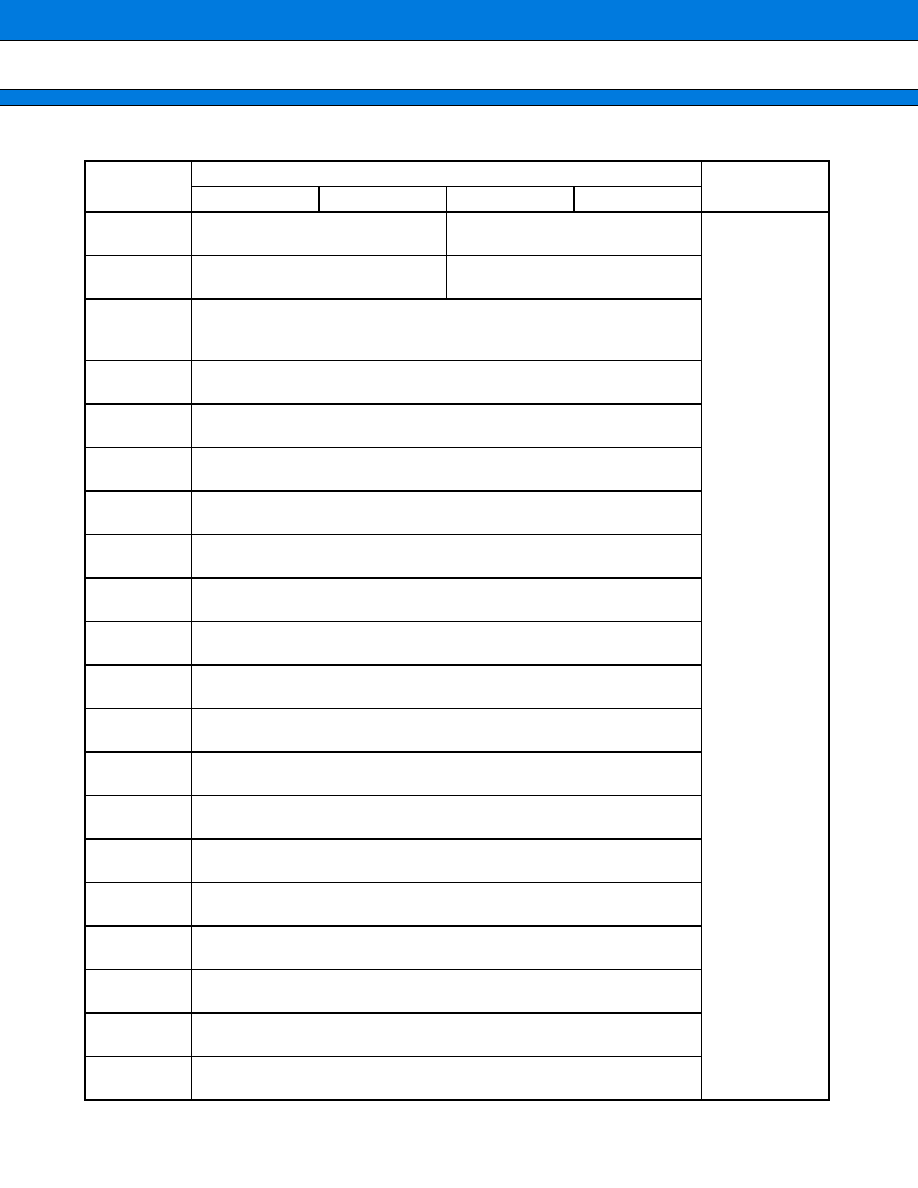

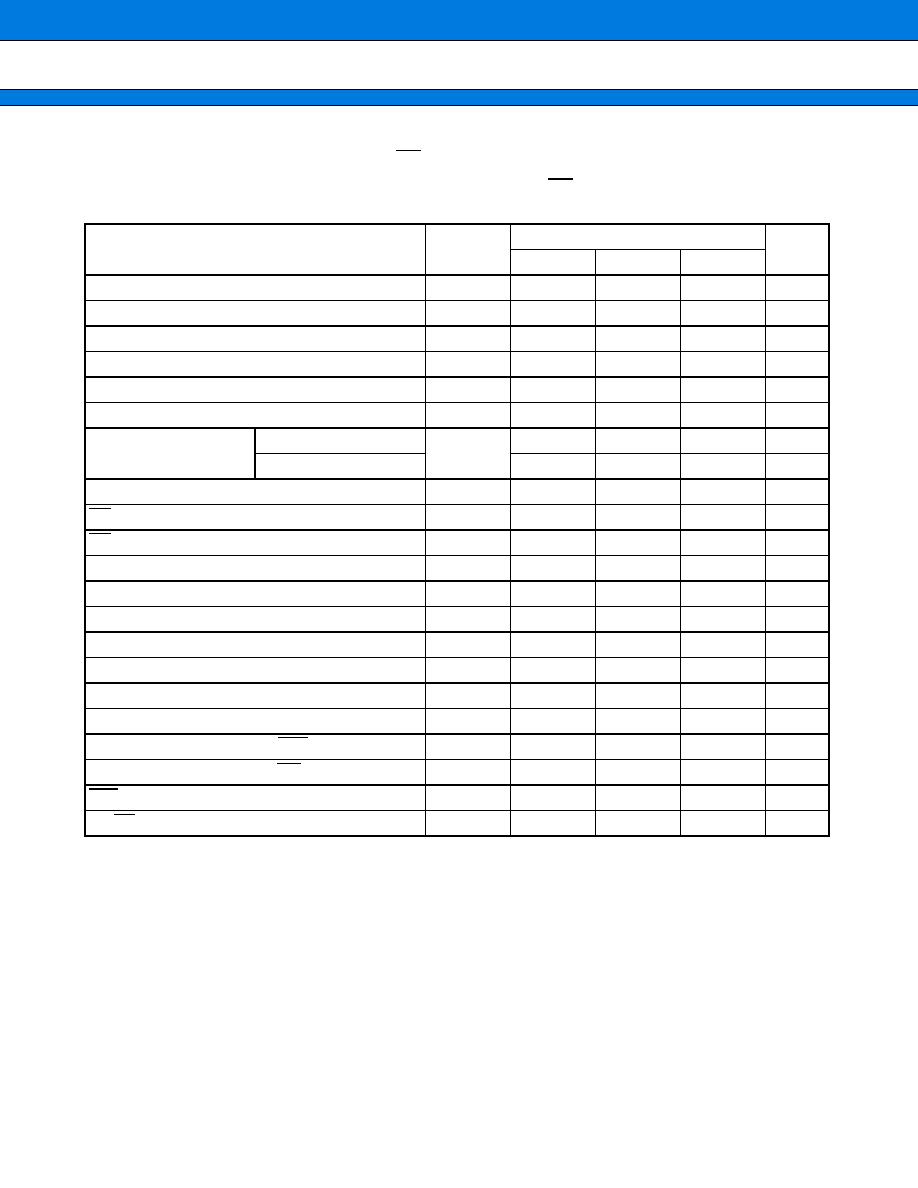

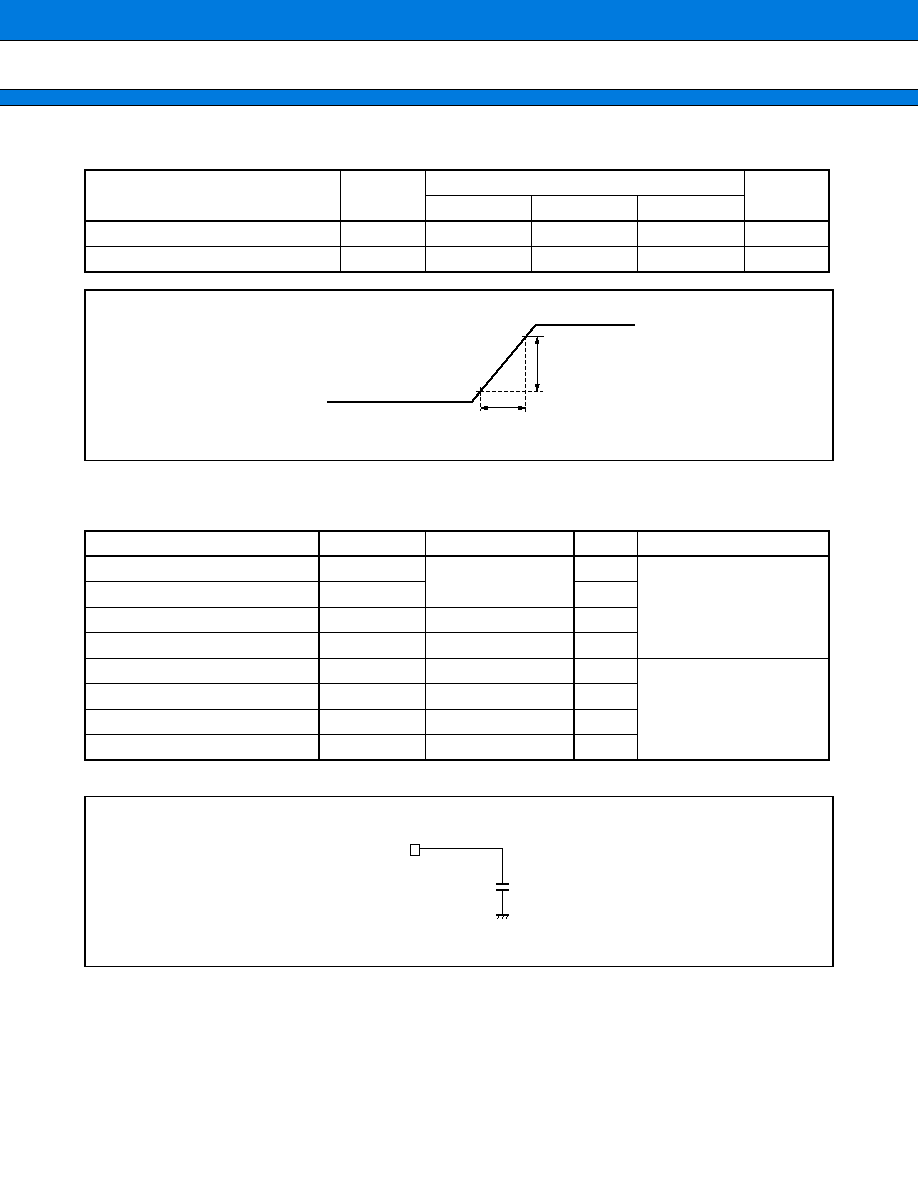

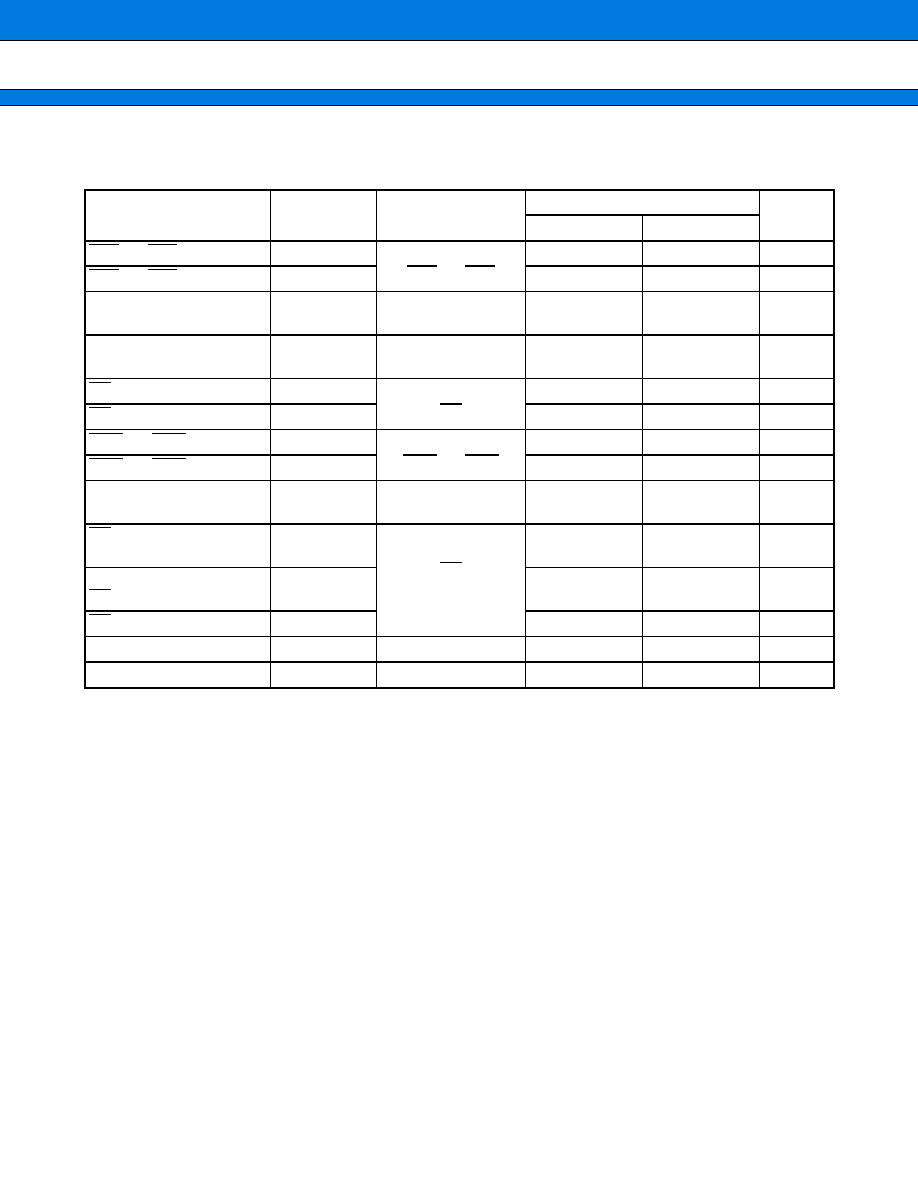

Circuit

Type

Description

A

I/O, I

OH

=

4 mA

/

I

OL

=

4 mA, CMOS Automotive Schmitt-Trigger Input, STOP control

B

I/O, I

OH

=

4 mA

/

I

OL

=

4 mA, CMOS Automotive Schmitt-Trigger Input, Analog Input, STOP control

C

Analog Output

D

Analog Input

E

CMOS Schmitt-Trigger Input, Pull-up Resistor: 50 k

,

F

CMOS Schmitt-Trigger Input

G

Tristate Output, I

OH

=

4 mA

/

I

OL

=

4 mA

H

4 MHz Oscillator Pin

I

32 kHz Oscillator pin

J

I/O, I

OH

=

14 mA

/

I

OL

=

24 mA, CMOS Automotive Schmitt-Trigger Input, STOP control (LED)

K

I/O, I

OH

=

30 mA

/

I

OL

=

30 mA, CMOS Automotive Schmitt-Trigger Input, STOP control, slew rate

improved for EMC (SMC)

L

I/O, I

OH

=

4 mA

/

I

OL

=

4 mA, CMOS Input; 5 V or 3 V input

M

I/O, I

OH

=

30 mA

/

I

OL

=

30 mA, CMOS Automotive Schmitt-Trigger Input, Analog Input, STOP control,

slew rate improved for EMC (SMC)

N

I/O, I

OH

=

4 mA

/

I

OL

=

4 mA, CMOS Input, Pulldown Resistor: 50 k

,; 5 V or 3 V input

O

CMOS Input, Pulldown Resistor: 50 k

,; 5 V or 3 V input

P

CMOS Input; 3 V input

Q

I/O, I

OH

=

4 mA

/

I

OL

=

4 mA, CMOS Input, STOP control

R

AVRL

/

AVRH Input

S

I/O, I

OH

=

4 mA

/

I

OL

=

4 mA, CMOS Input, STOP control, Pull-up Resistor: 10 k

,

T

CMOS Input, can withstand V

ID

for flash programming

U

CMOS Schmitt-Trigger Input, Pull-up Resistor: 50 k

,, 3.3 V and 5 V inputs to core

W

I/O, I

OH

=

4 mA

/

I

OL

=

4 mA, CMOS Input; 3 V input

X

Tristate Output, I

OH

=

4 mA

/

I

OL

=

4 mA, 3 V

Y

I/O, I

OH

=

3 mA

/

I

OL

=

3 mA (I

2

C) , CMOS Input, STOP control

MB91360G Series

25

s

HANDLING DEVICES

1.

Preventing latch-up

Latch-up may occur in a CMOS IC if a voltage greater than V

DD

or less than V

SS

is applied to an input or output

pin or if the voltage applied between V

DD

and V

SS

exceeds the rating. If latch-up occurs, the power supply current

increases rapidly resulting in thermal damage to circuit elements. Therefore, ensure that maximum ratings are

not exceeded in circuit operation.

2.

Connecting unused pins

Leaving unused input pins open may result in misbehavior or latch up and possible permanent damage of the

device. Therefore they must be tied to V

DD

or V

SS

through resistors. In this case those resistors should be more

than 2 KOhm.

Unused bidirectional pins should be set to the output state and can be left open, or the input state with the above

described connection.

The resistor of more than 2 KOhm is used to limit currents through the protection diodes. In case of voltages at

the not used pin of 0.3 V or more below V

SS

or 0.3 V or more above V

DD

currents which could cause latch-up will

flow through those diodes.

3.

External reset input

When inputting an "L" level to the INIT pin, hold this low level at the INIT pin long enough so that after release

of the low level at INIT and the passing of the built in waiting time stable oscillation of the oscillation circuit is

achieved. INIT must be pulled low for at least 8 cycles of the 4 MHz oscillation clock.

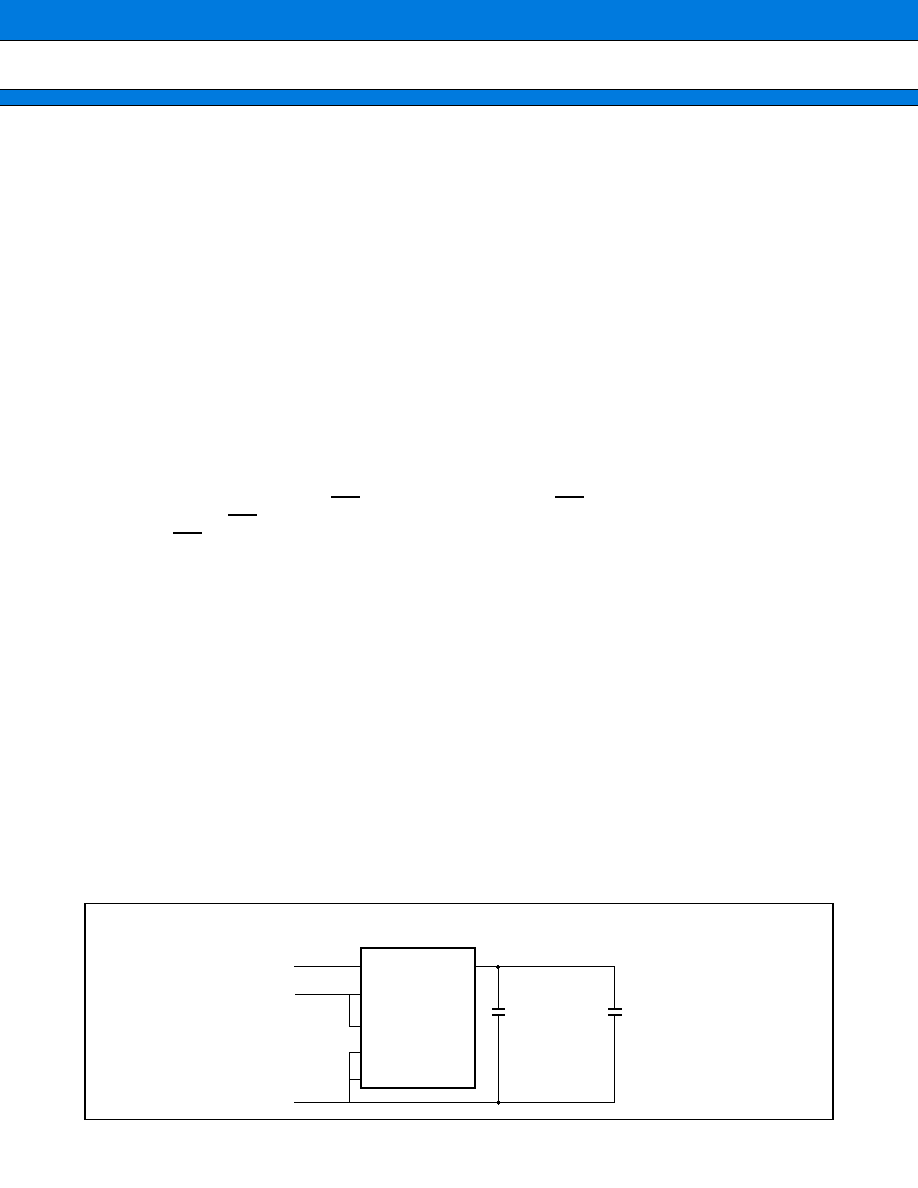

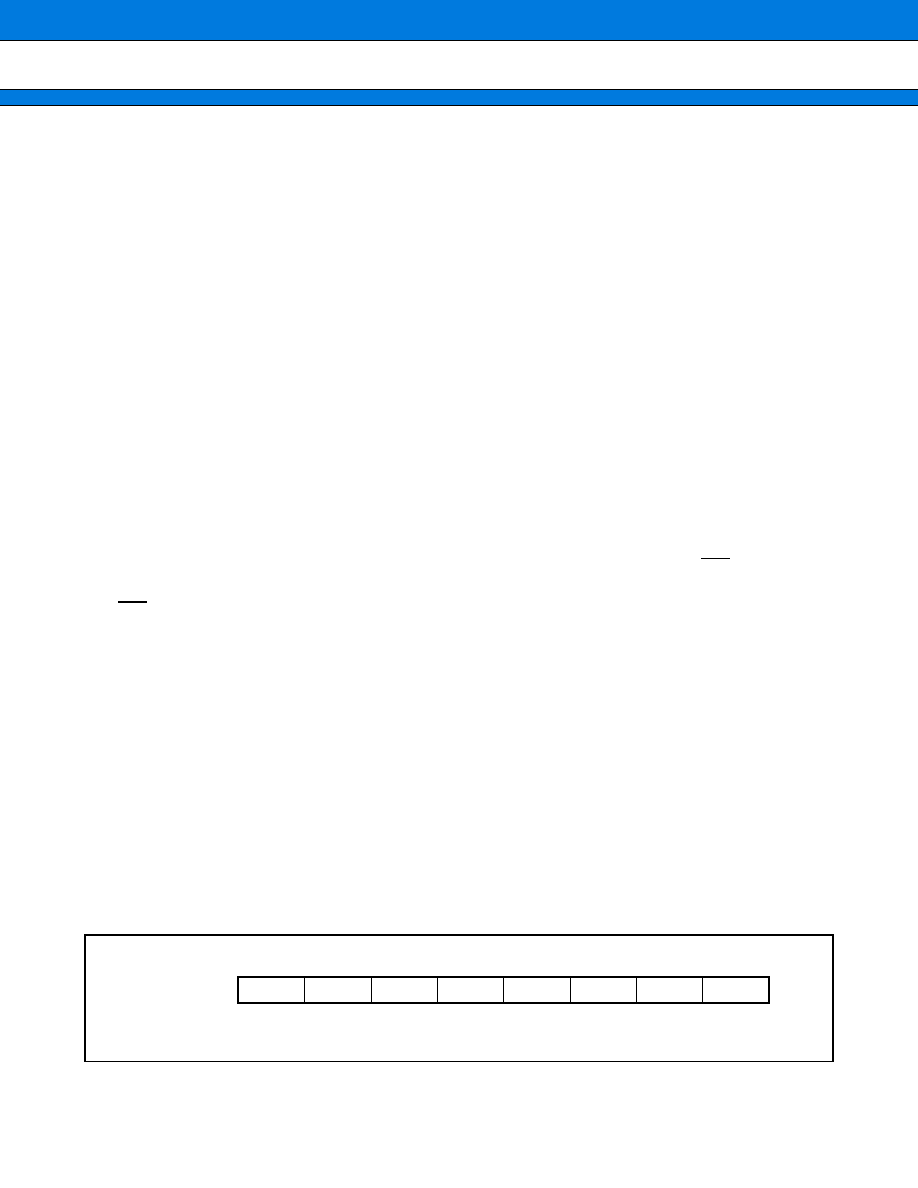

4.

Power supply pins

All V

DD

pins should be connected to the same potential (exception can be the external bus interface on F361GA

and F362GA) . The analogue supply voltage (AV

CC

) must not be turned on before the digital supply voltage. If

the external bus interface is supplied with 3.3 V this voltage also must not be turned on before the 5 V digital

voltage has been switched on. If the supply voltage to the external bus interface is switched off (it may not be

tristate but should be pulled low) it must be made sure that all related signals do not have a voltage higher than

this pulled down supply.

When multiple V

DD

and V

SS

pins are provided, be sure to connect all V

DD

and V

SS

pins to the power supply or

ground externally. Although pins at the same potential are connected together in the internal device design so

as to prevent malfunctions such as latch-up, connecting all V

DD

and V

SS

pins appropriately minimizes unwanted

radiation, prevents malfunction of strobe signals due to increases in the ground level, and keeps the overall

output current rating.

Also, take care to connect V

DD

and V

SS

to current source in the lowest possible impedance.

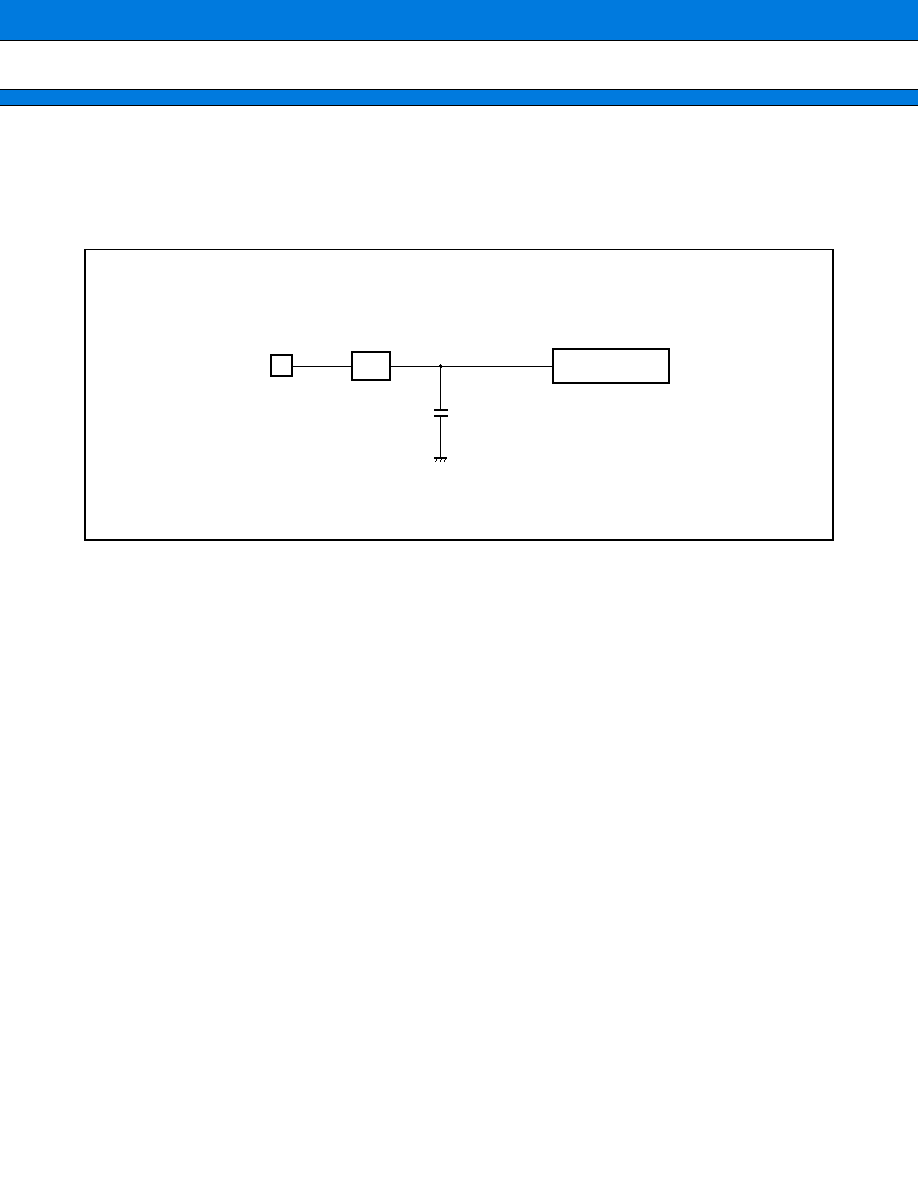

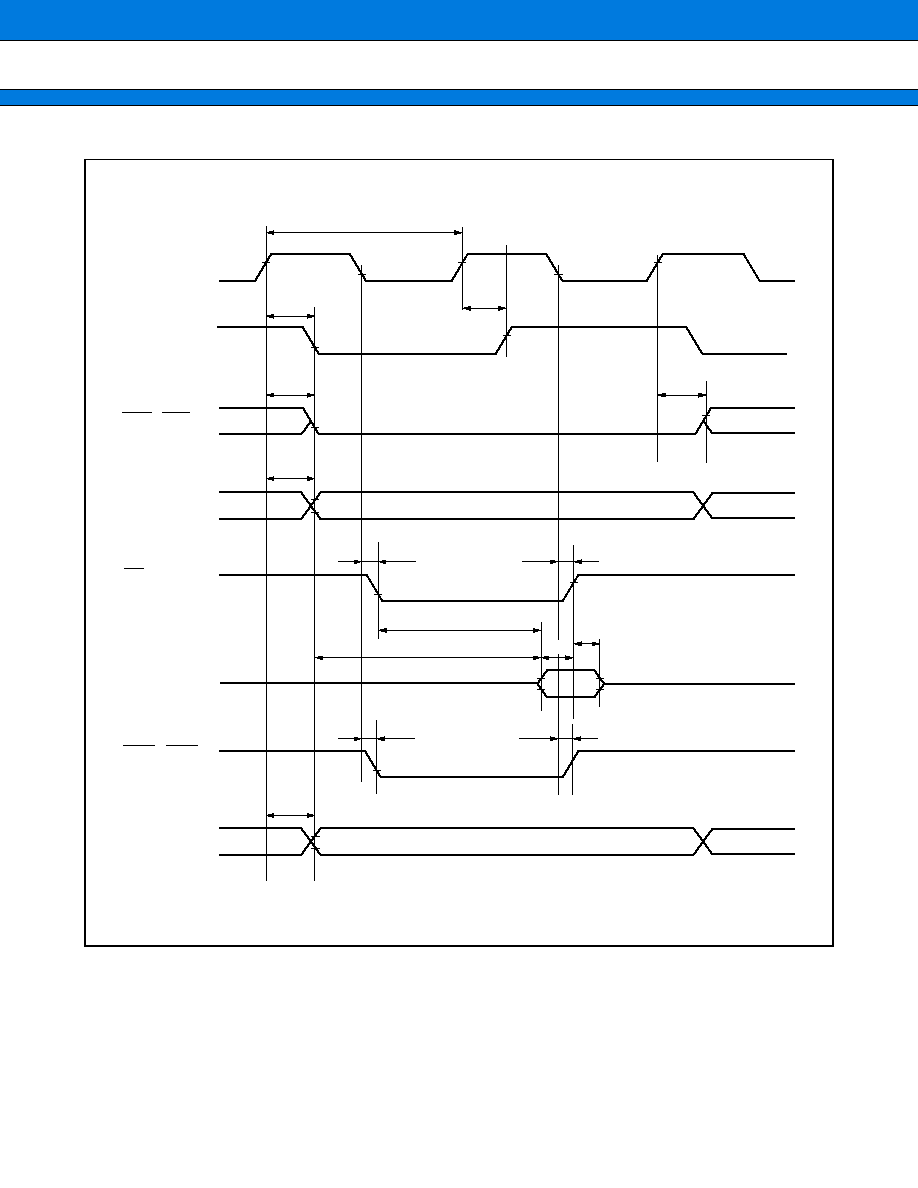

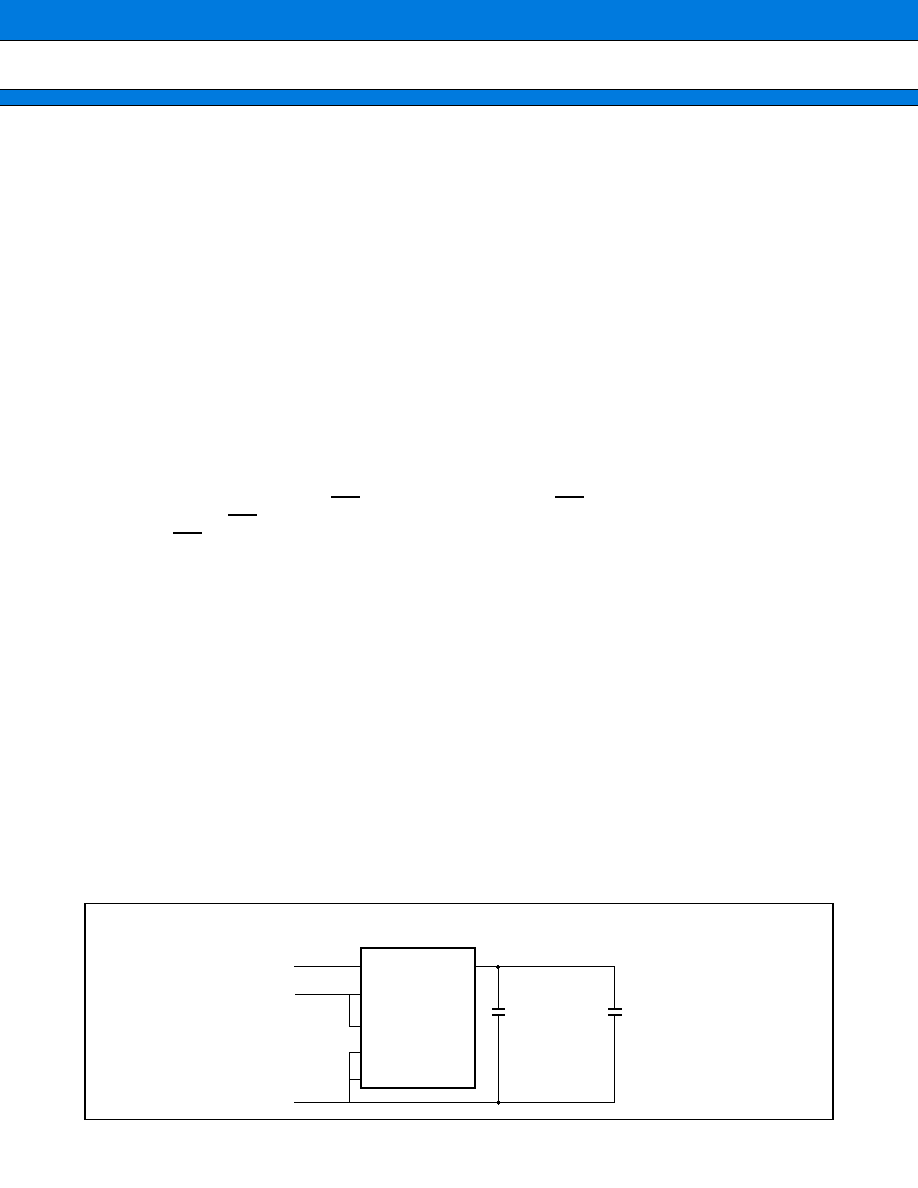

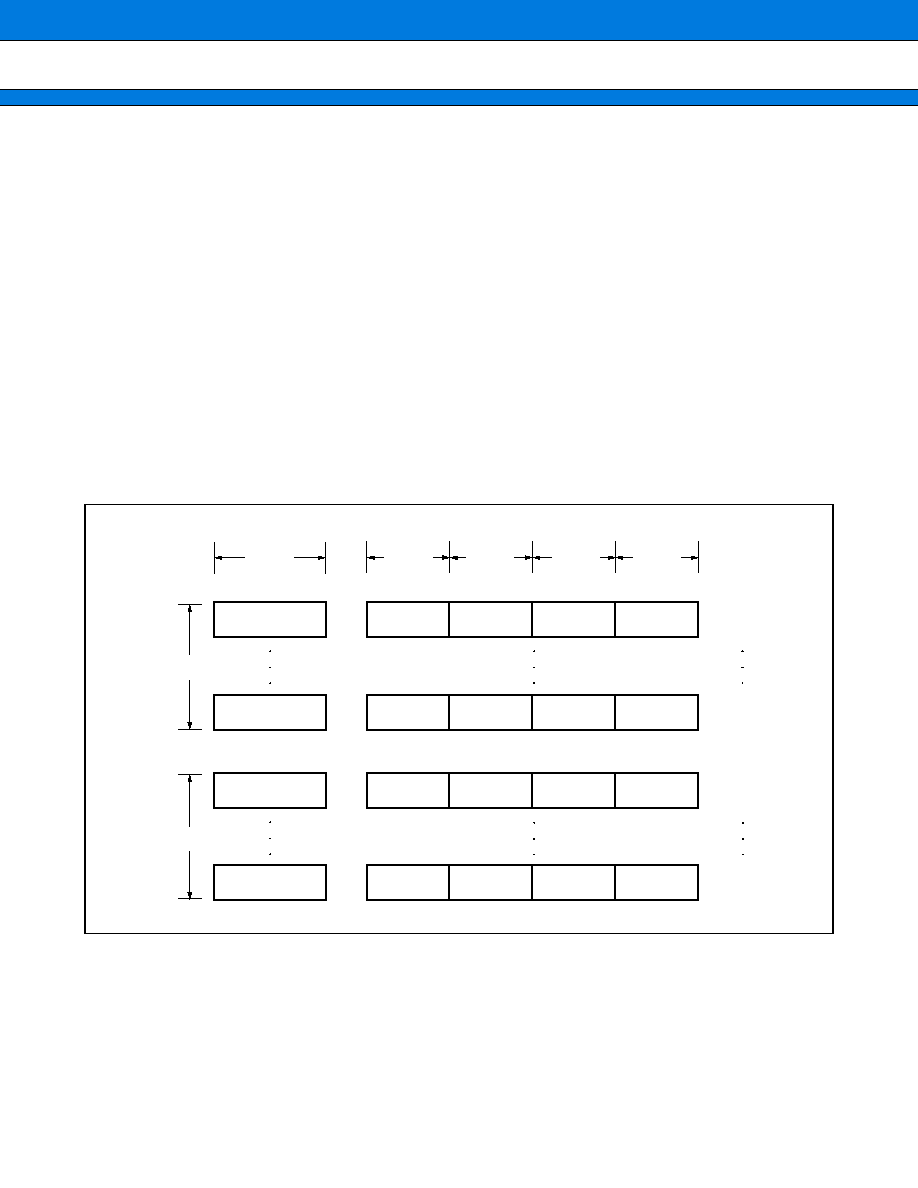

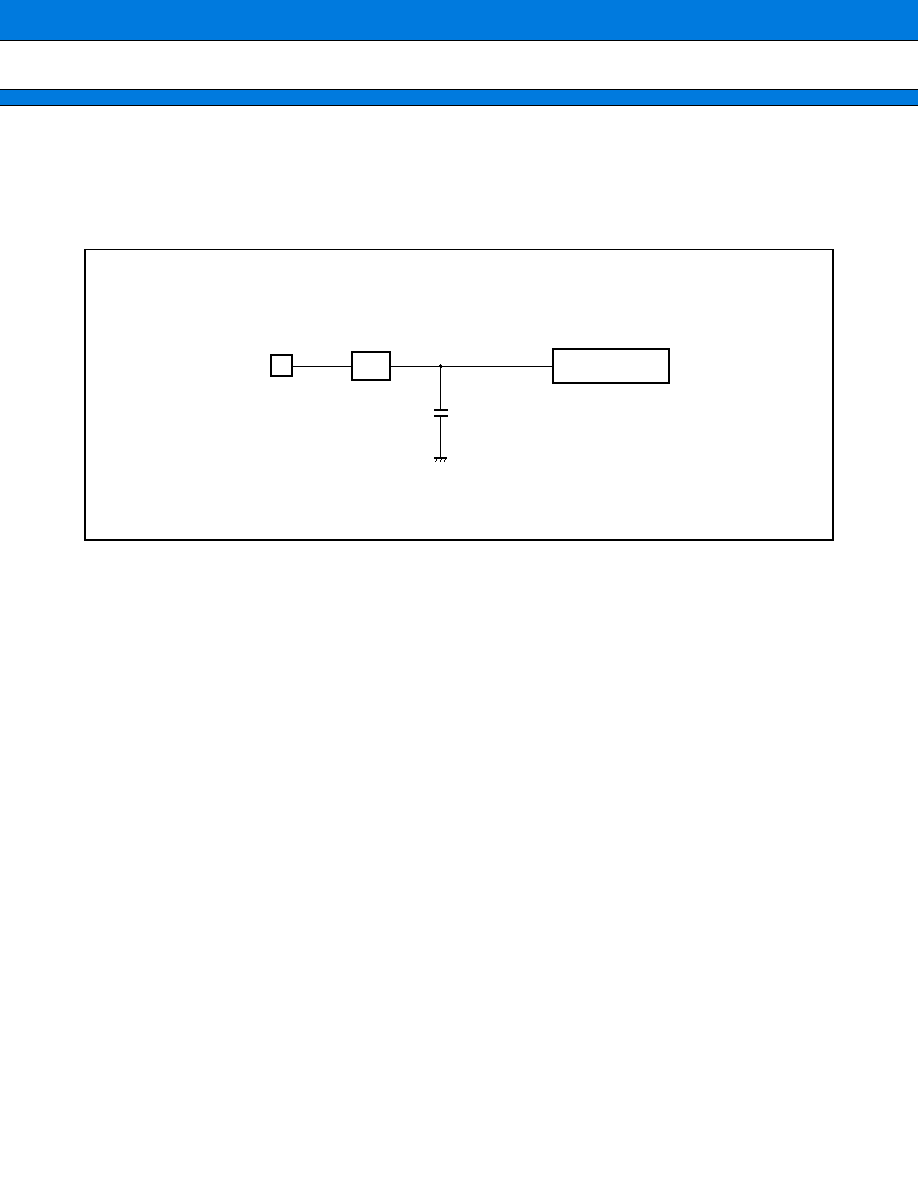

Connection of a ceramic bypass capacitor of approximately 0.1

µ

F between V

DD

and V

SS

close to the device is

recommended.

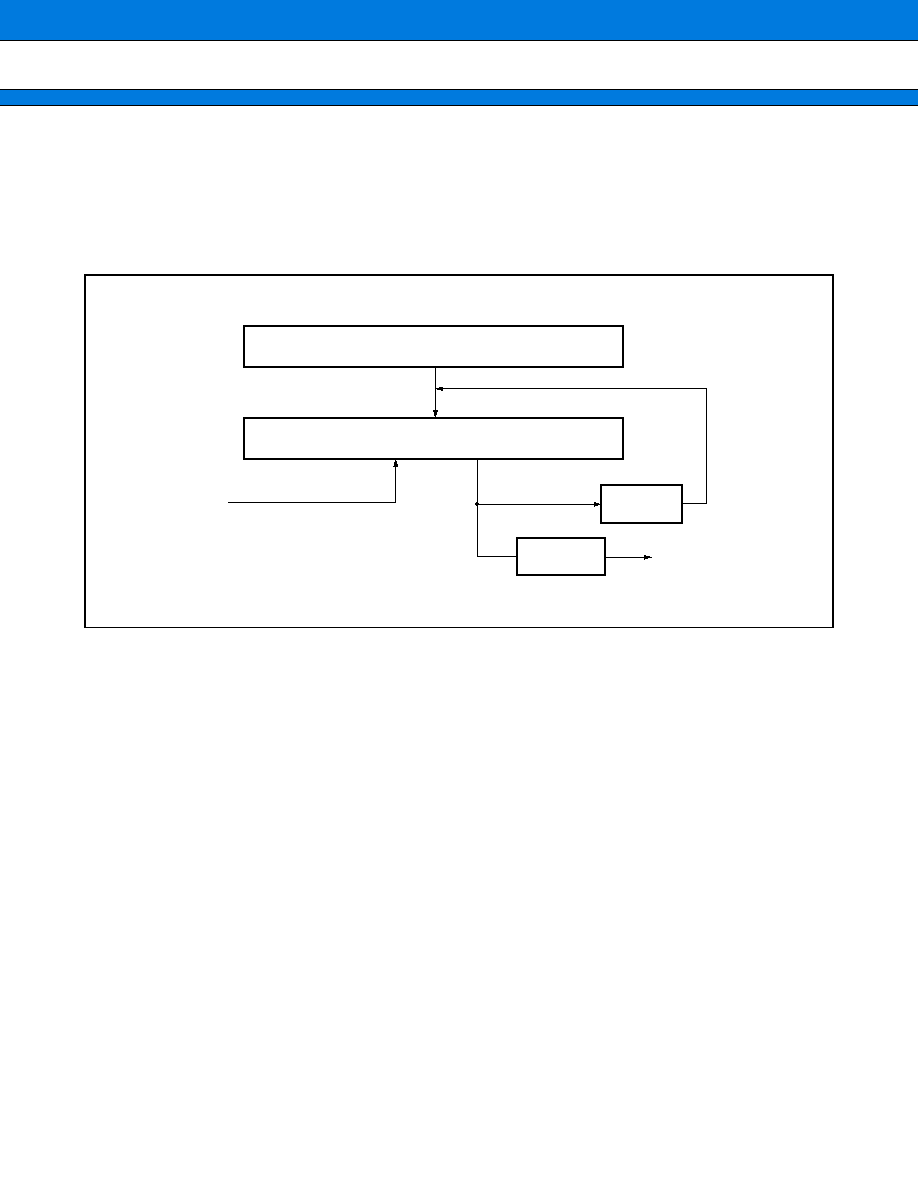

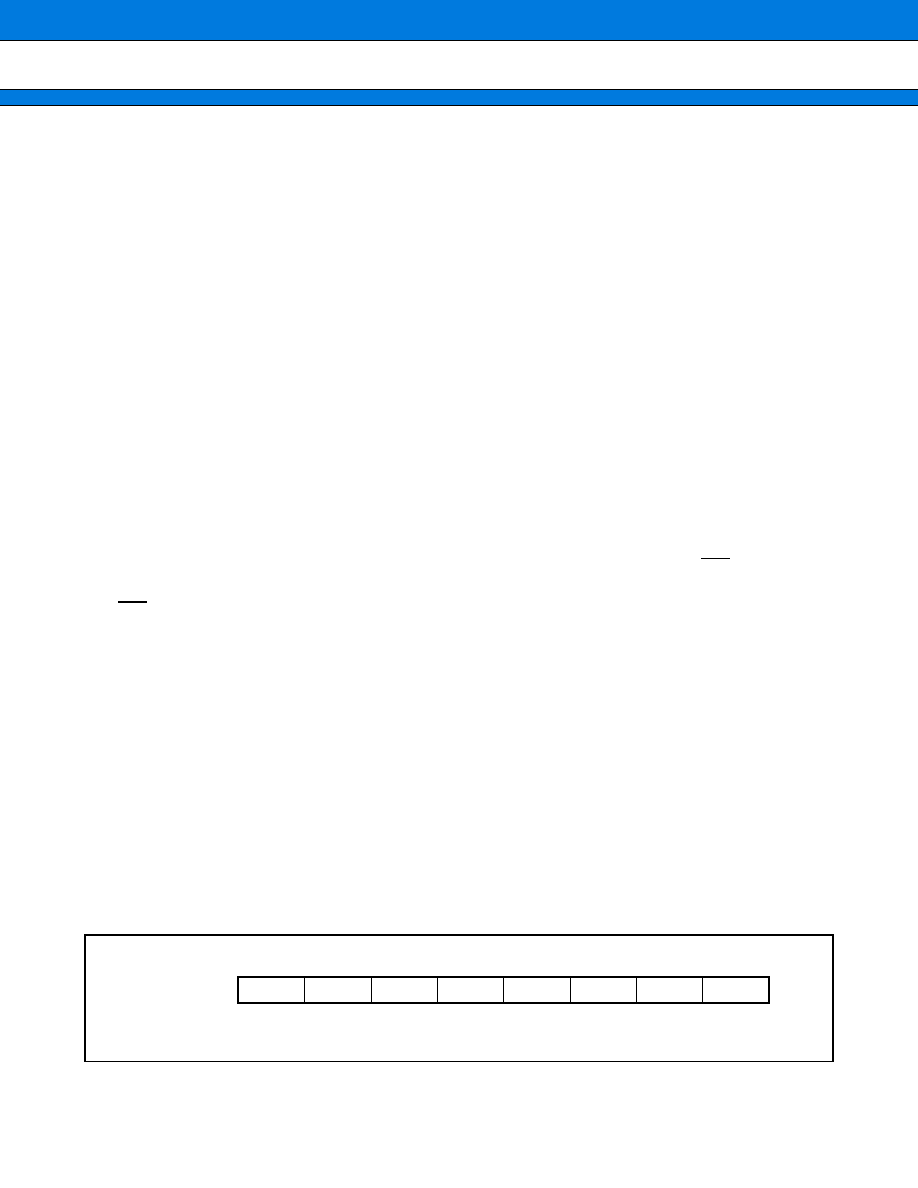

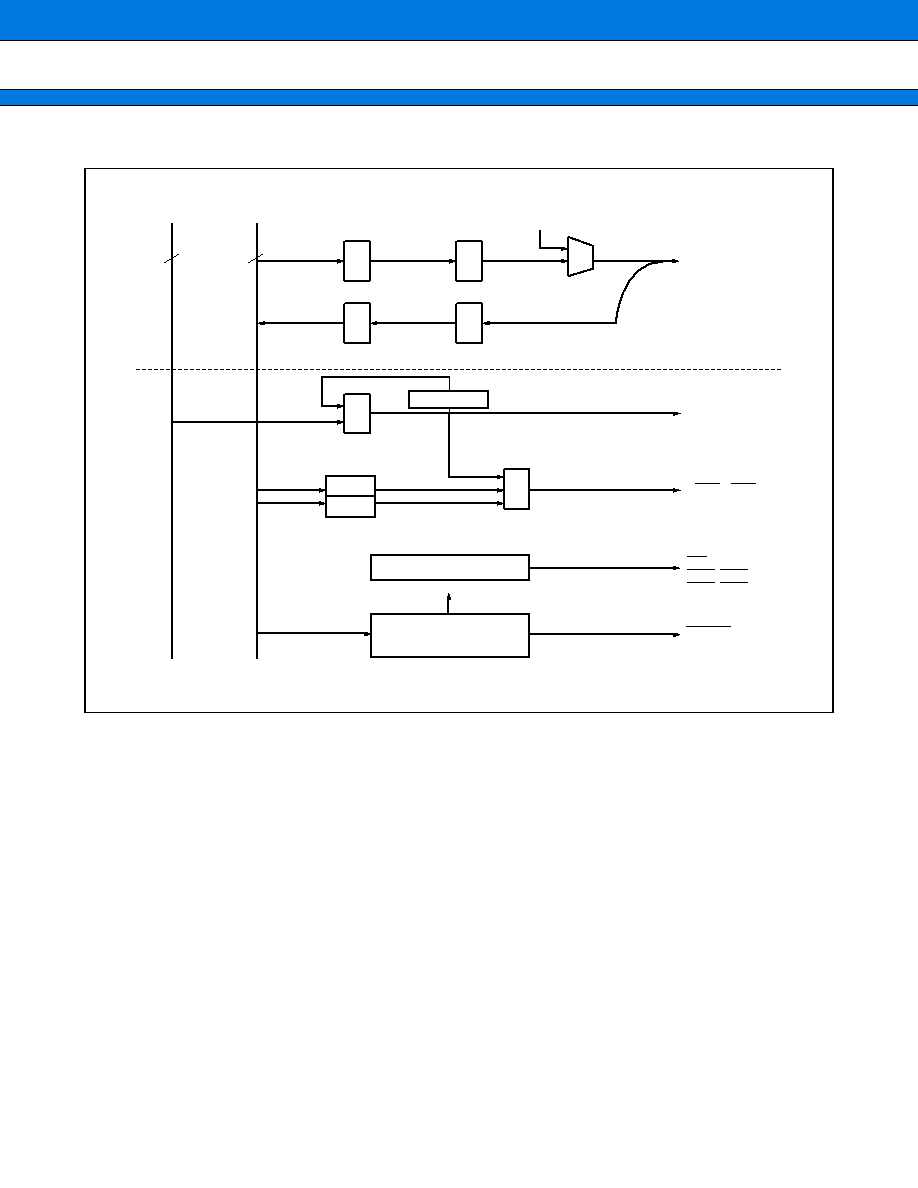

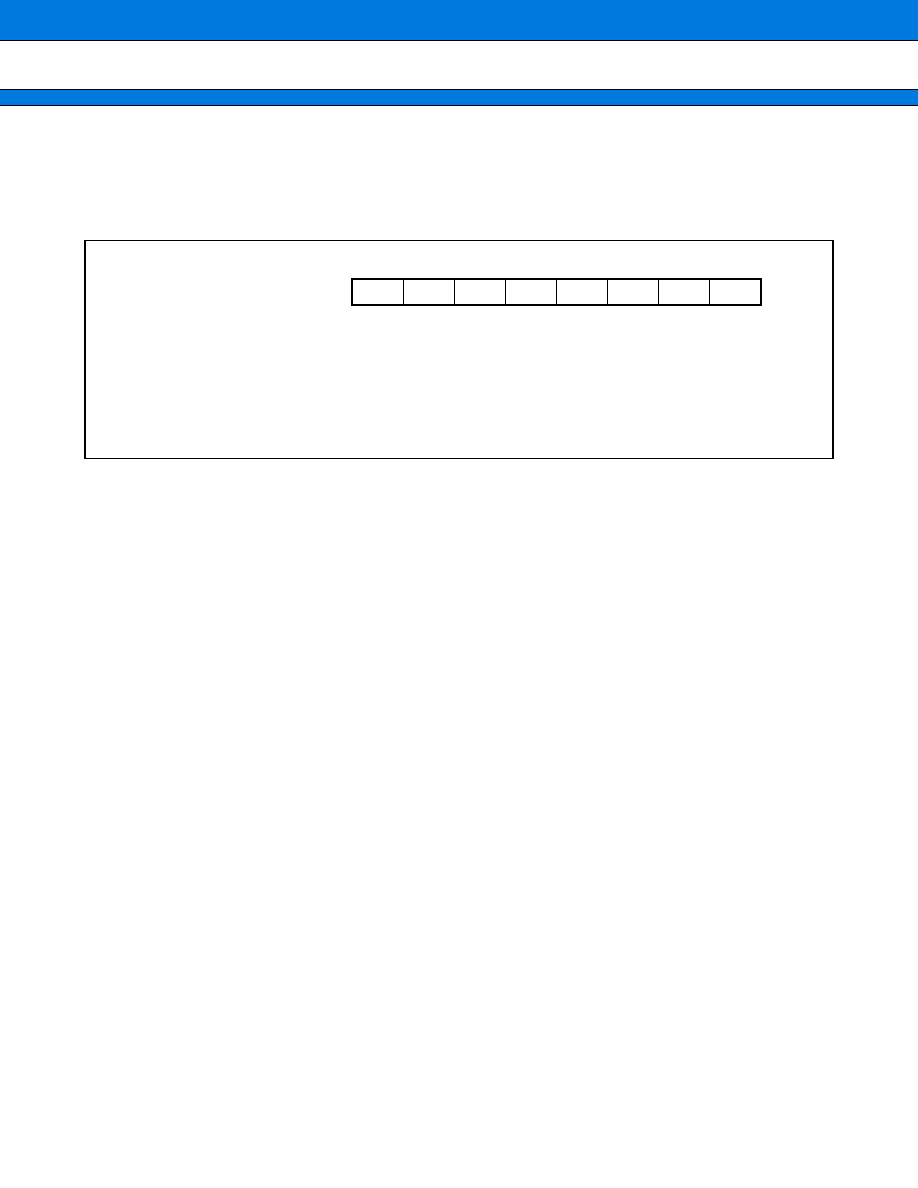

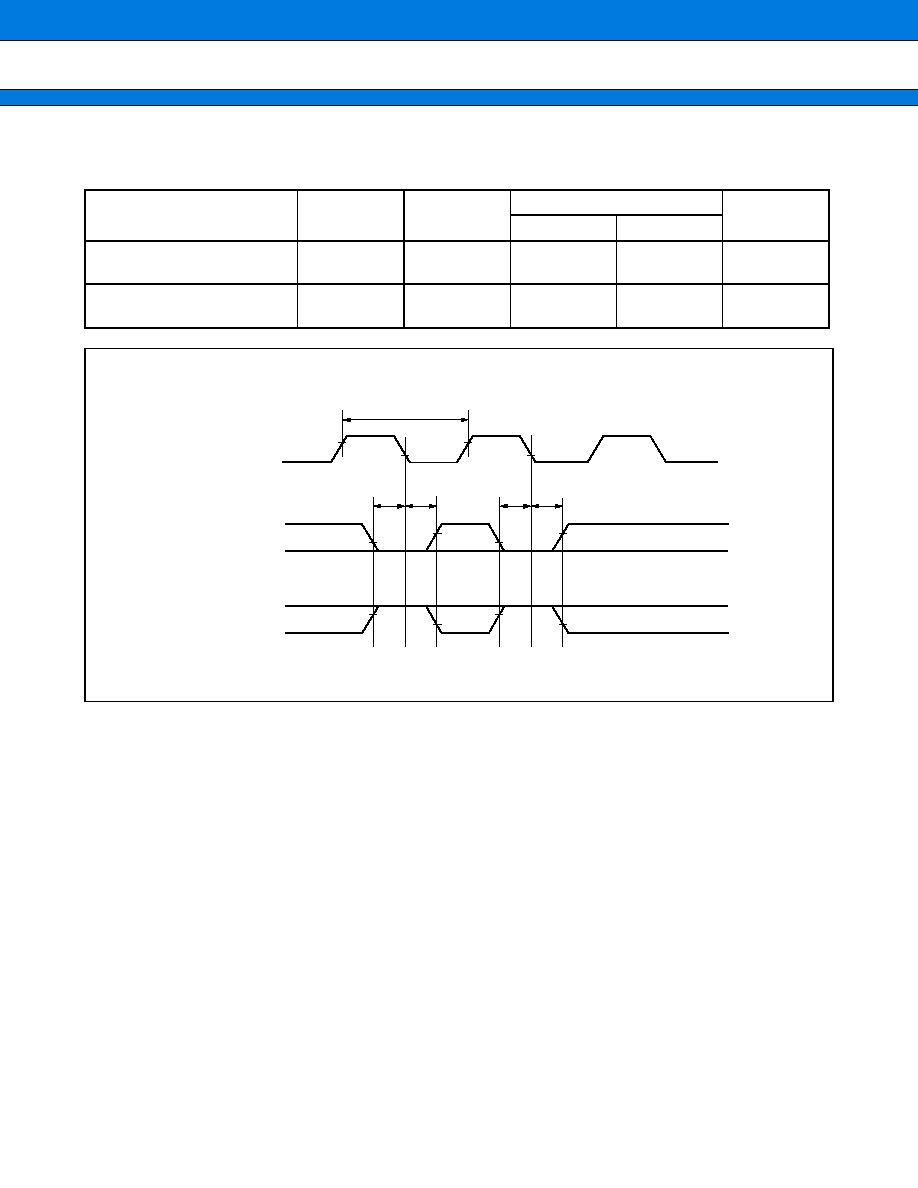

The MB91360G series contains a regulator. To use the device with the 5-V power supply, supply 5-V power to

the V

CC

pins and be sure to connect a bypass capacitor of 10

µ

F parallel to 10 nF to the V

CC

3C pin for the regulator.

5 V

5 V

10

µ

F

10 nF

V

CC

3C

V

CC

AV

CC

AVRH

AV

SS

V

SS

GND

[Use with 5-V power supply]

MB91360G Series

26

5.

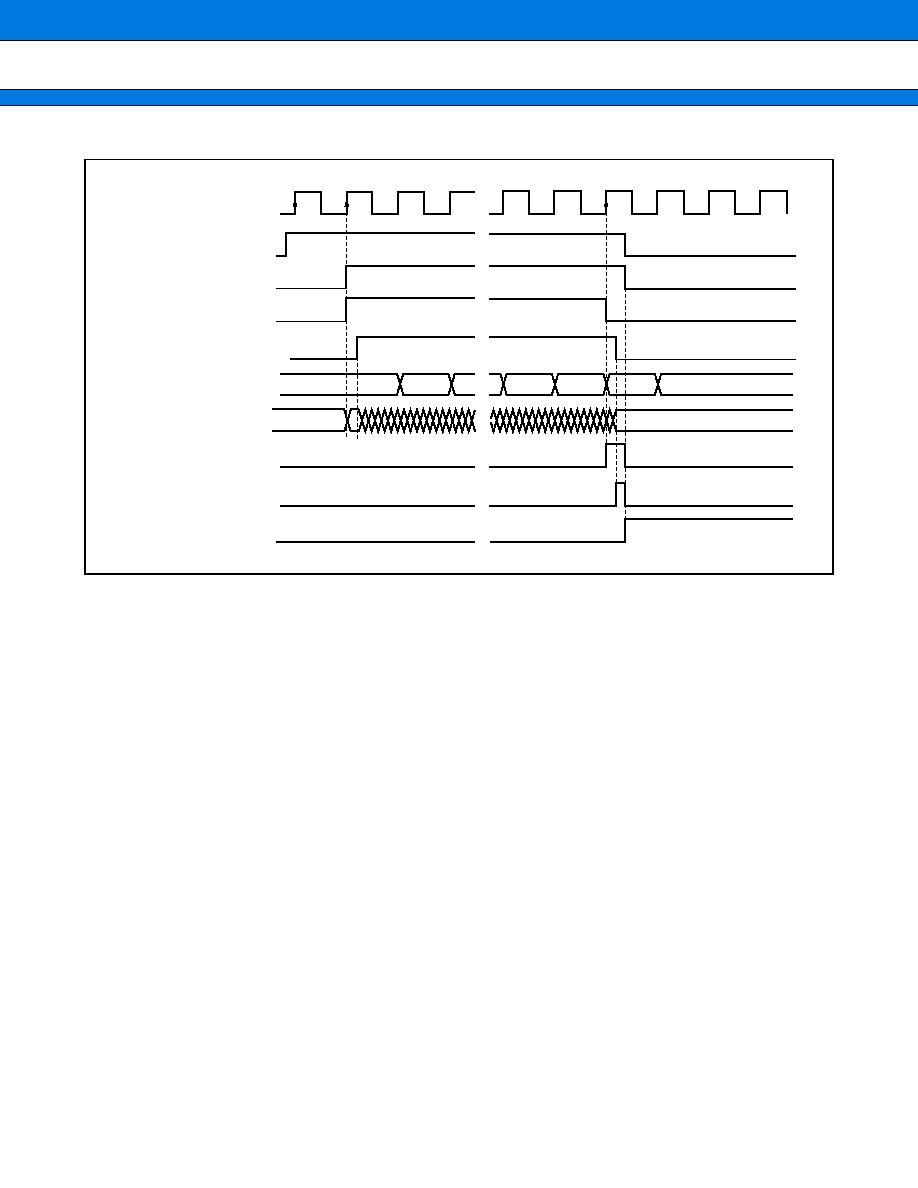

Crystal oscillator circuit

Noise in the vicinity of the X0 and X1 pins can be a cause of device malfunction. Design the circuit board so that

X0, X1, the crystal oscillator (or ceramic oscillator) , and the bypass capacitor to ground are located as close to

the device as possible.

A printed circuit board design that surrounds the X0 and X1 pins with ground provides for stable operation and

is strongly recommended.

6.

Mode pins

Connect the mode pins (MD0 to MD2) directly to V

DD

or V

SS

.

To prevent the device unintentionally entering test mode due to noise, lay out the printed circuit board so as to

minimize the distance from the mode pins to V

DD

or V

SS

and to provide a low-impedance connection.

7.

Turning the power supply on

Immediately after power on always execute INIT at the INIT pin (start with a low level at the INIT pin) . Hold this

low level at the INIT pin long enough so that after release of the low level at INIT and the passing of the built in

waiting time stable oscillation of the oscillation circuit is achieved. INIT must be pulled low for at least 8 cycles

of the 4 MHz oscillation clock.

The analogue supply voltage (AV

CC

) must not be turned on before the digital supply voltage. If the external bus

interface is supplied with 3.3 V this voltage also must not be turned on before the 5 V digital voltage has been

switched on.

8.

A state in turning power on

Output pin level is not guranteed while supply voltage does not reach minimum operation voltage in turning

power on.

MB91360G Series

27

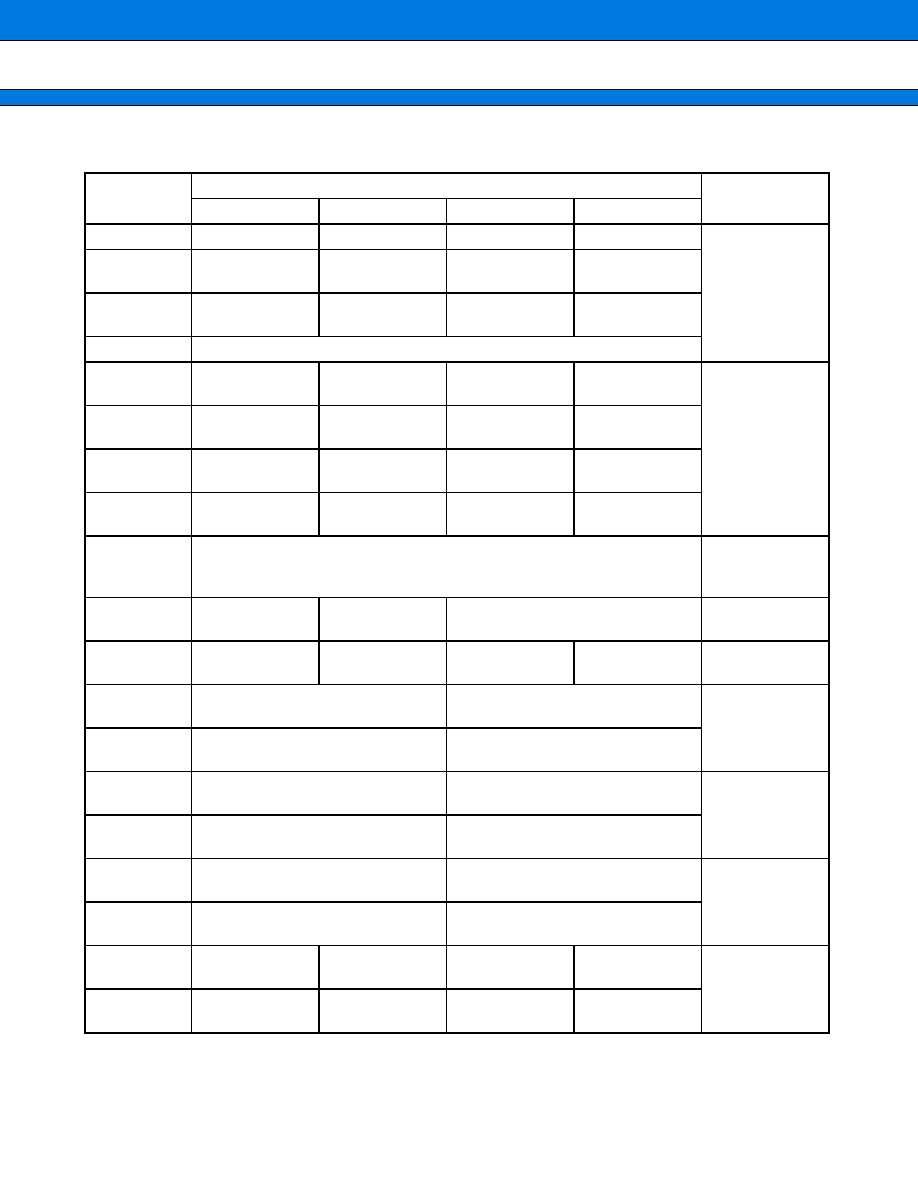

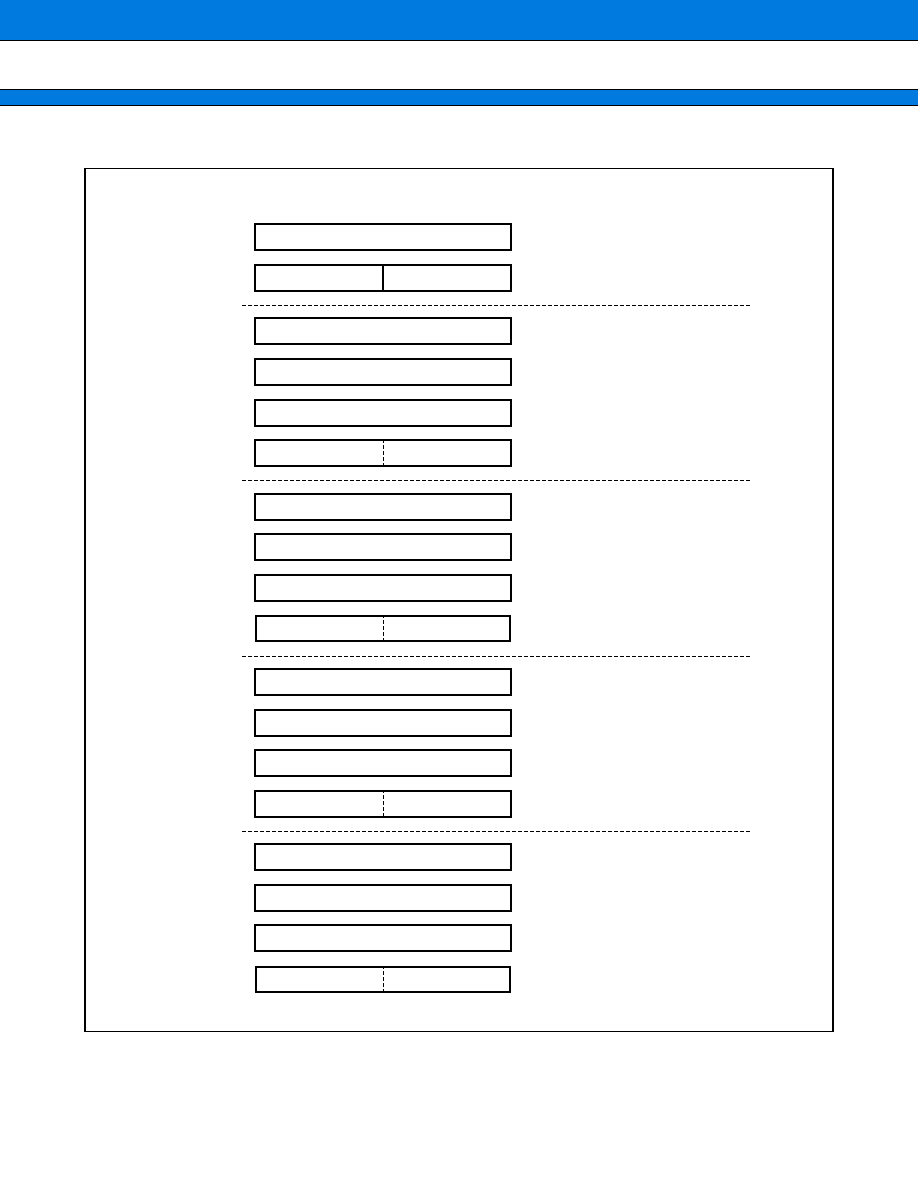

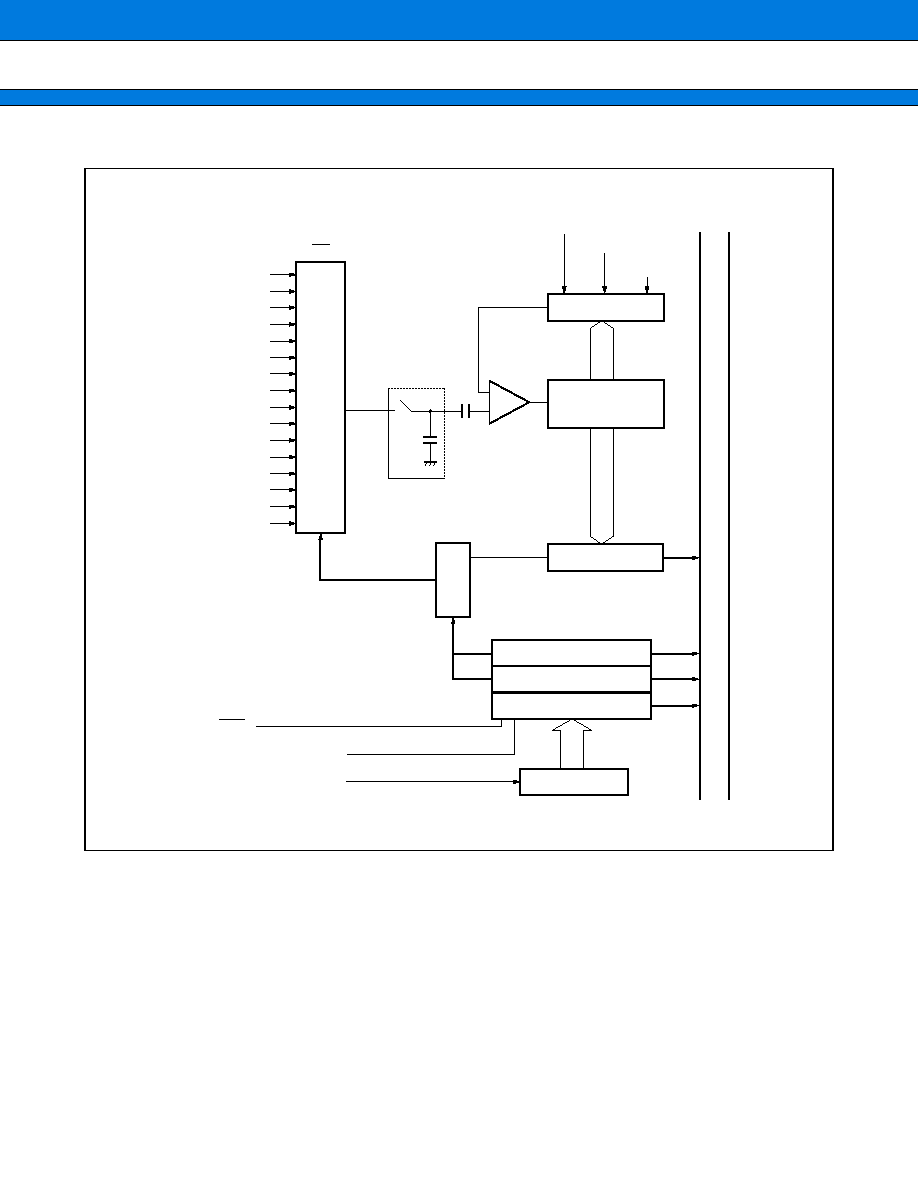

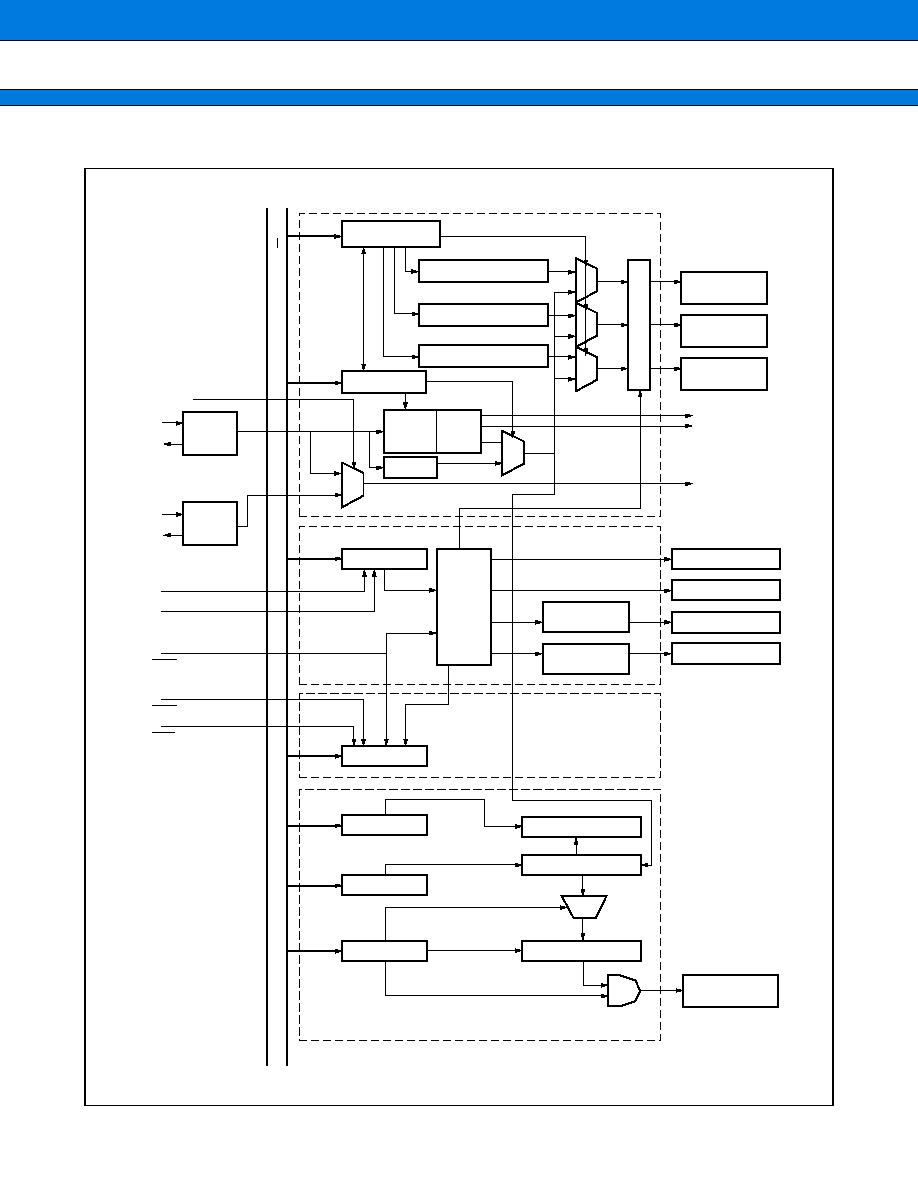

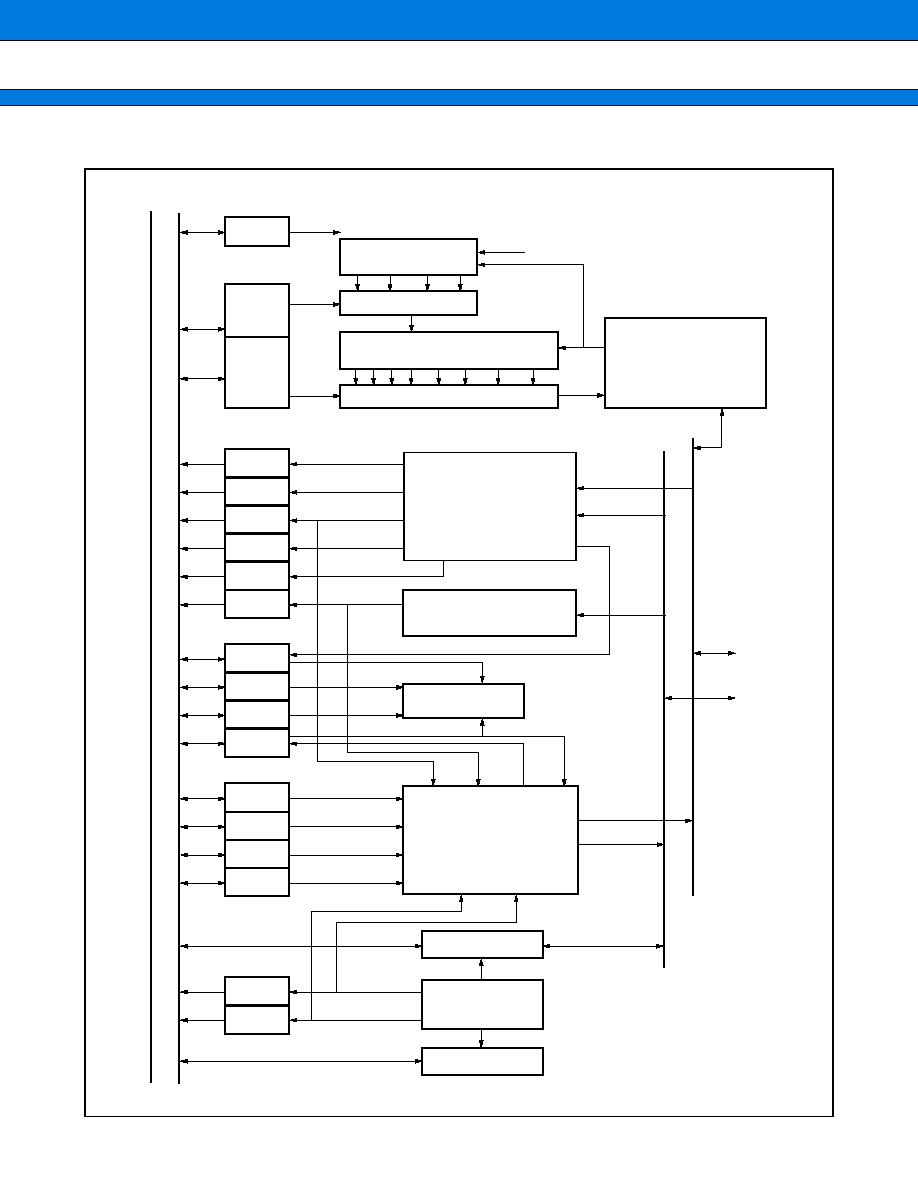

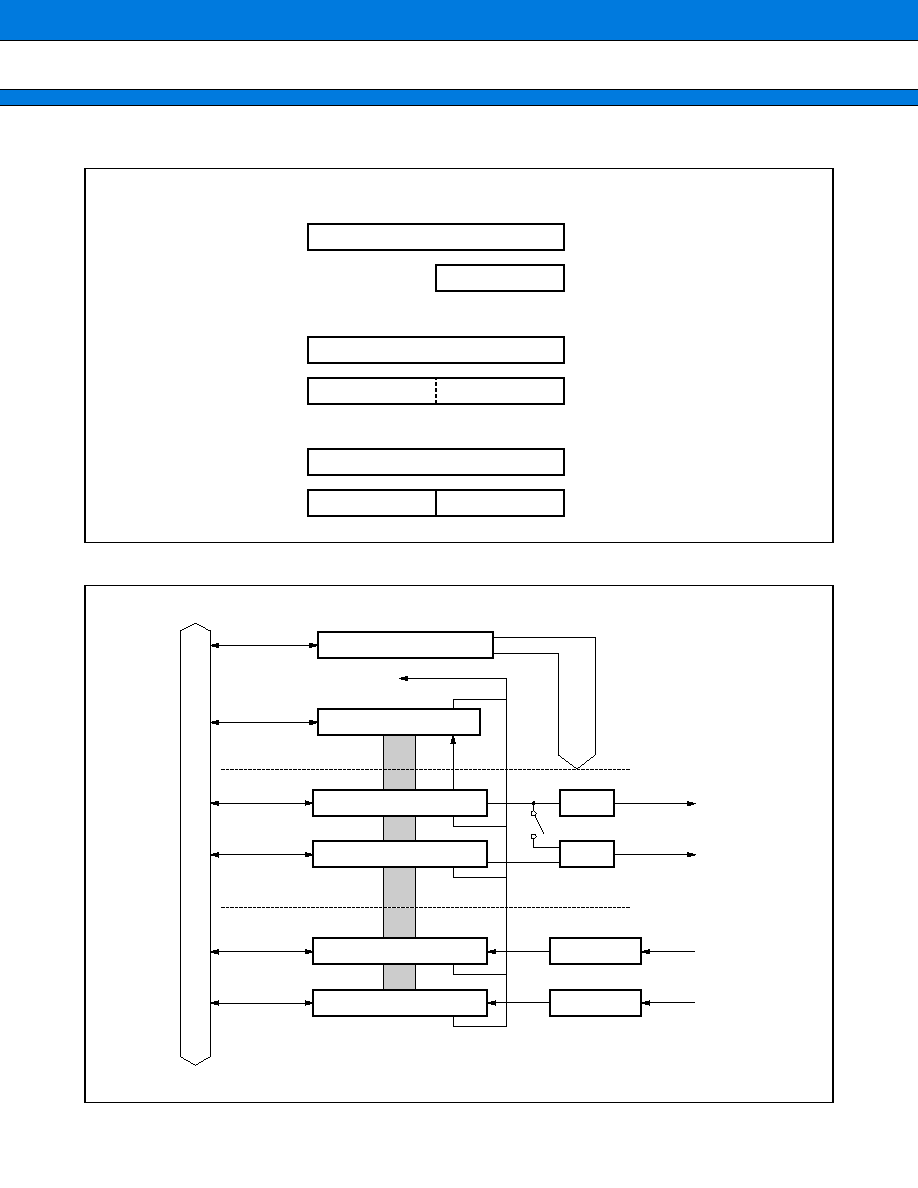

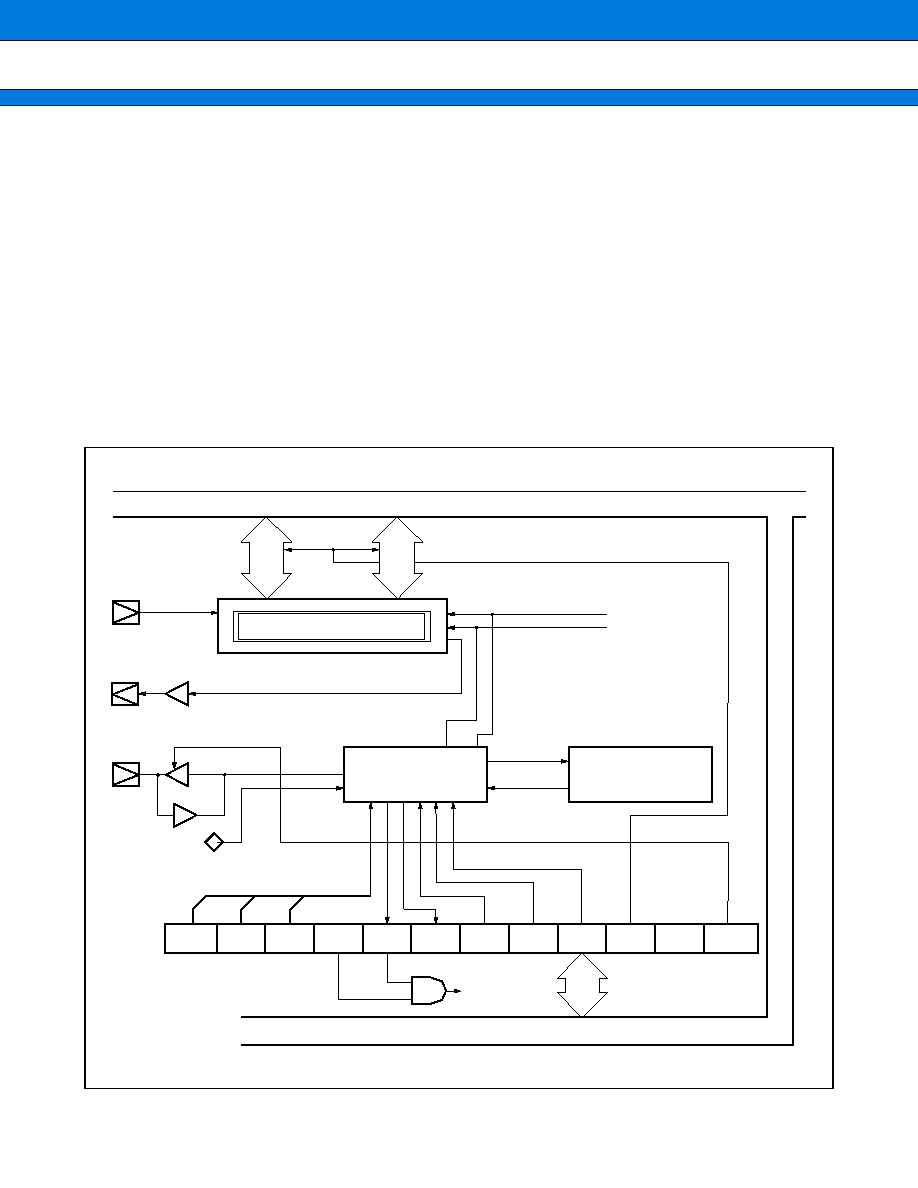

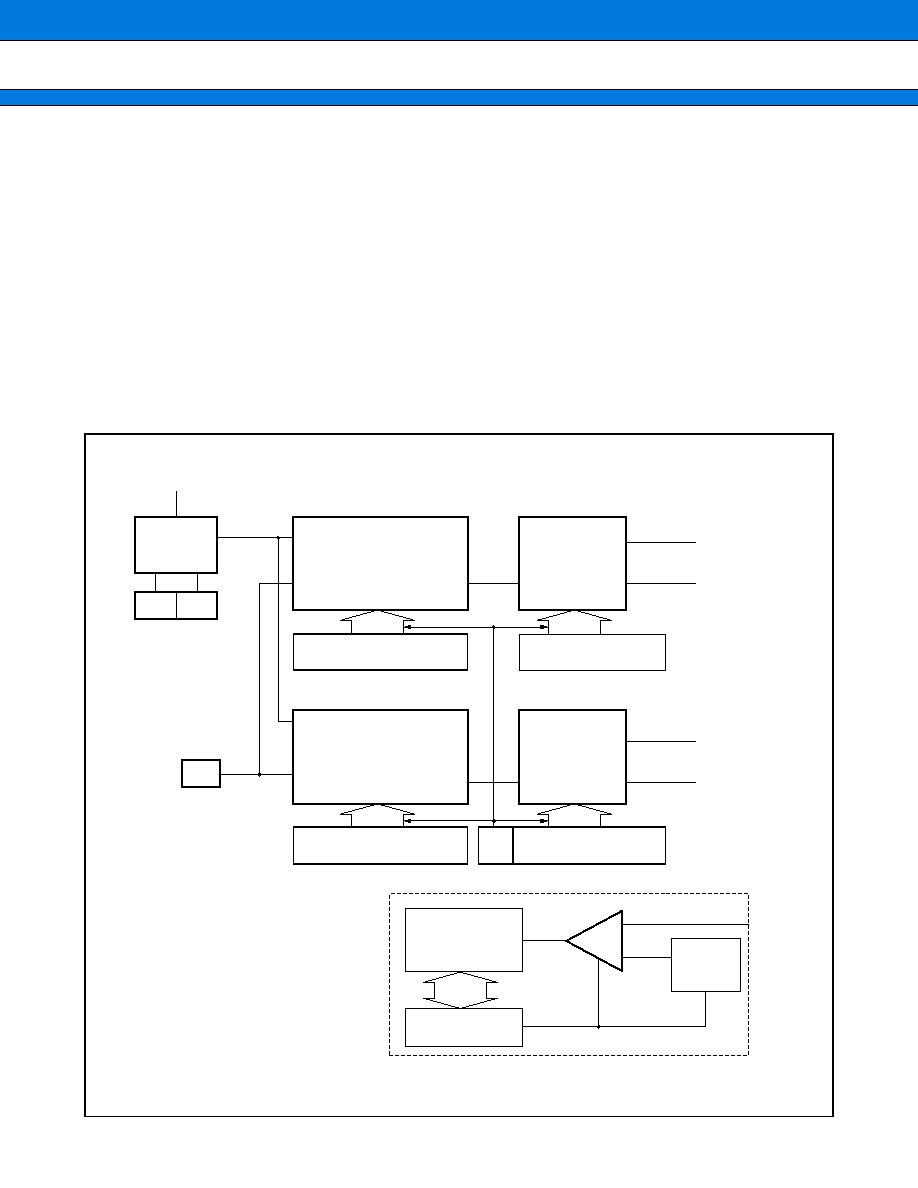

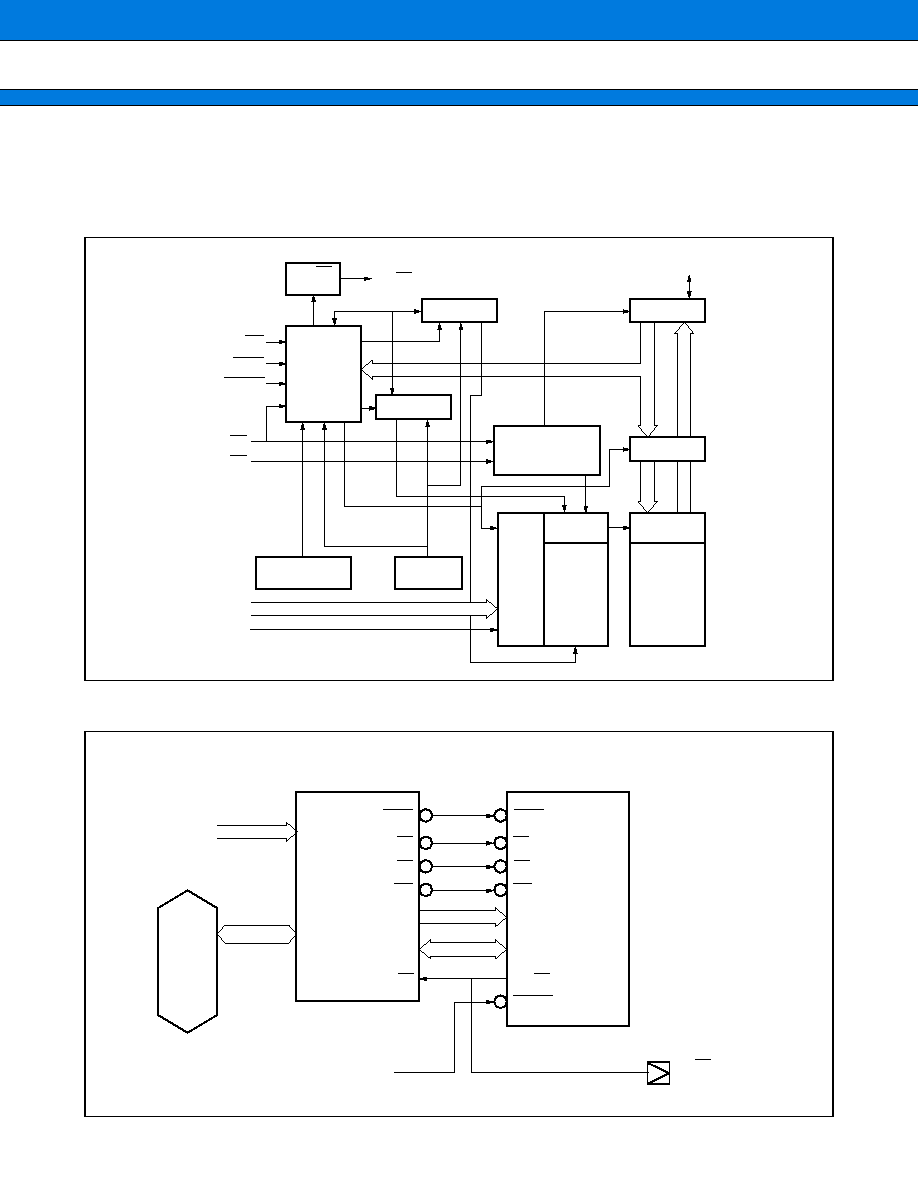

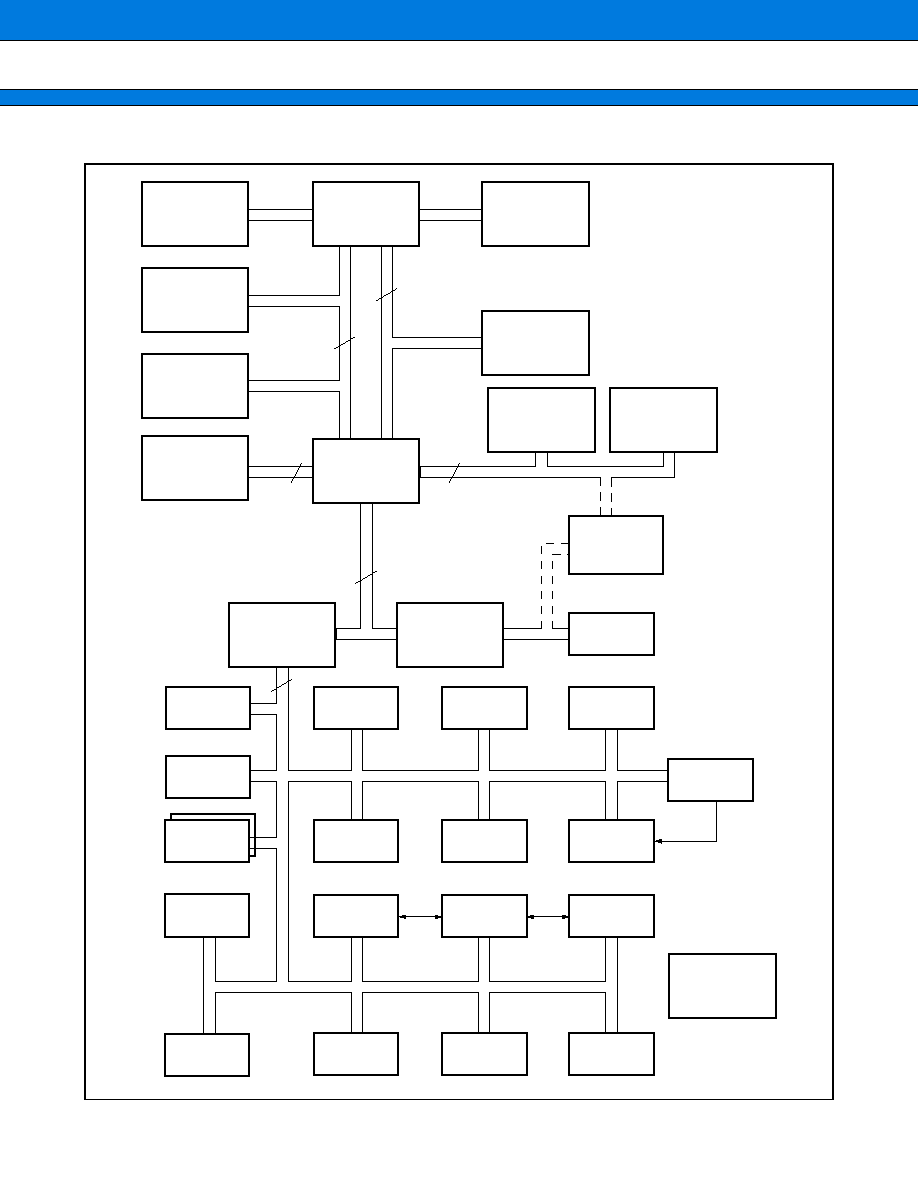

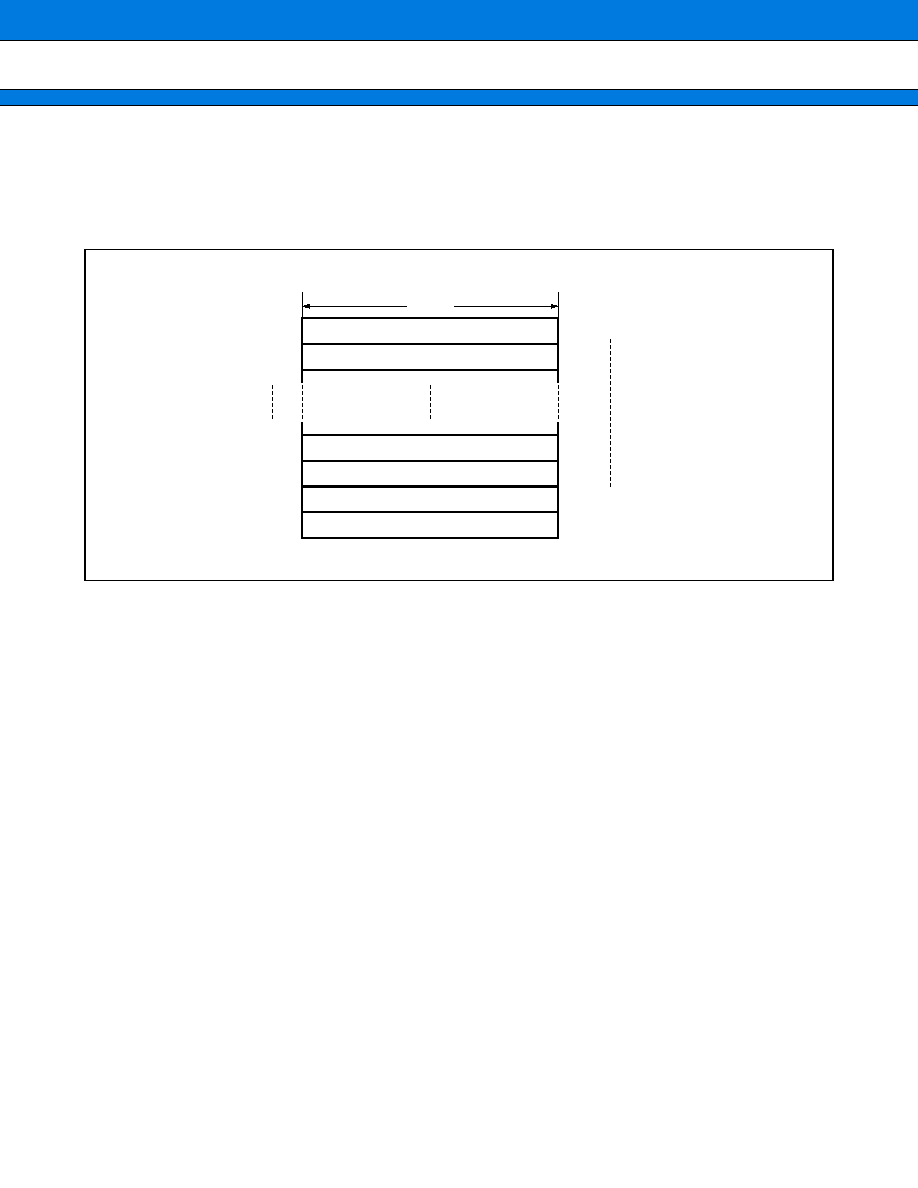

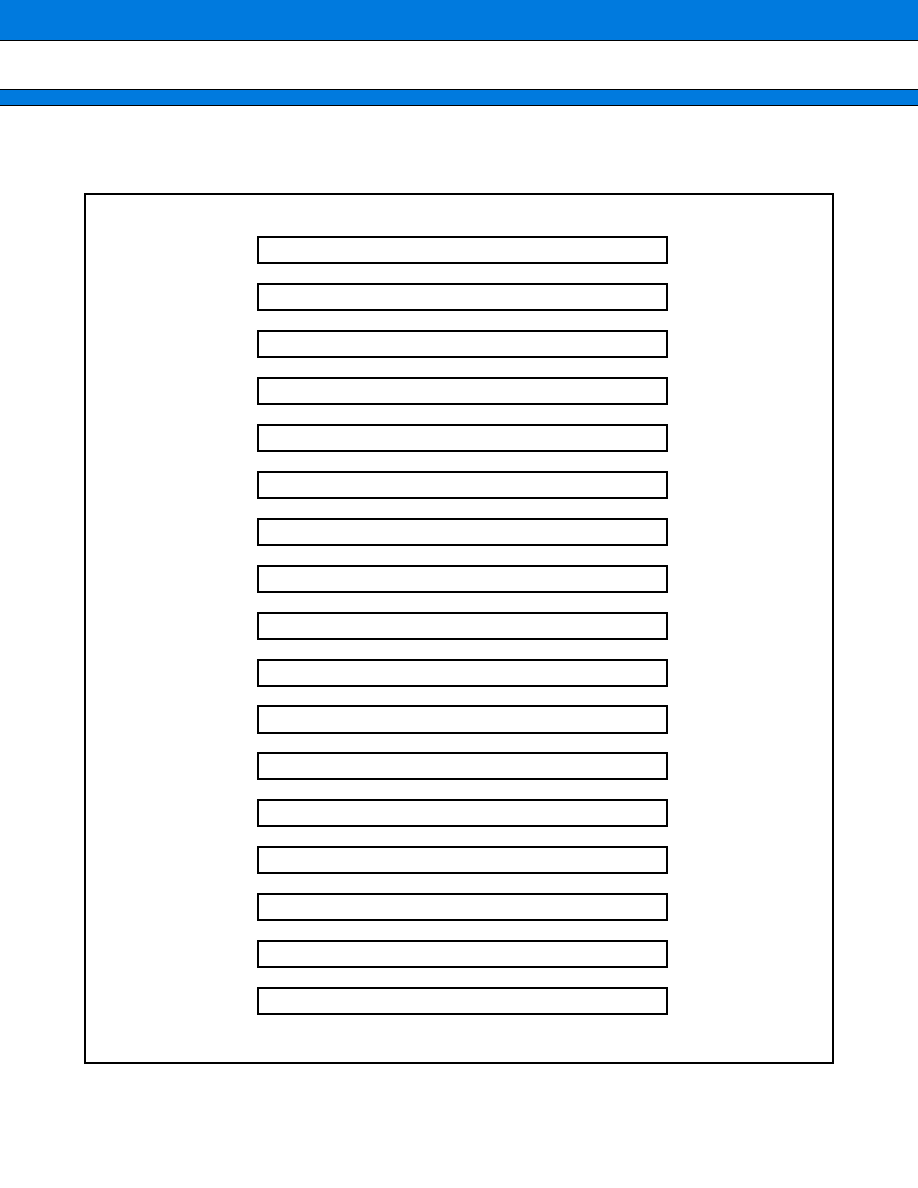

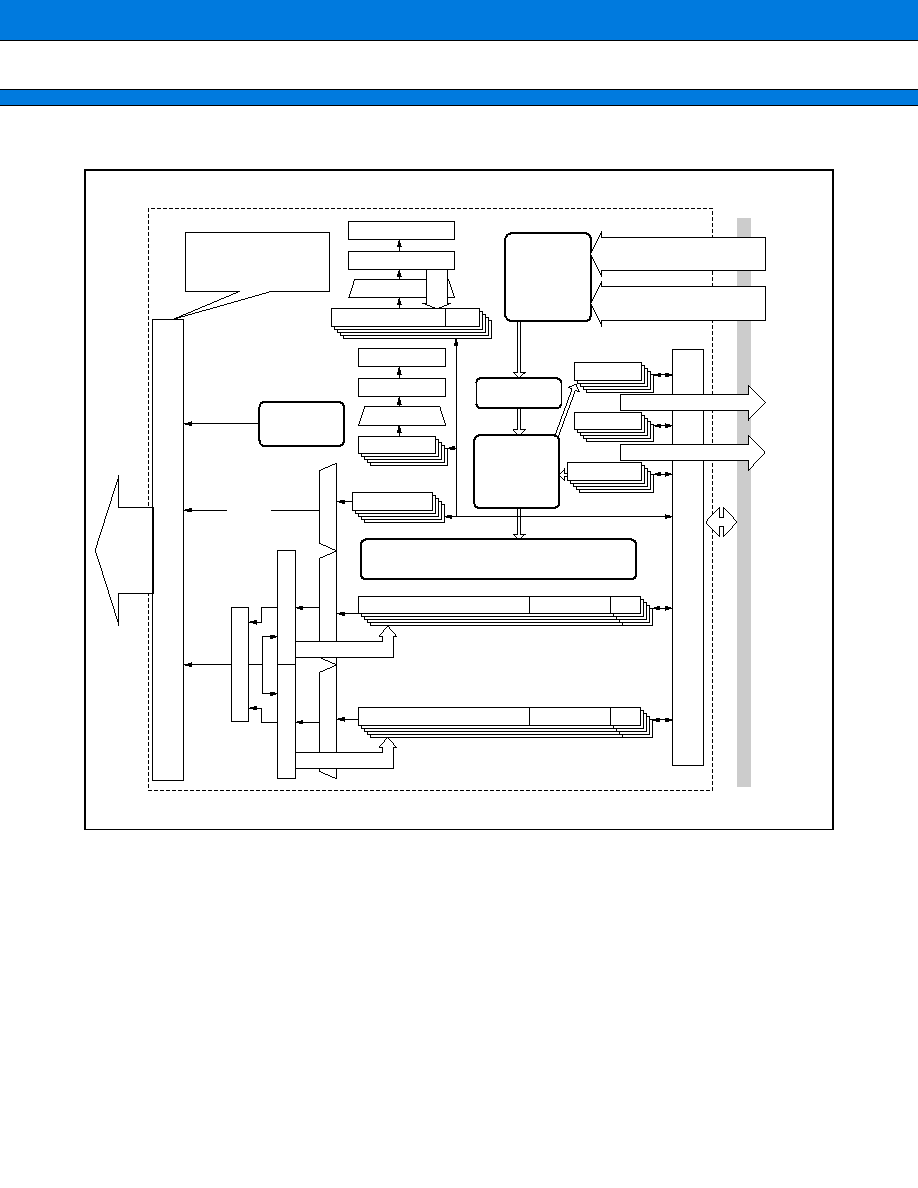

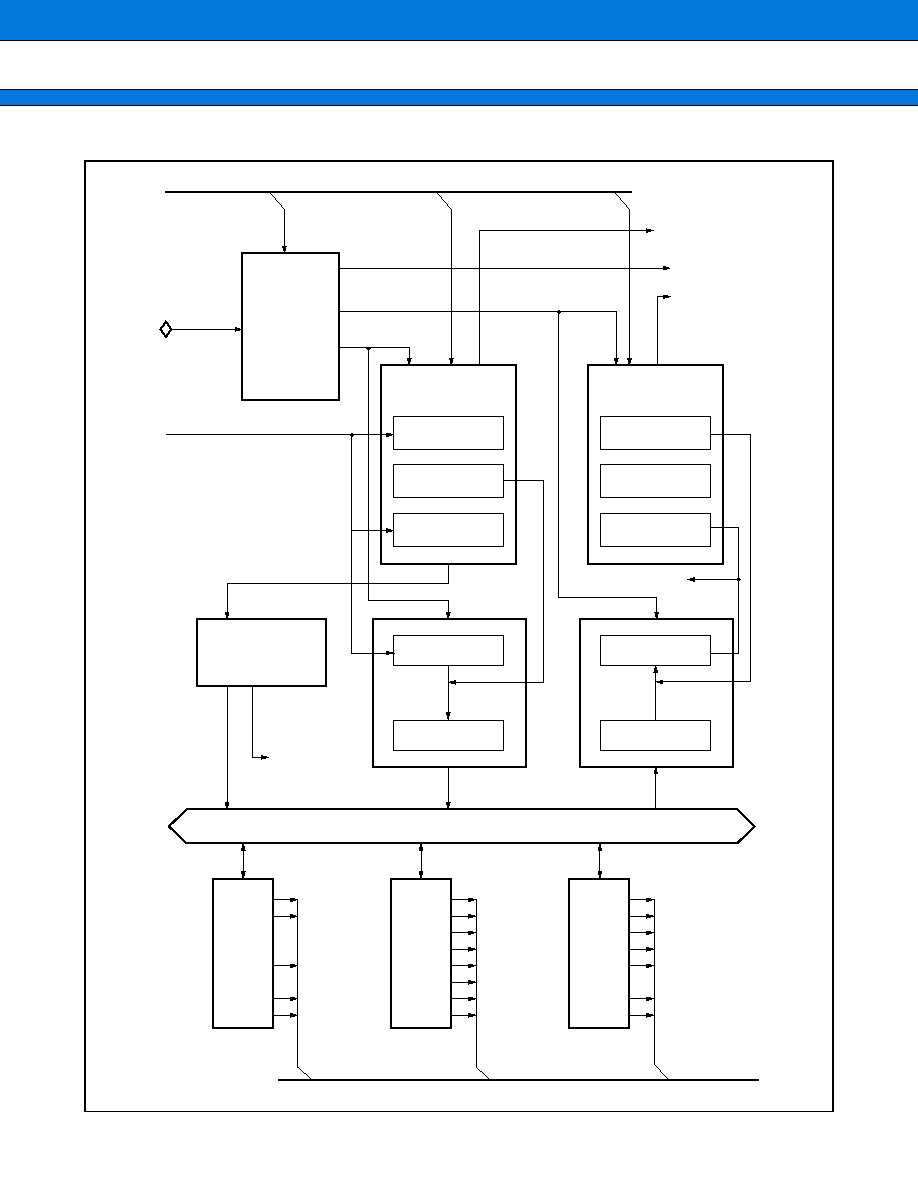

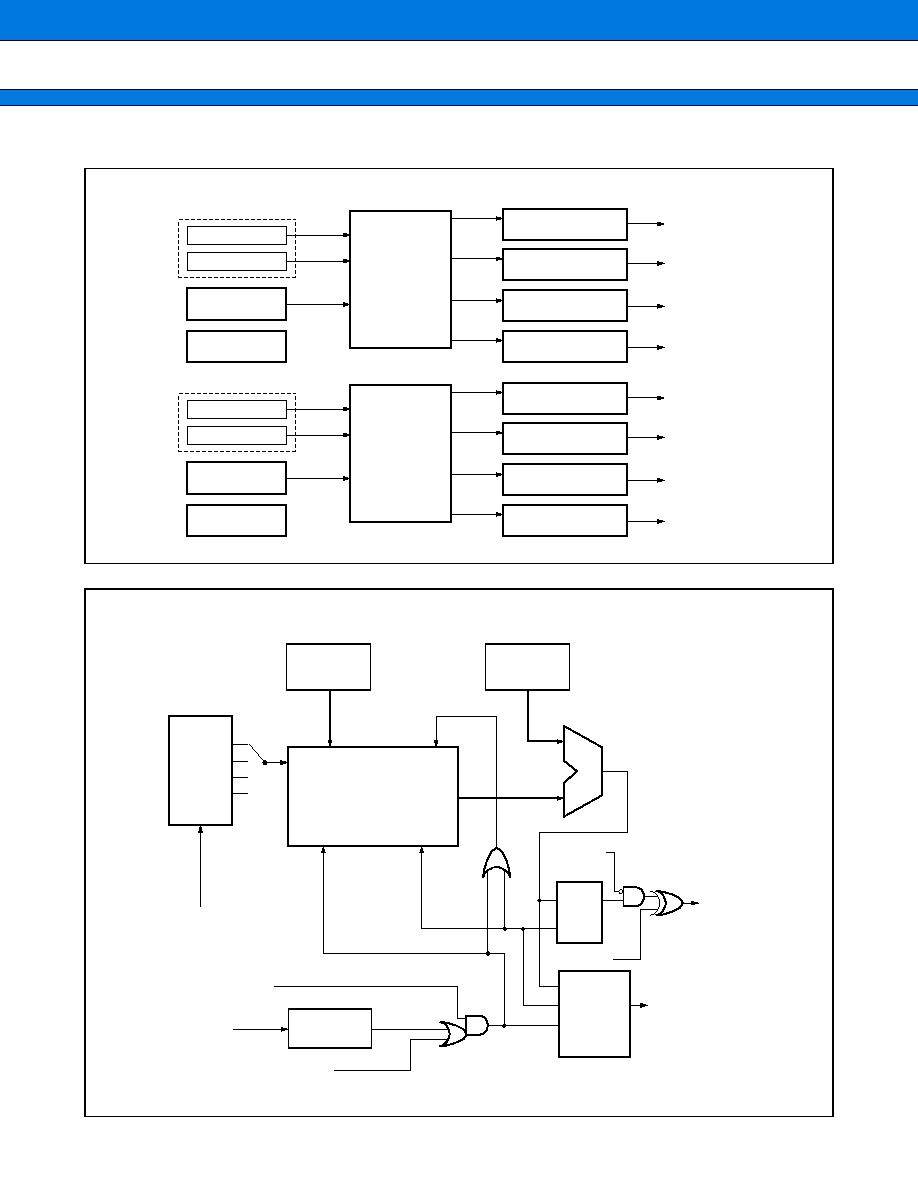

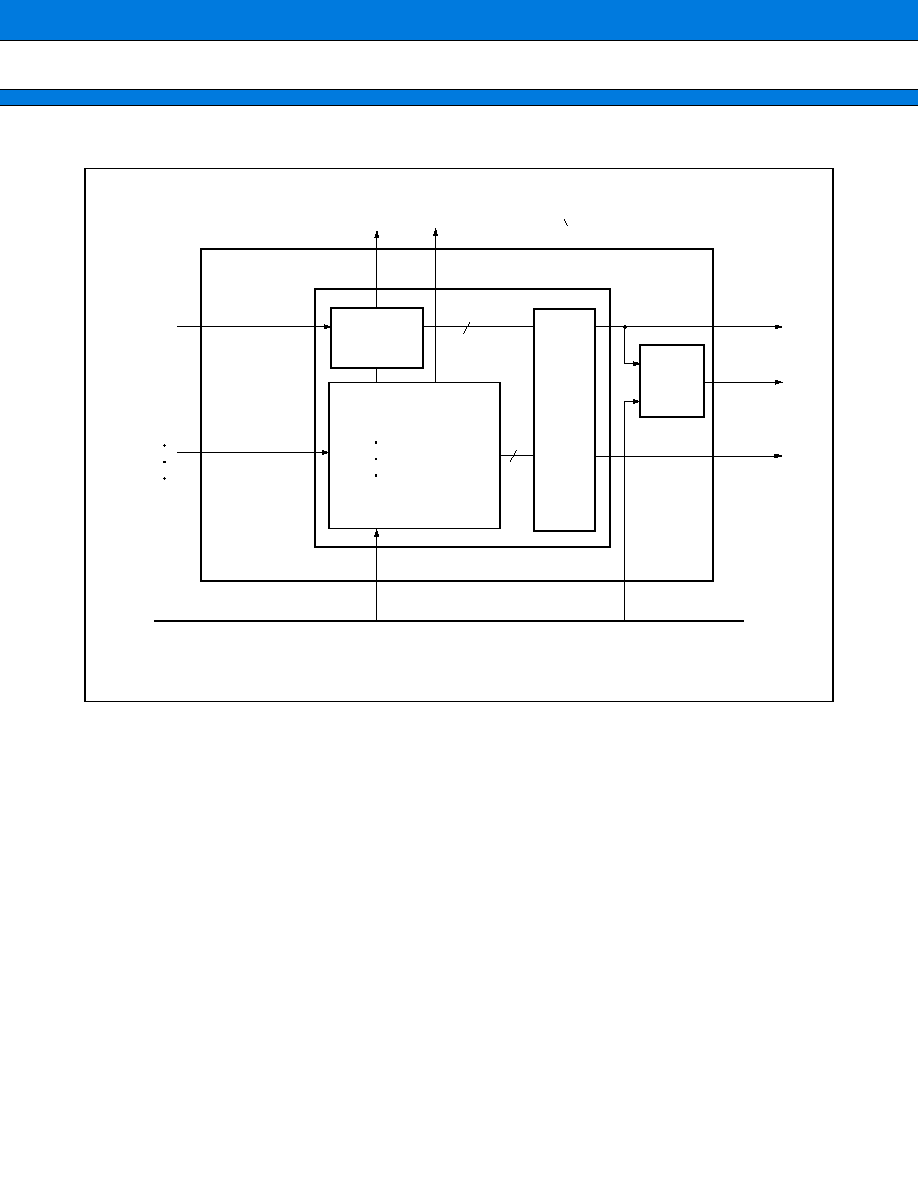

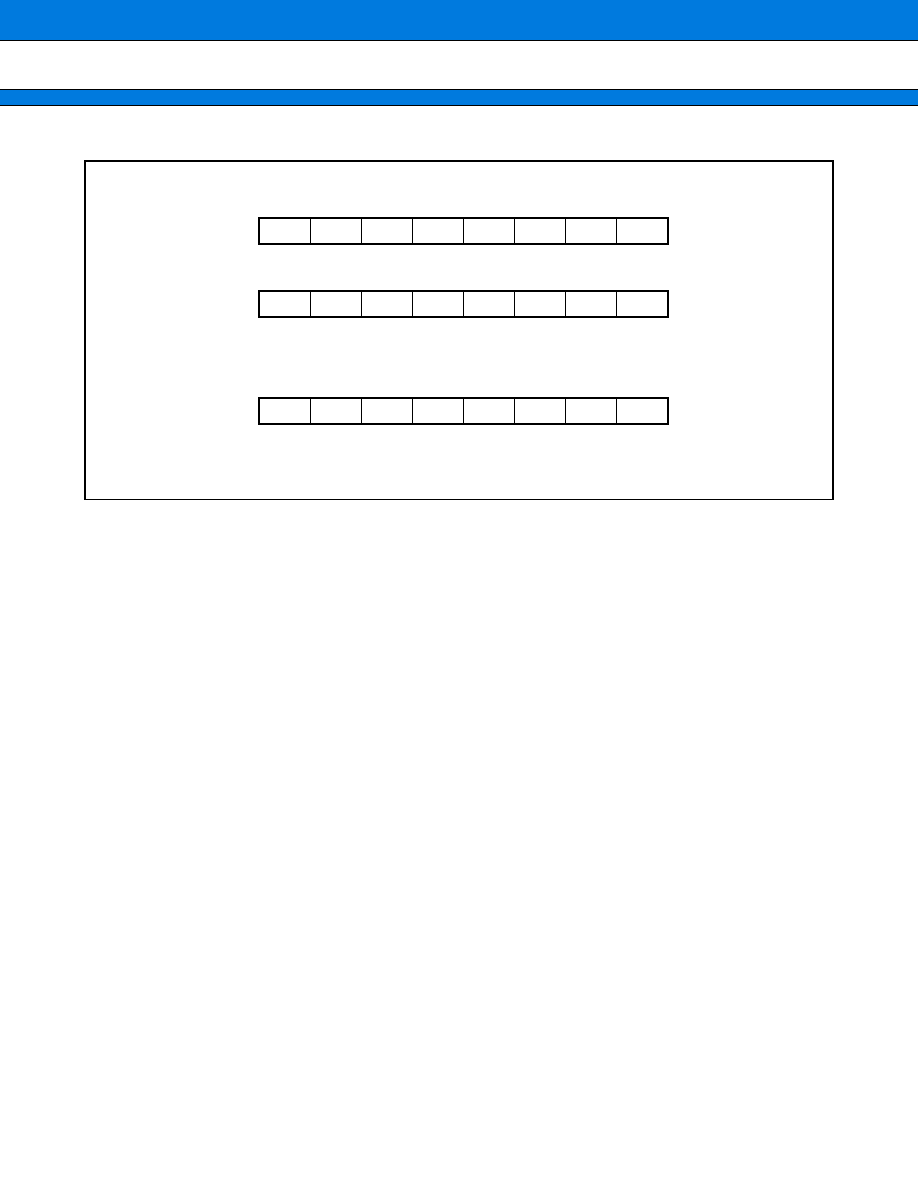

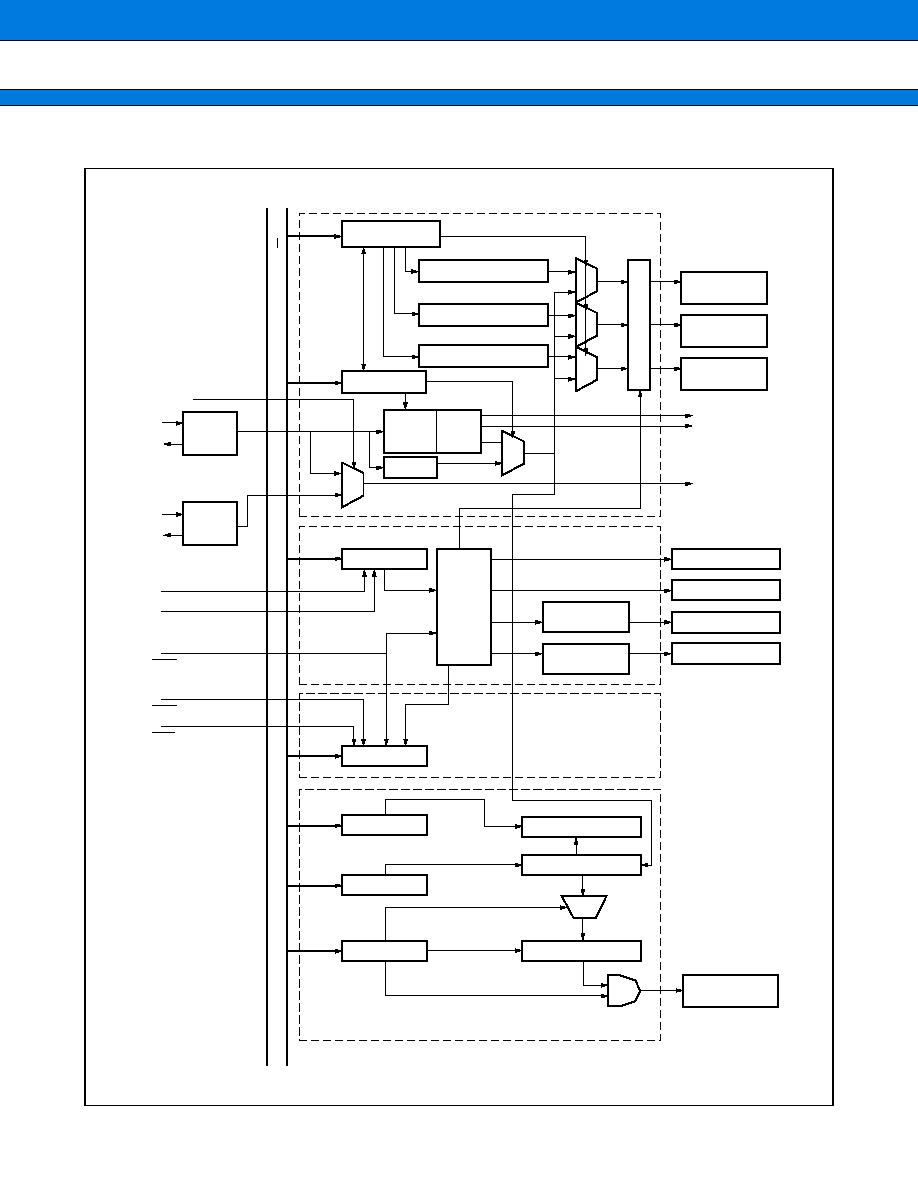

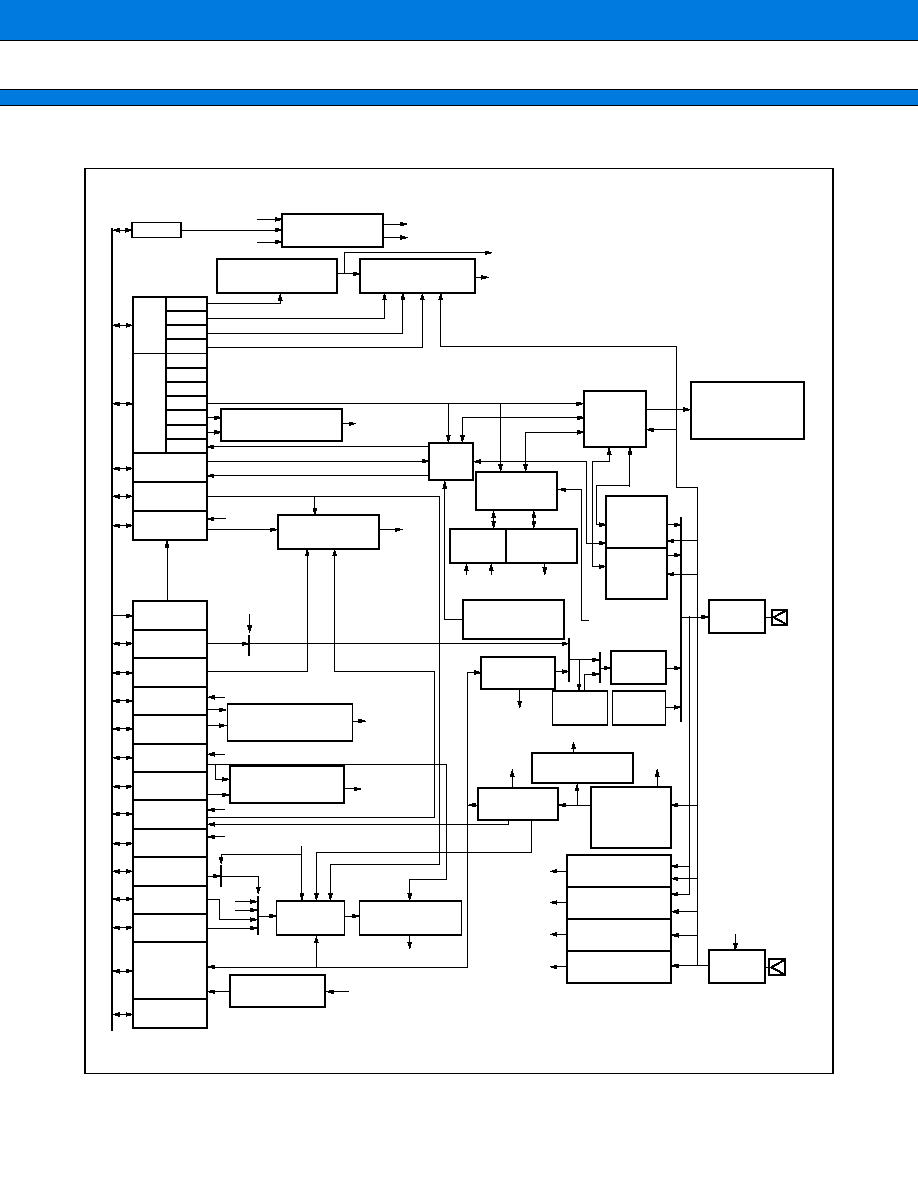

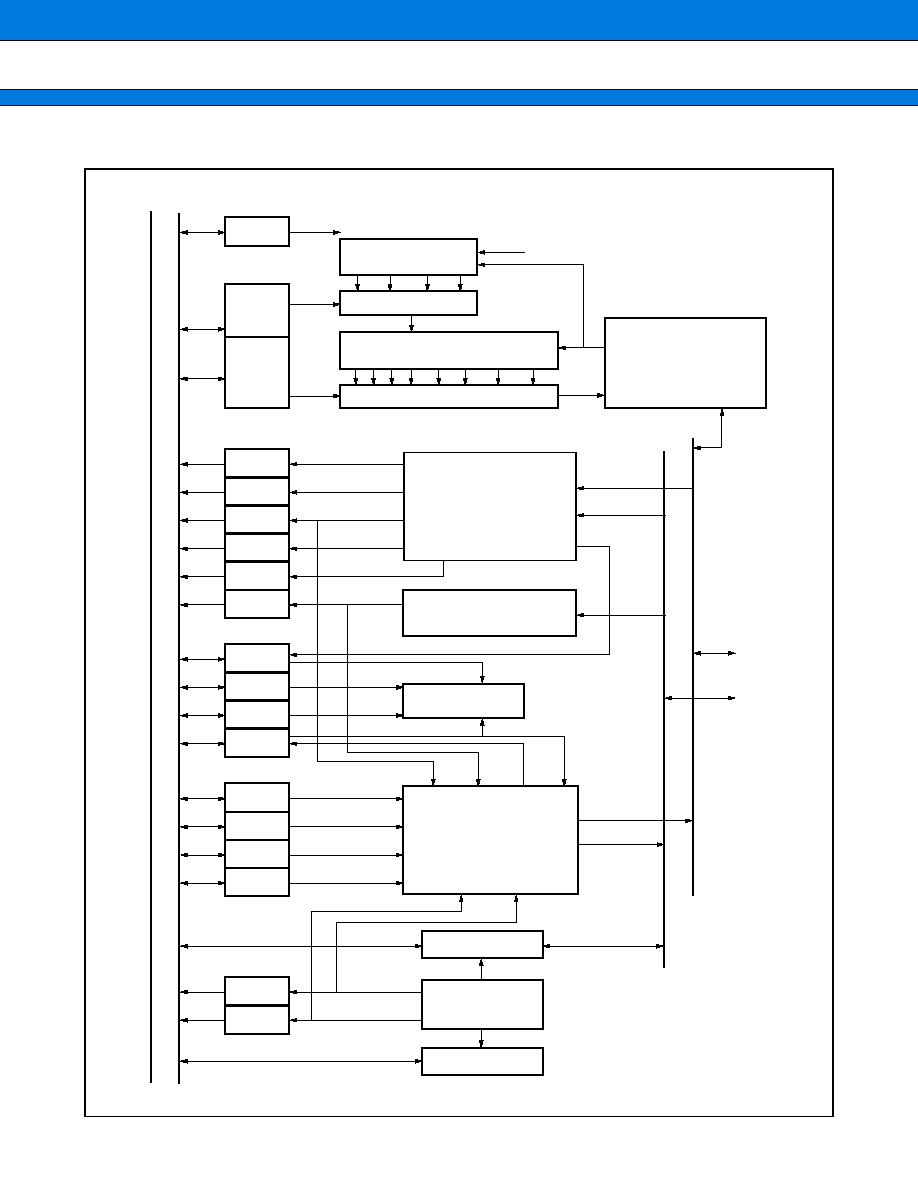

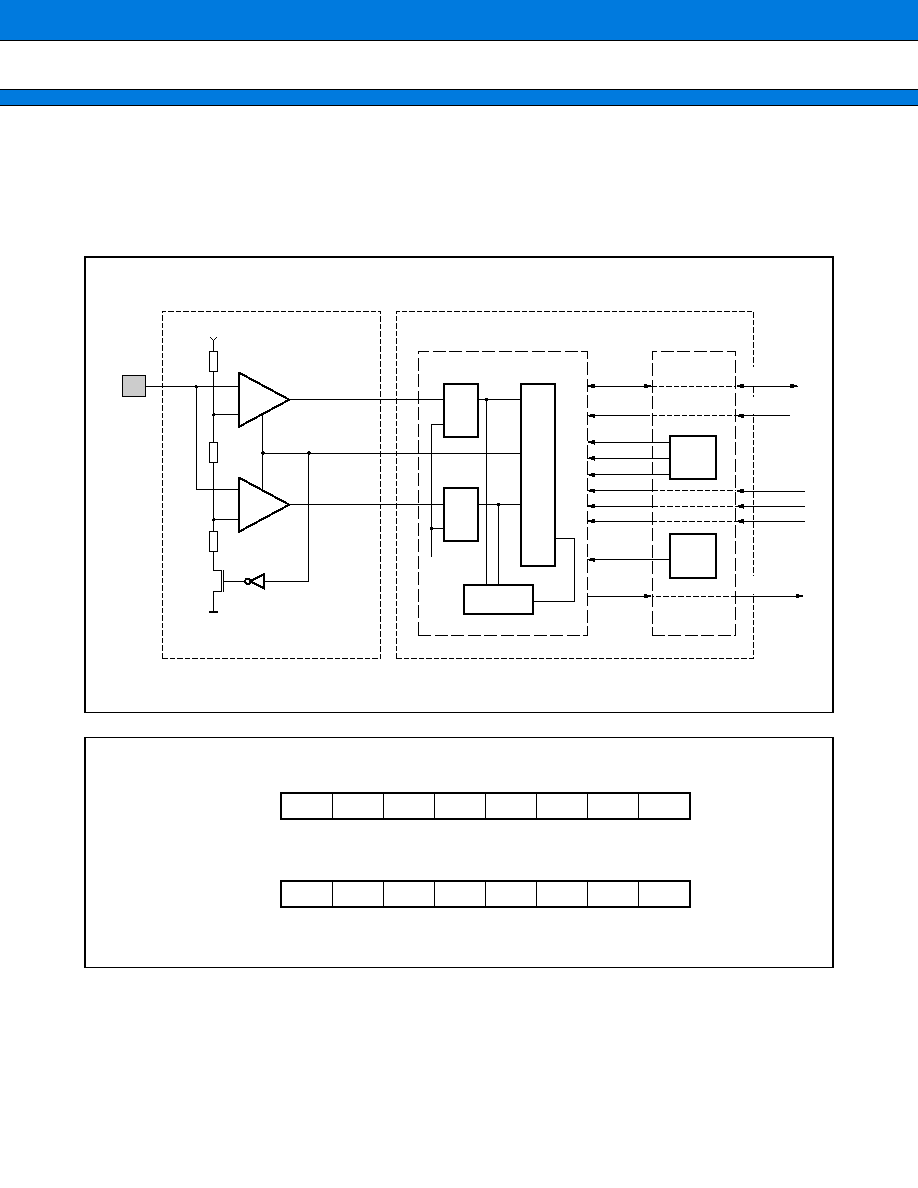

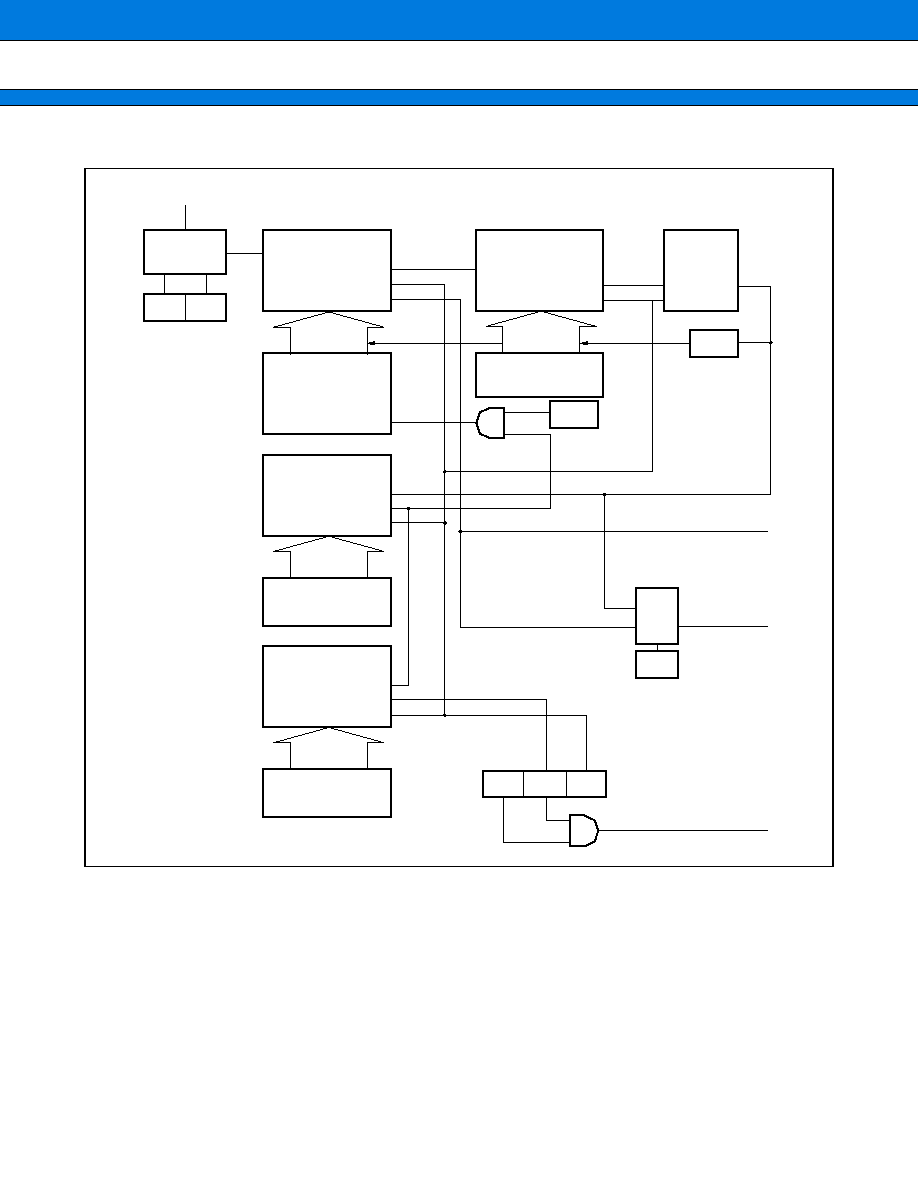

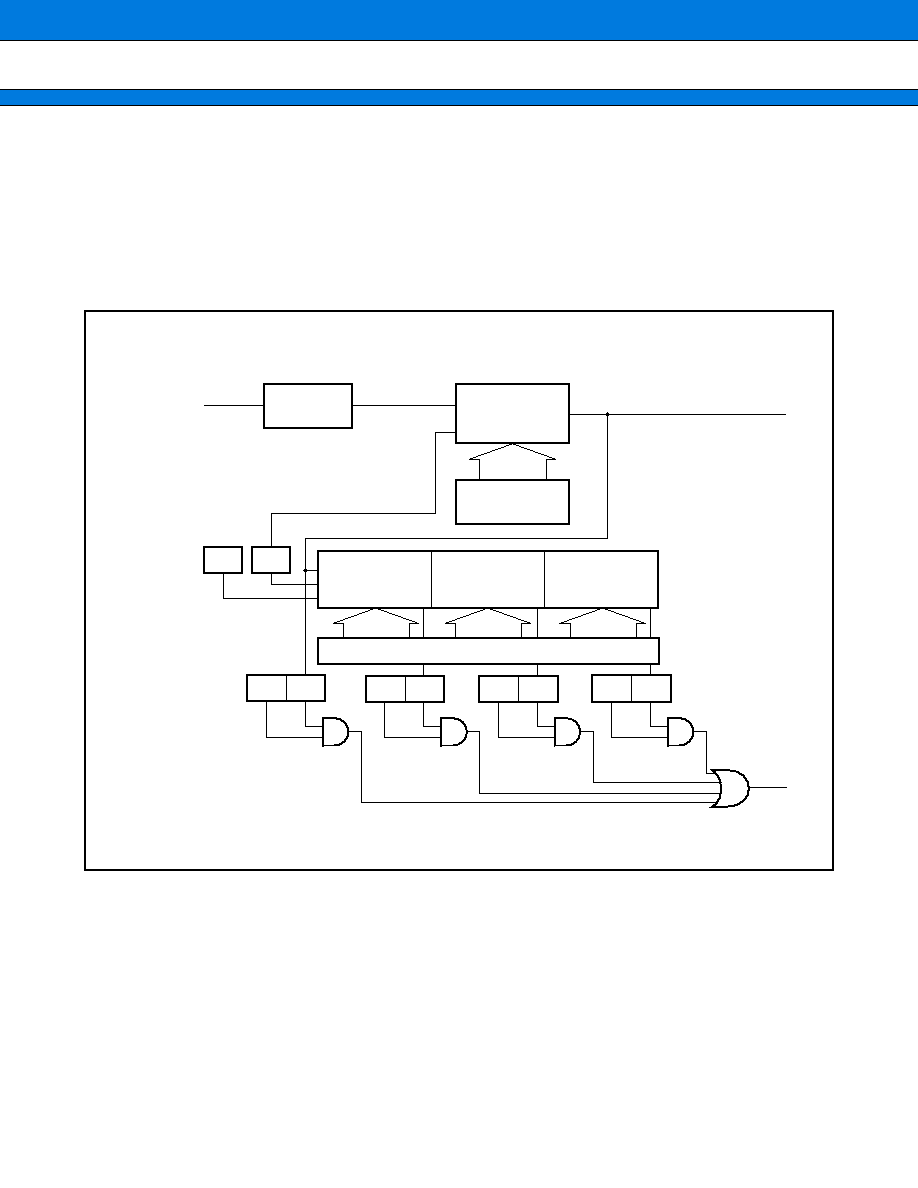

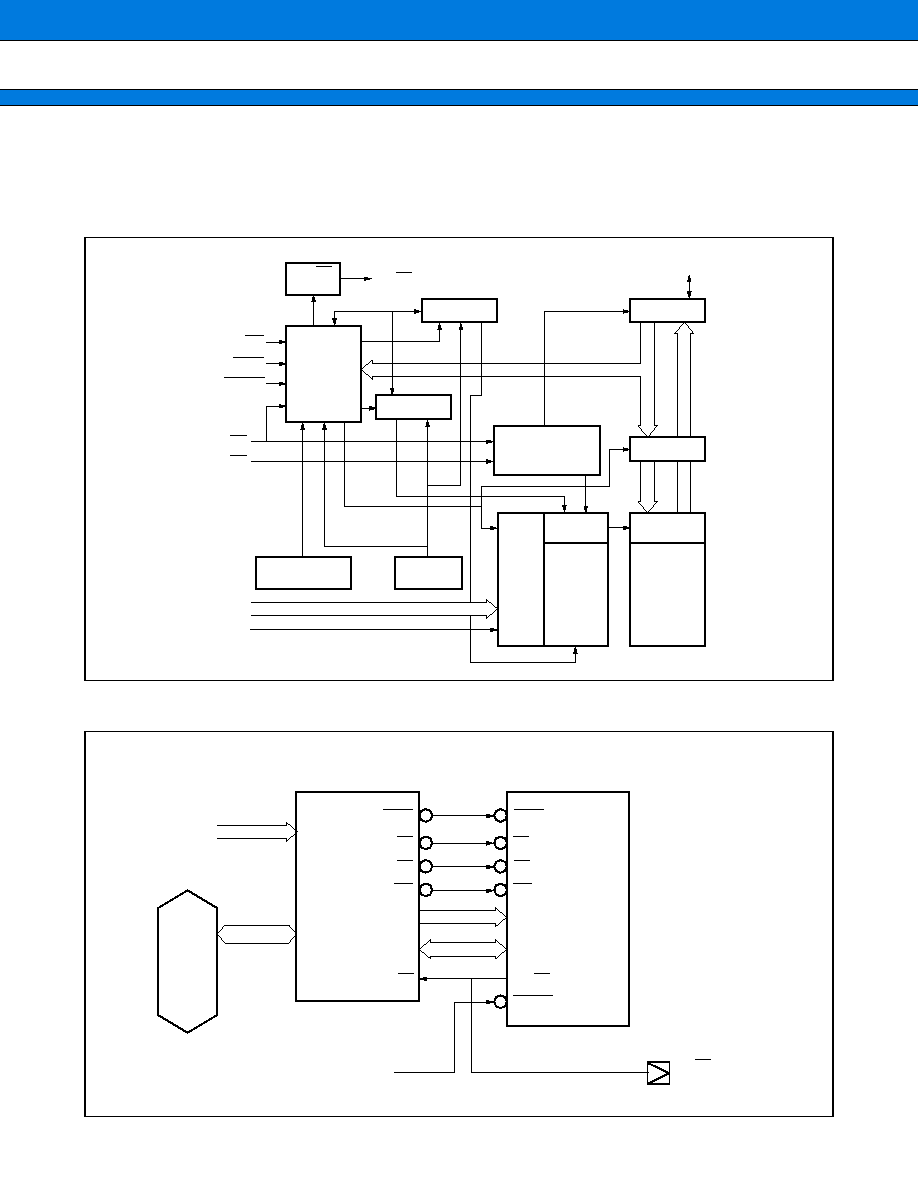

s

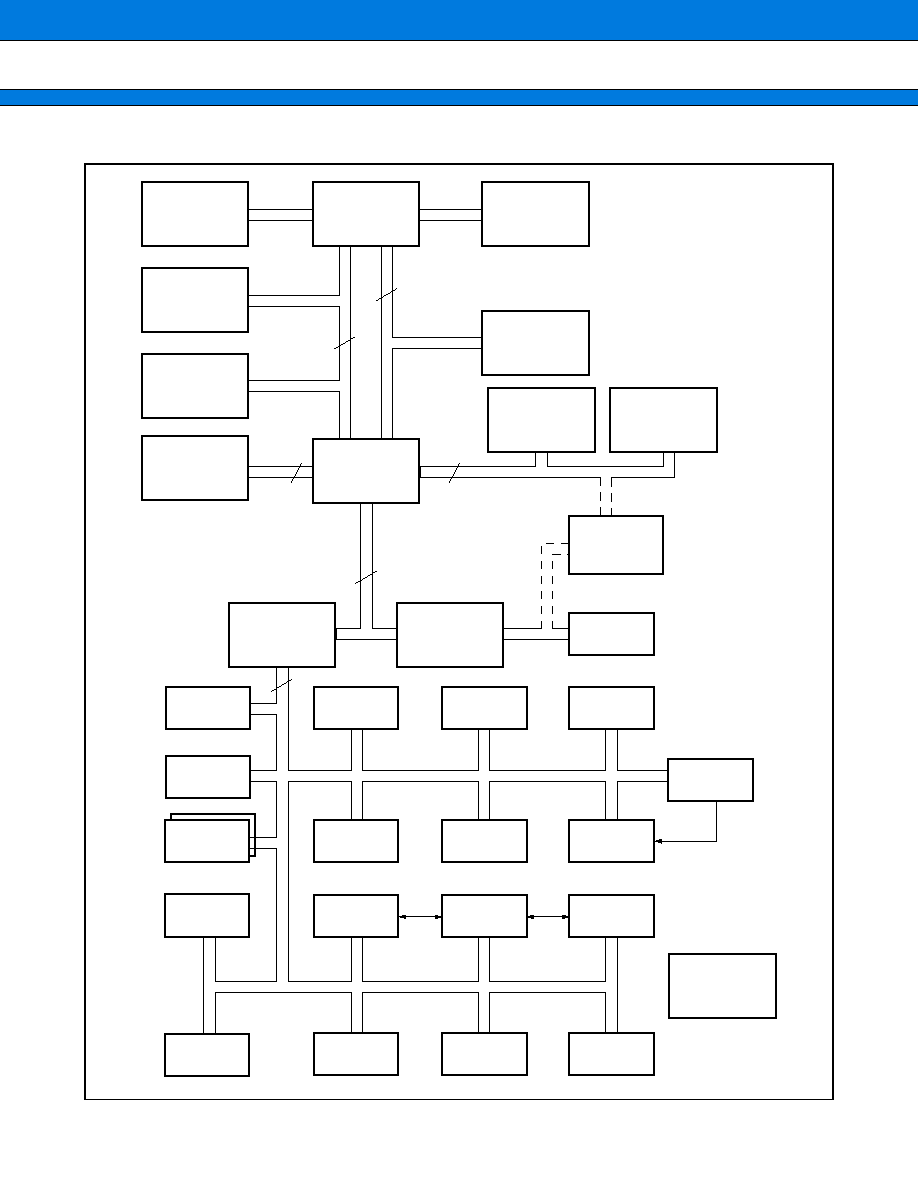

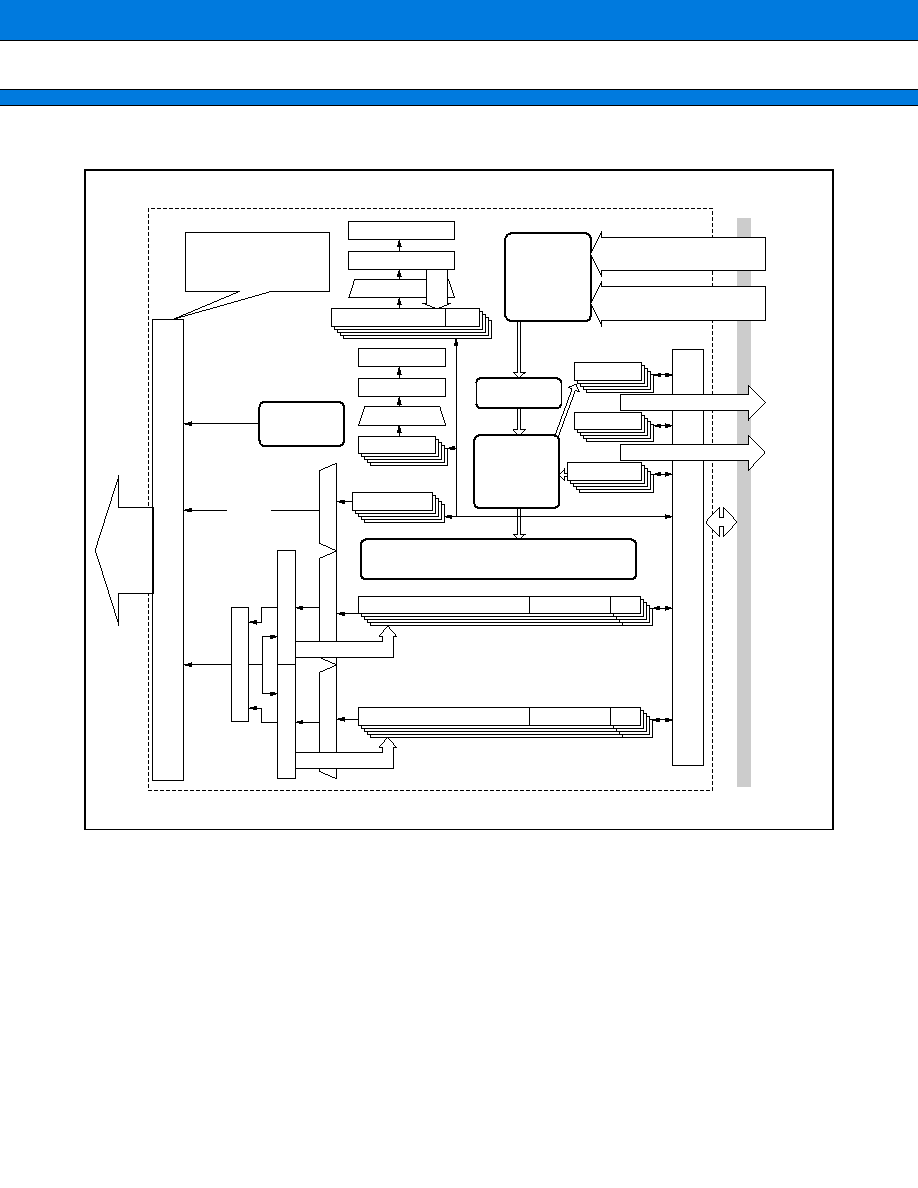

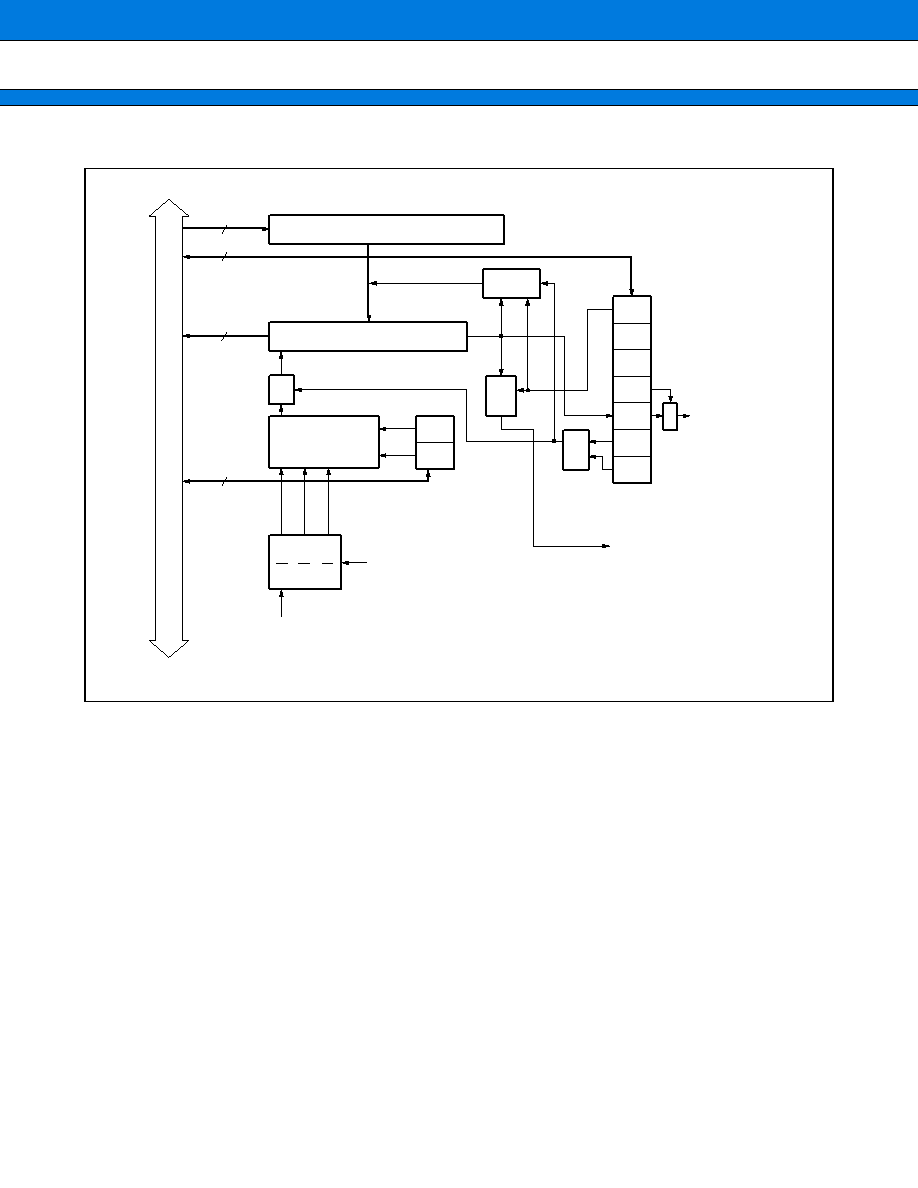

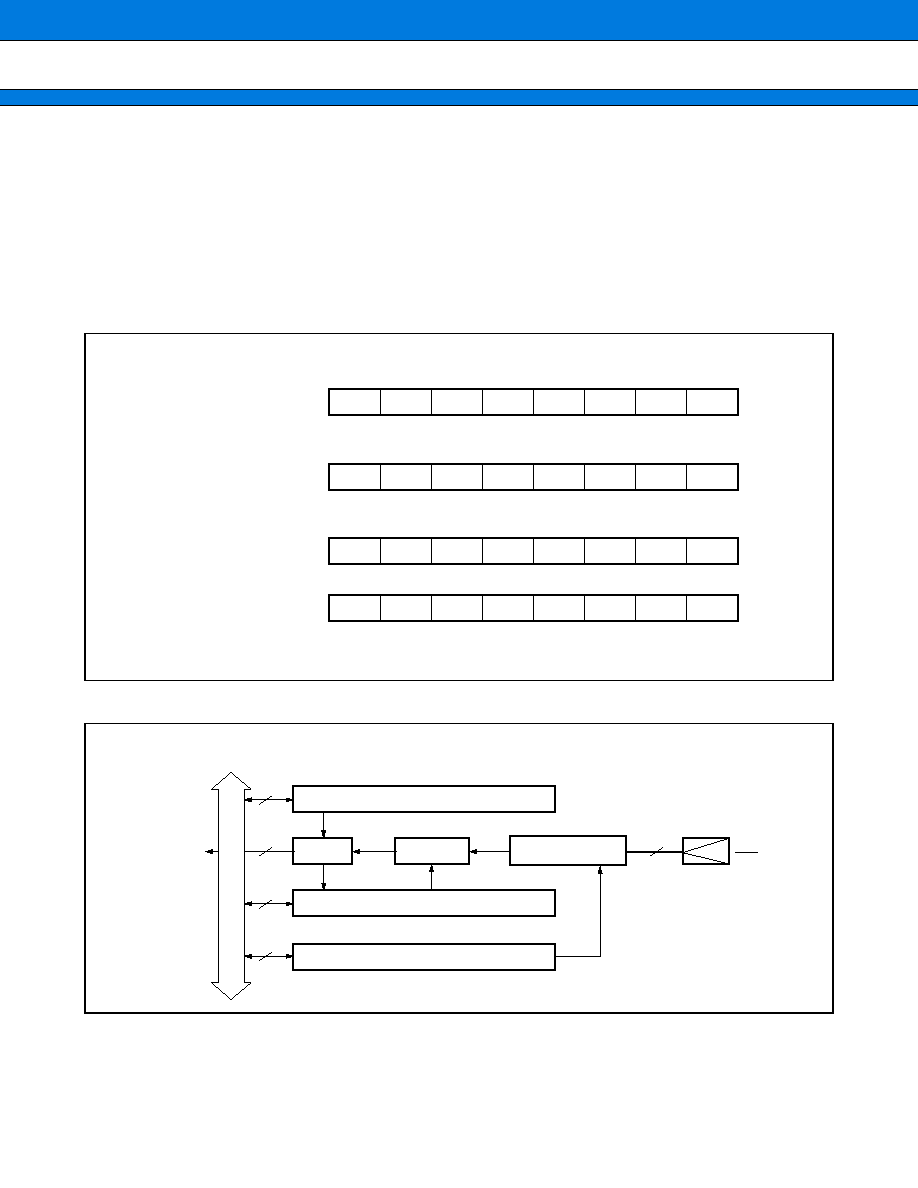

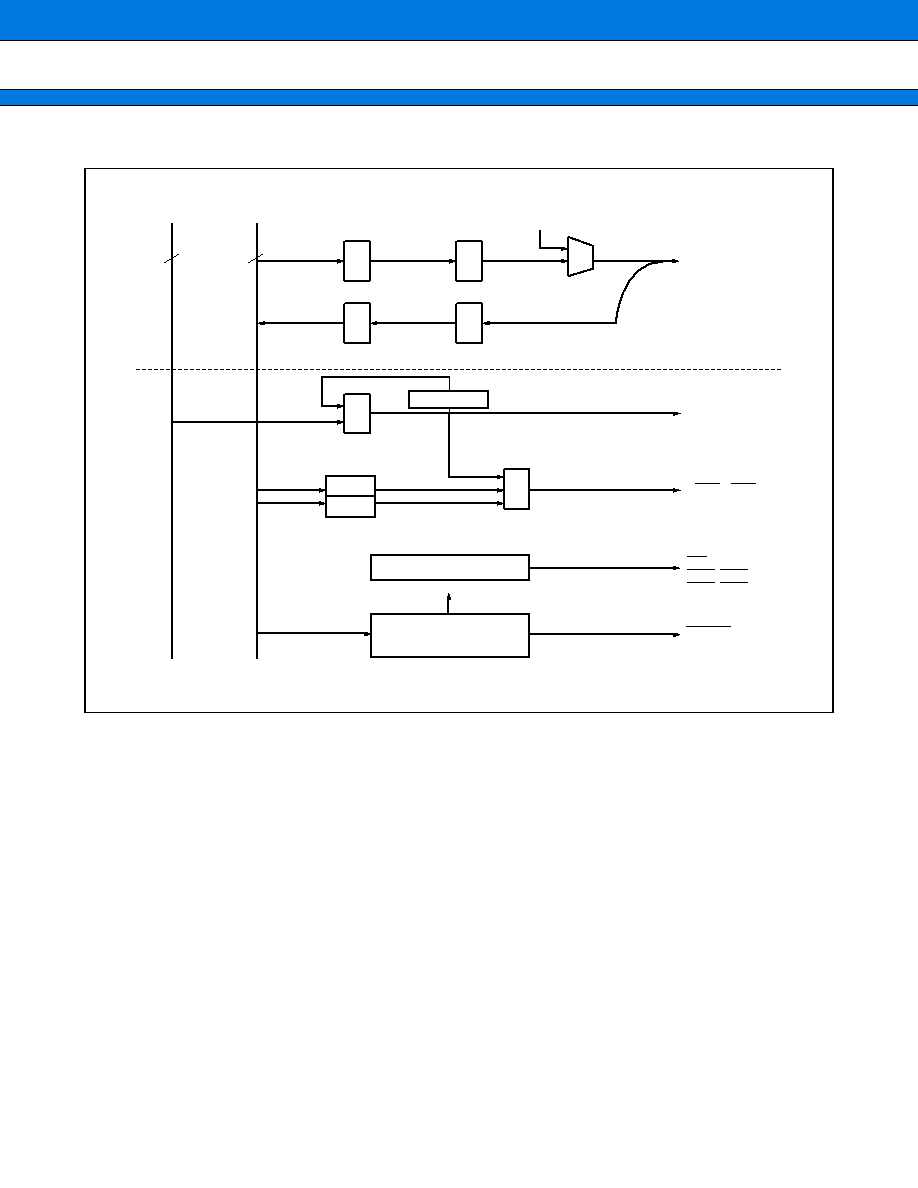

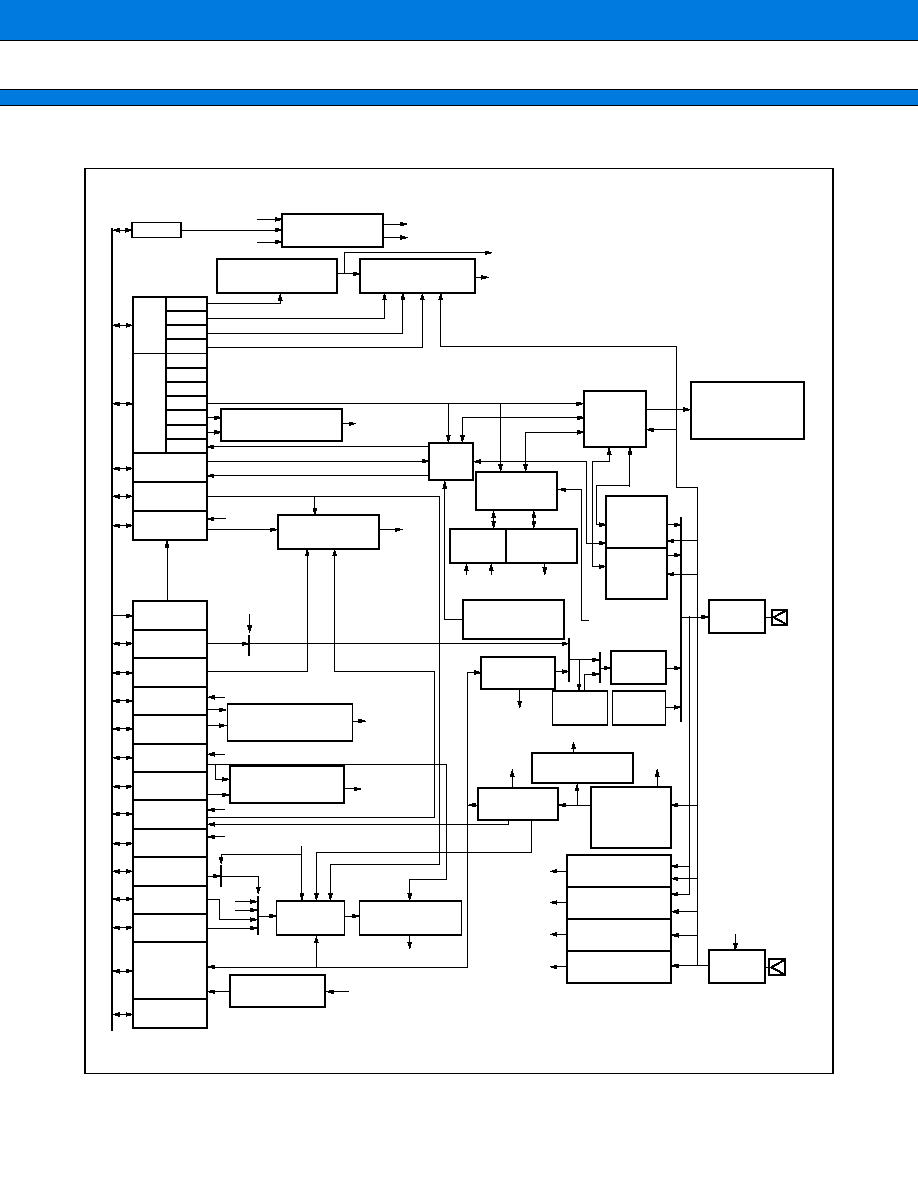

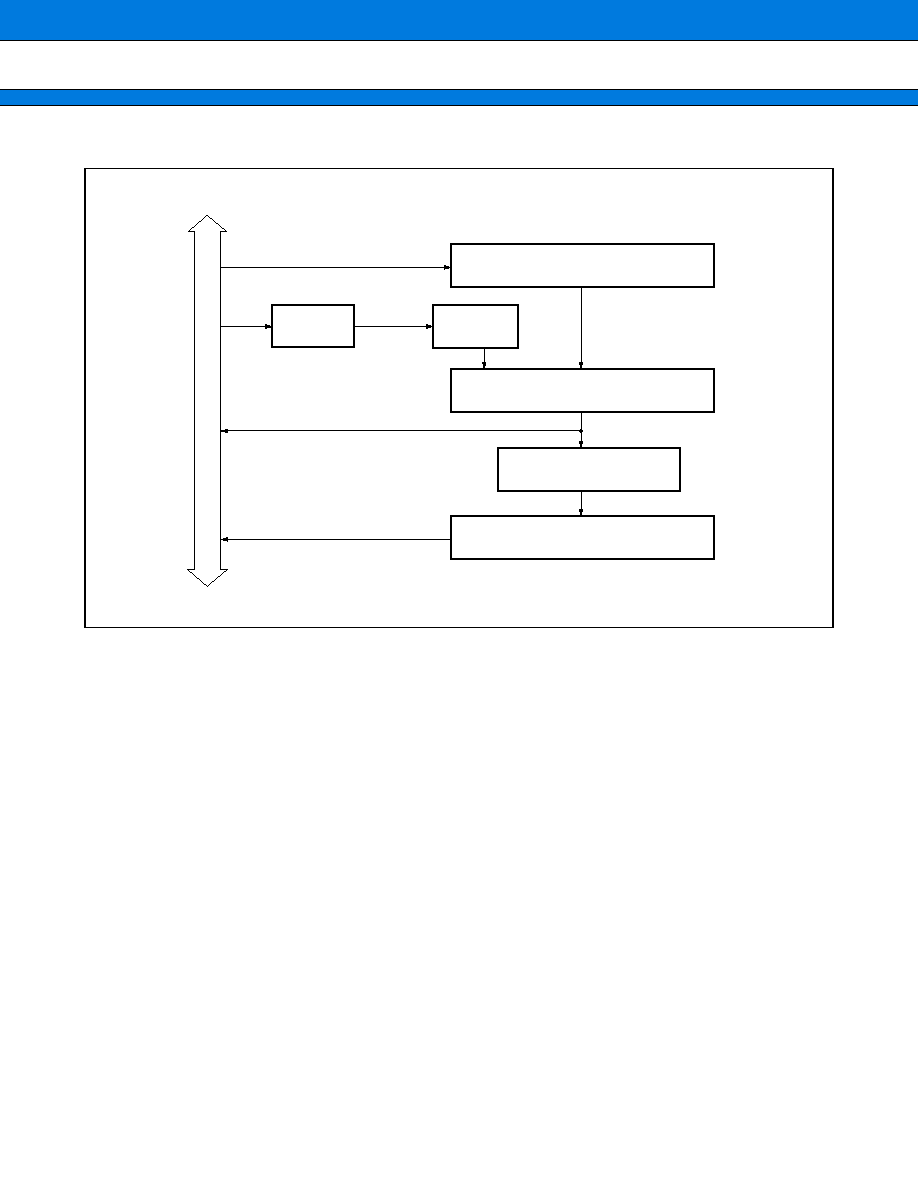

BLOCK DIAGRAM

32

32

32

16

32

32

on FV360GA, F362GA

on F361GA

Clock

Generation

FR50

Core

Watchdog

Timer

User RAM

D-bus

Bit Search

Module

DMA

Controller

Instruction

Cache/RAM

F-bus RAM

Bus

Converter

Boot ROM

2 KB

R-Bus

Adapter

SIO Prescaler/

SIO

U-Timer/

UART

Power Down

Reset

Subclock

Calibration

External Bus

Interface

CAN

DAC

ADC

External

Interrupt

Flash-

memory

I

2

C

Reload

Timer

ICU

LED

Sound

Generator

Alarm

Comparator

FreeRunning

Timer

Real Time

Clock

Voltage

regulator

OCU

Stepper Motor

Control

Prog. Pulse

Generator

MB91360G Series

28

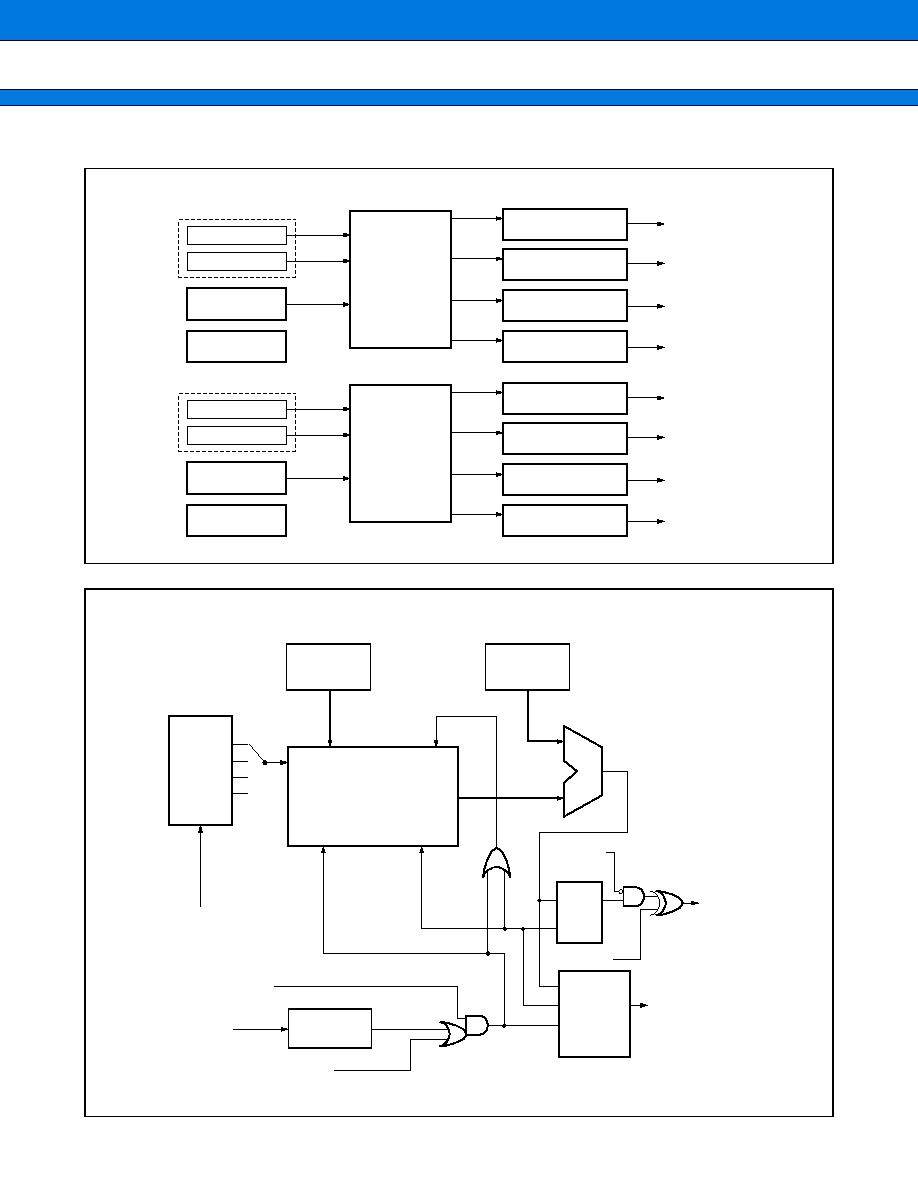

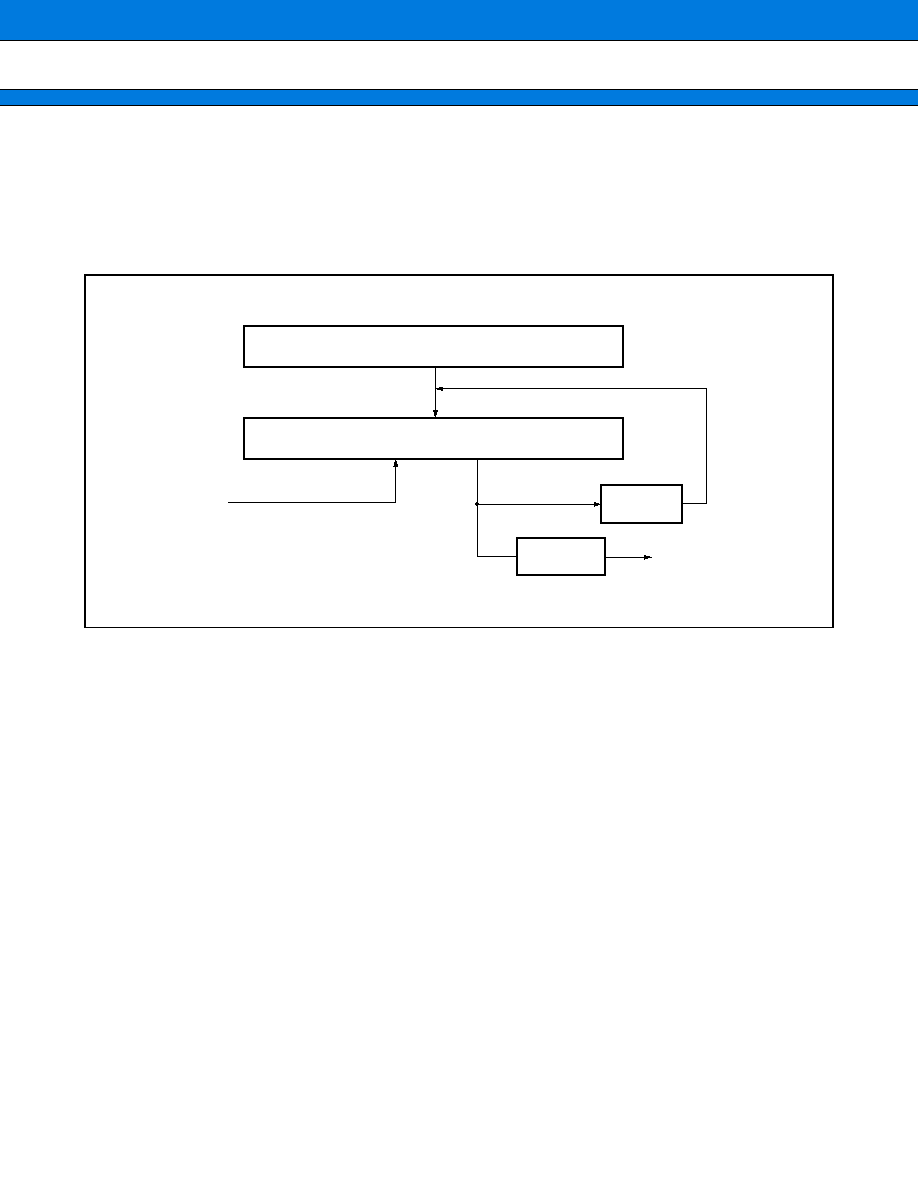

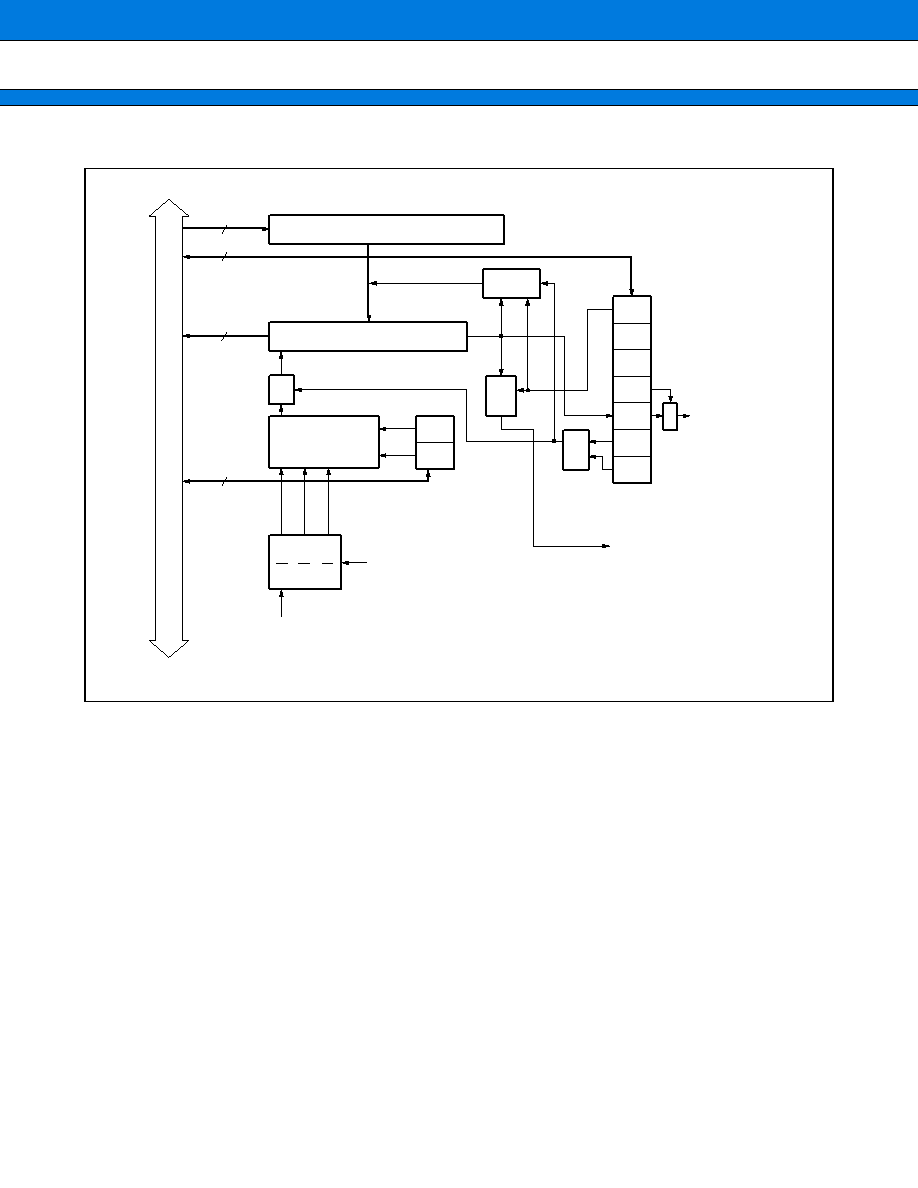

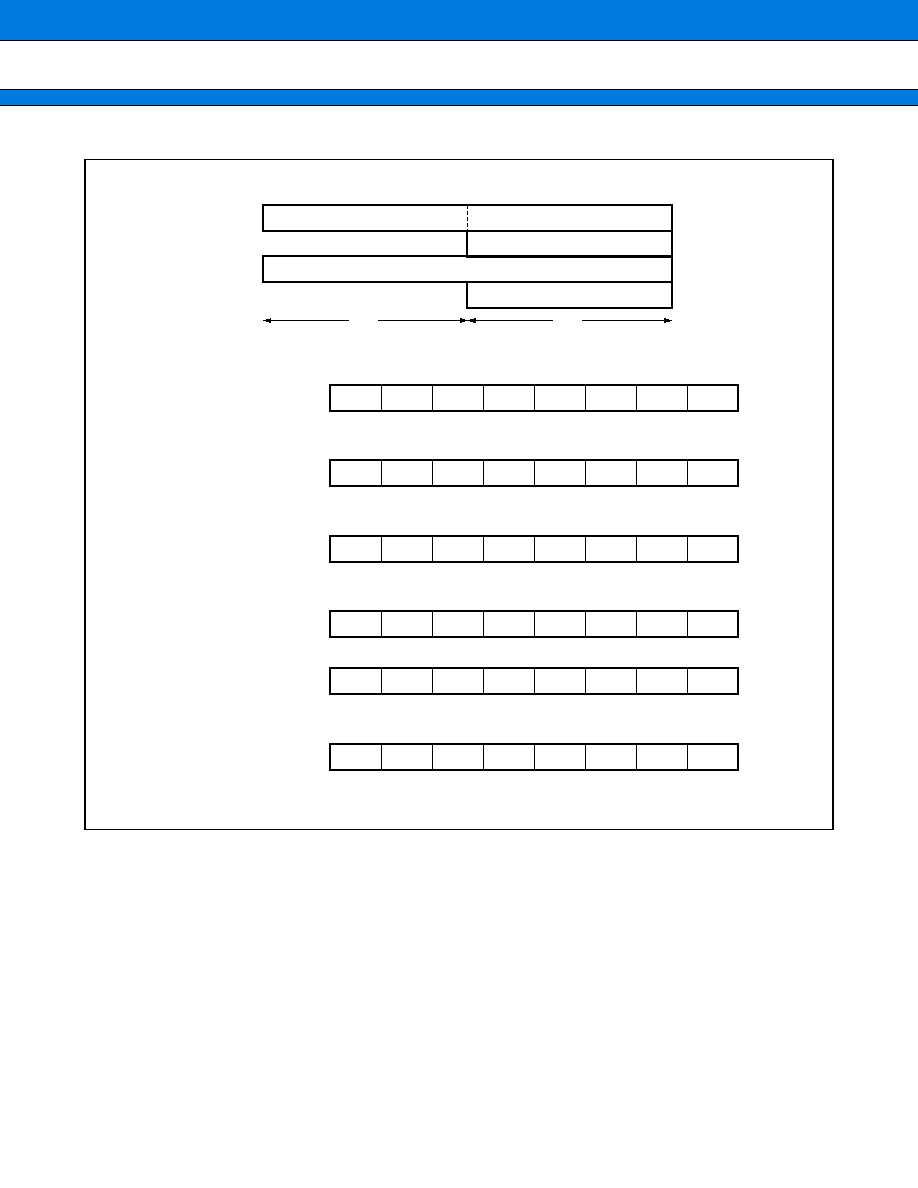

s

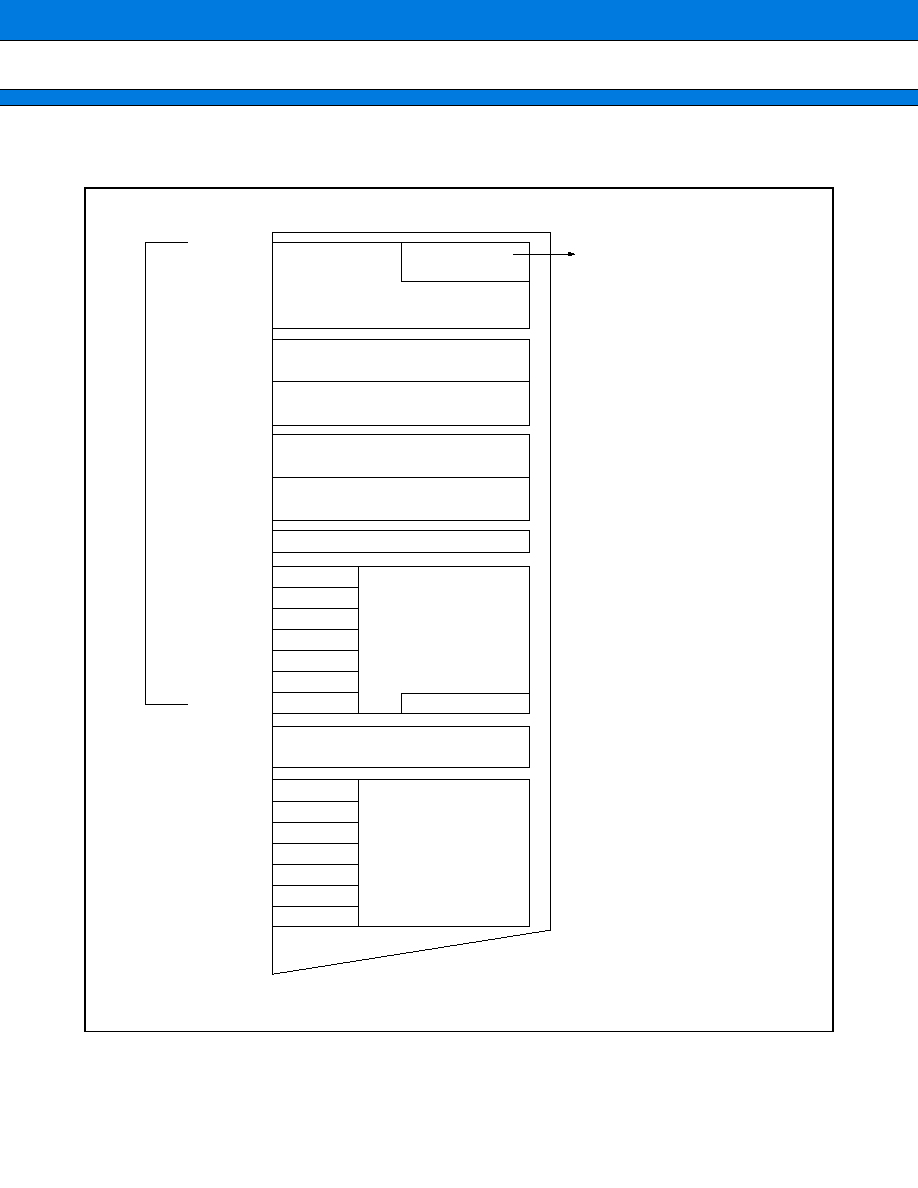

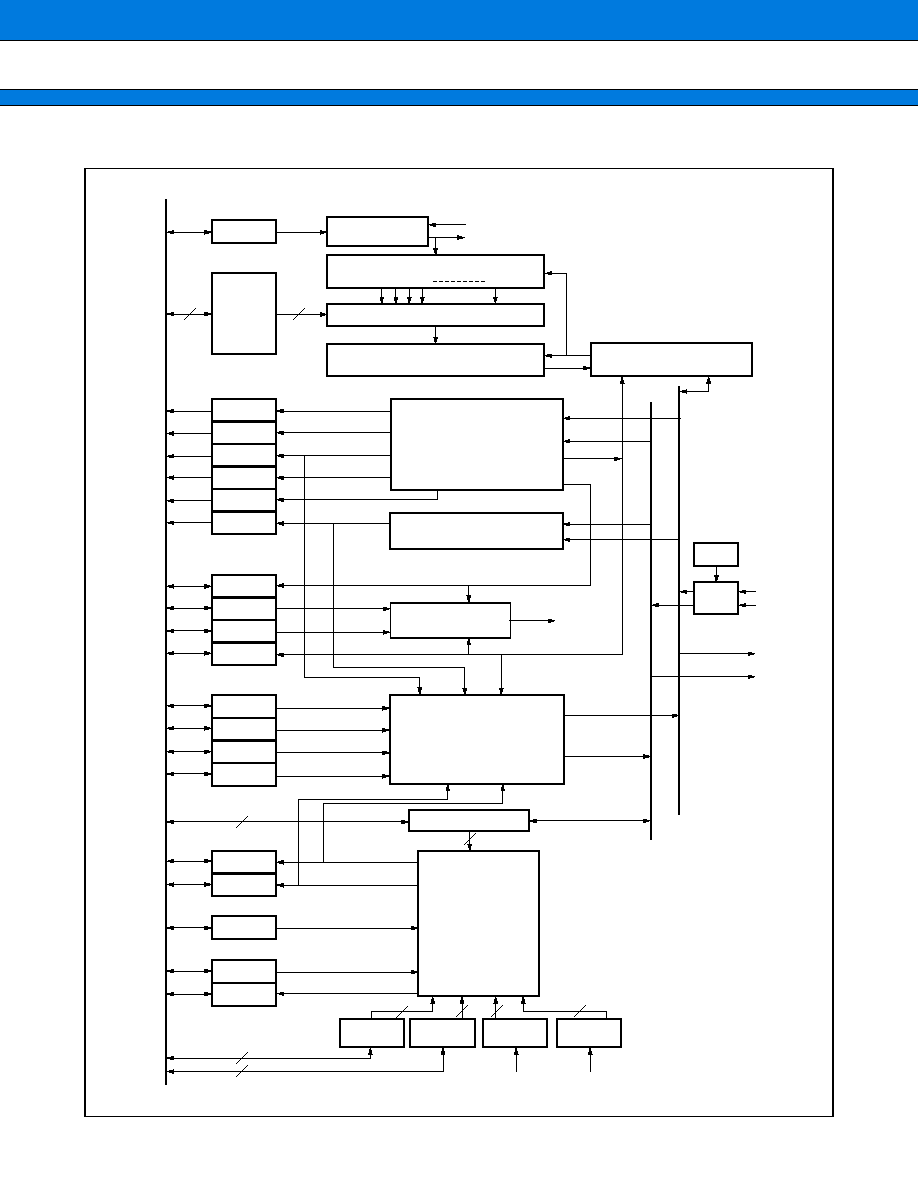

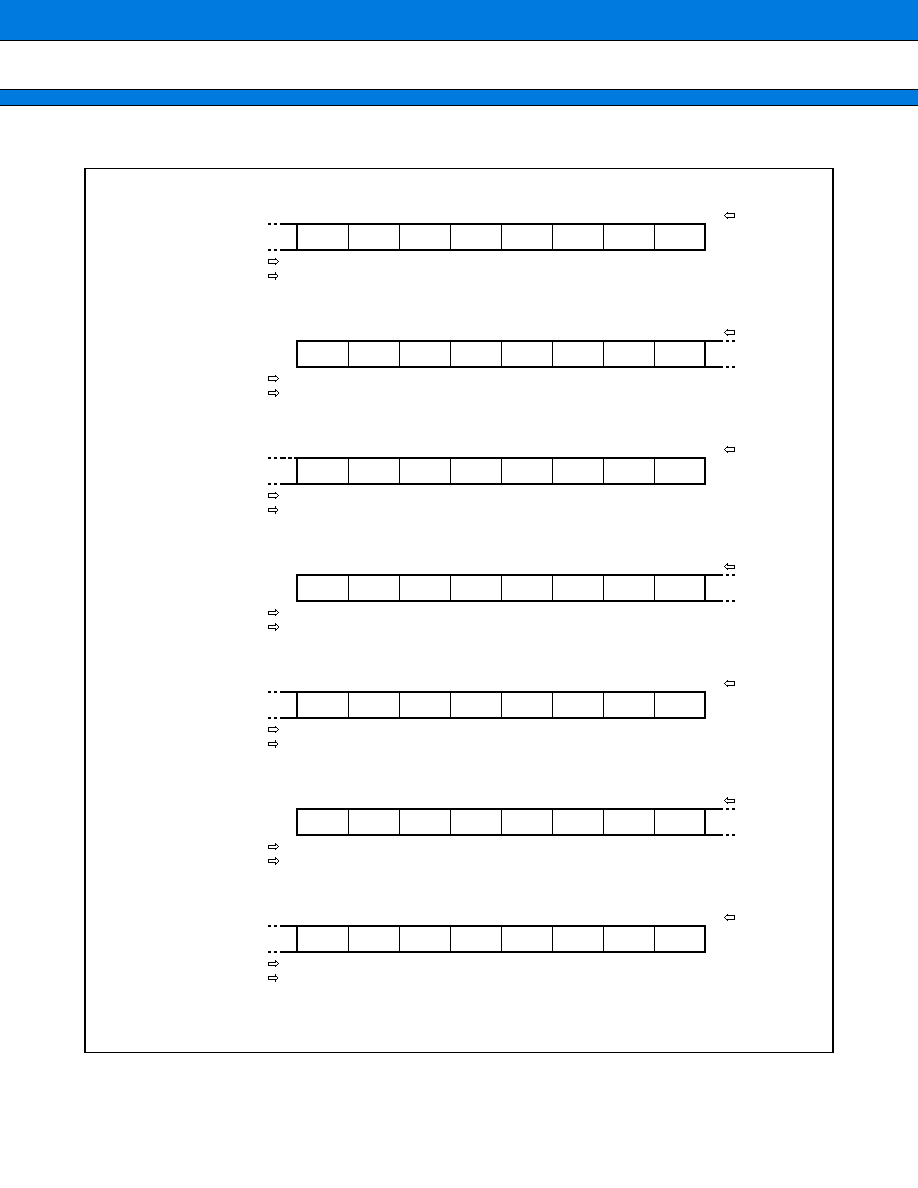

CPU CORE

1.

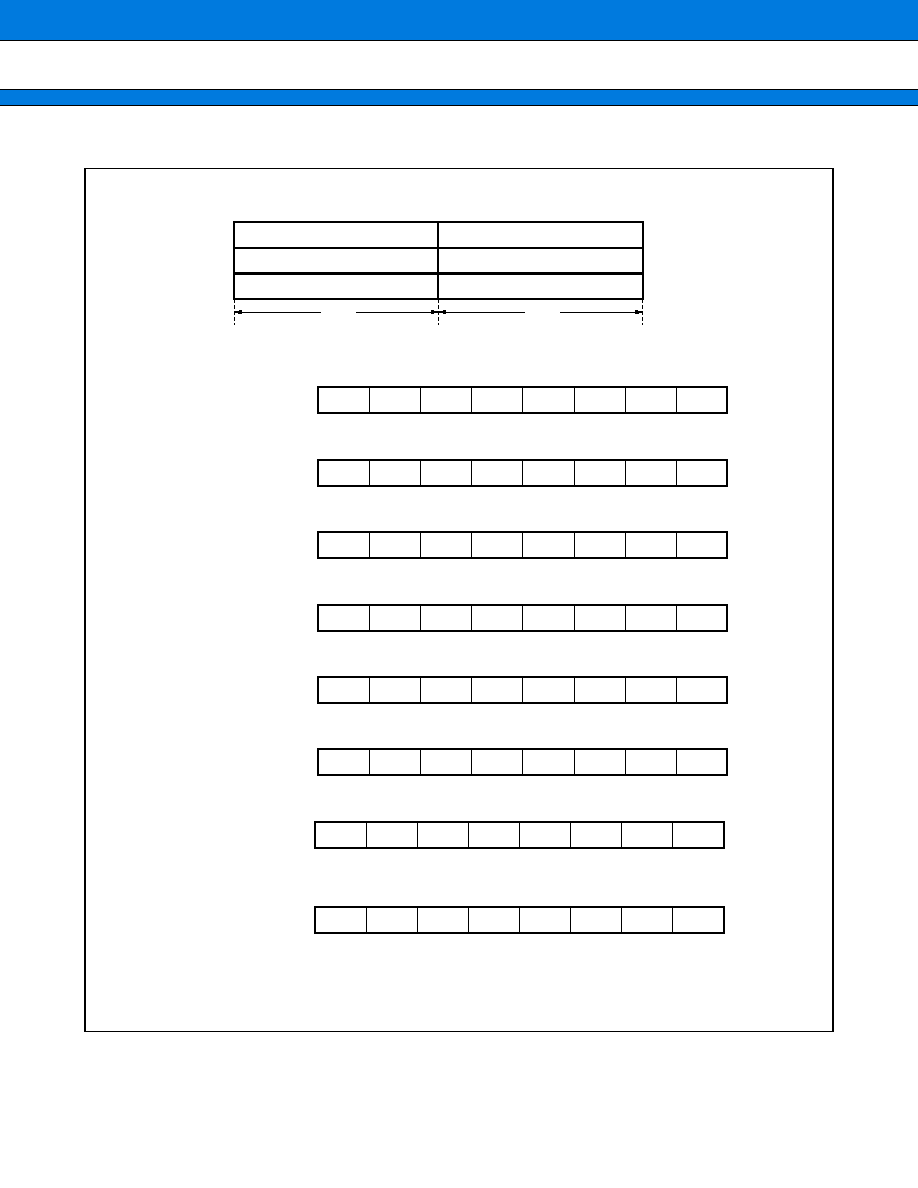

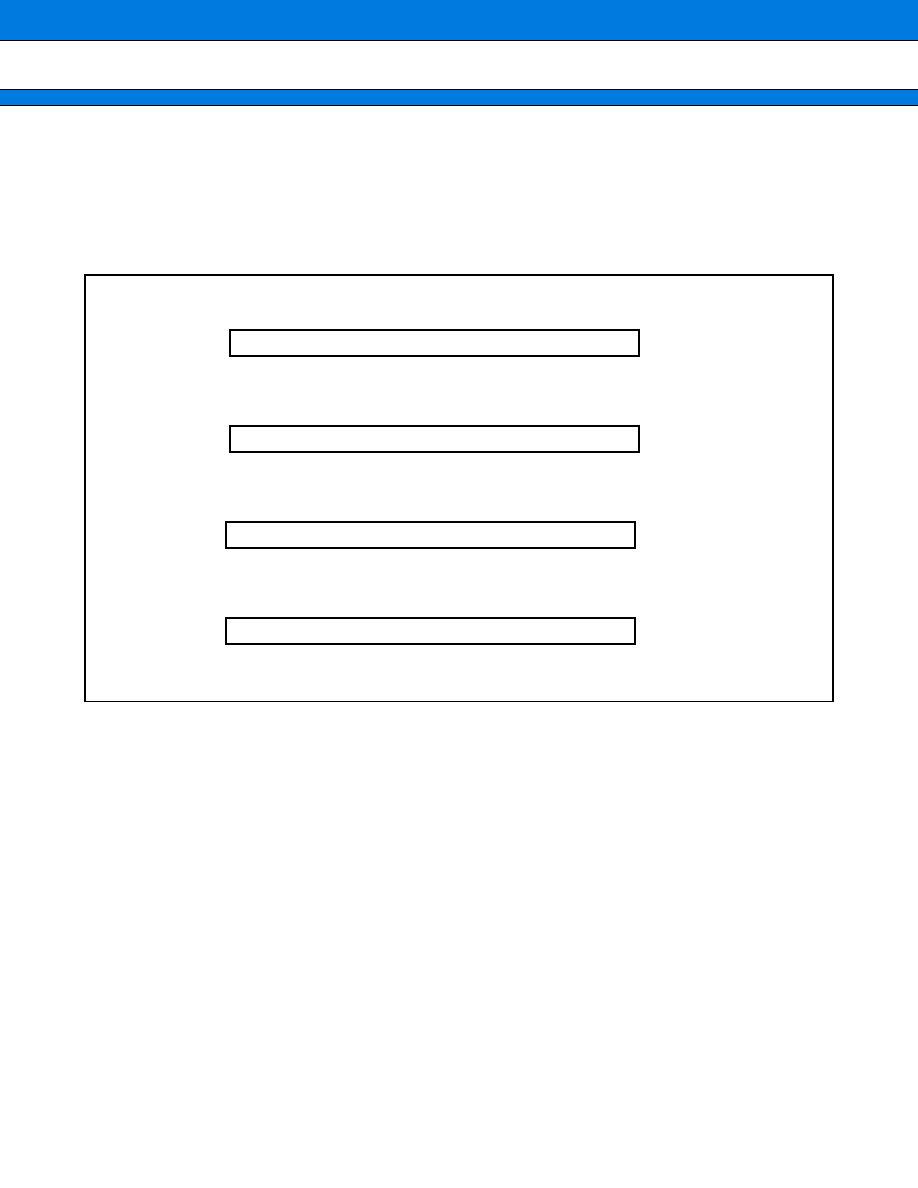

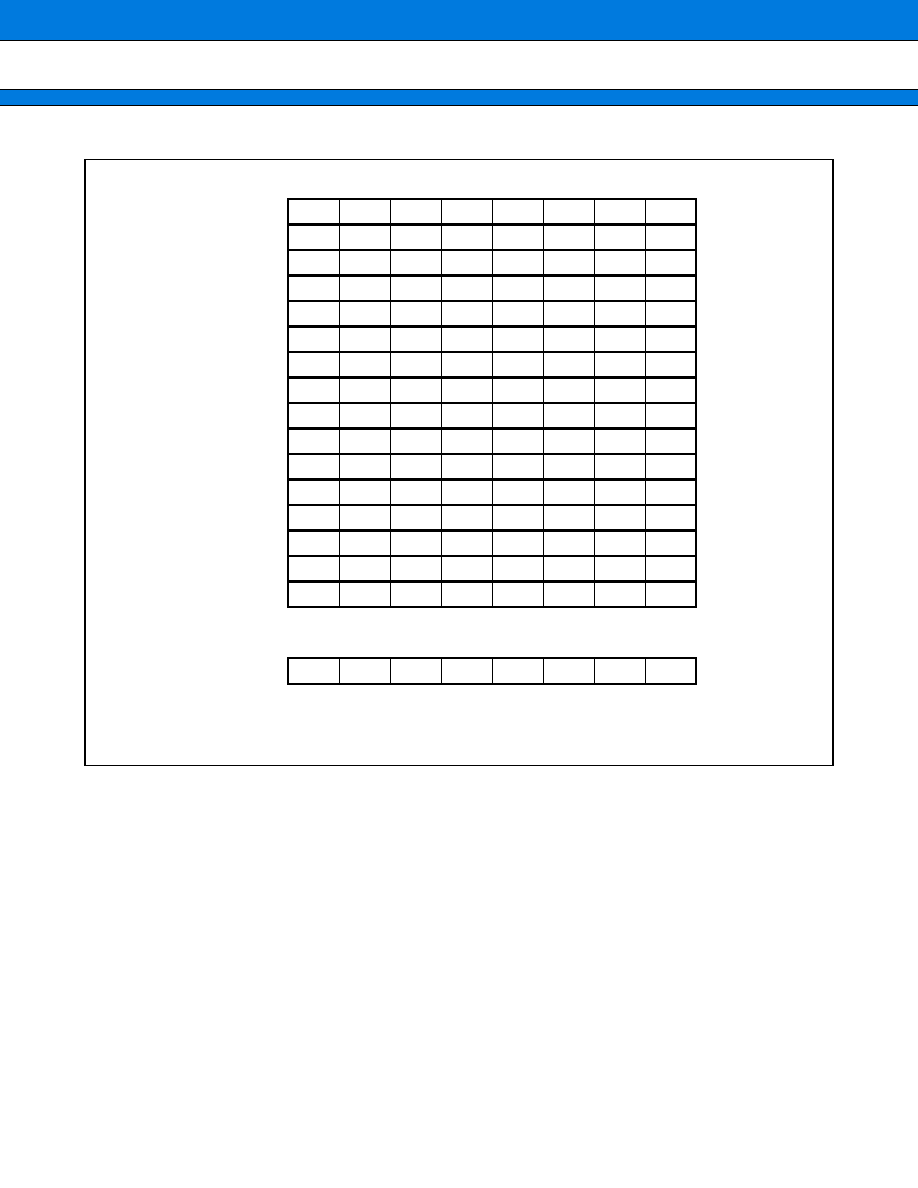

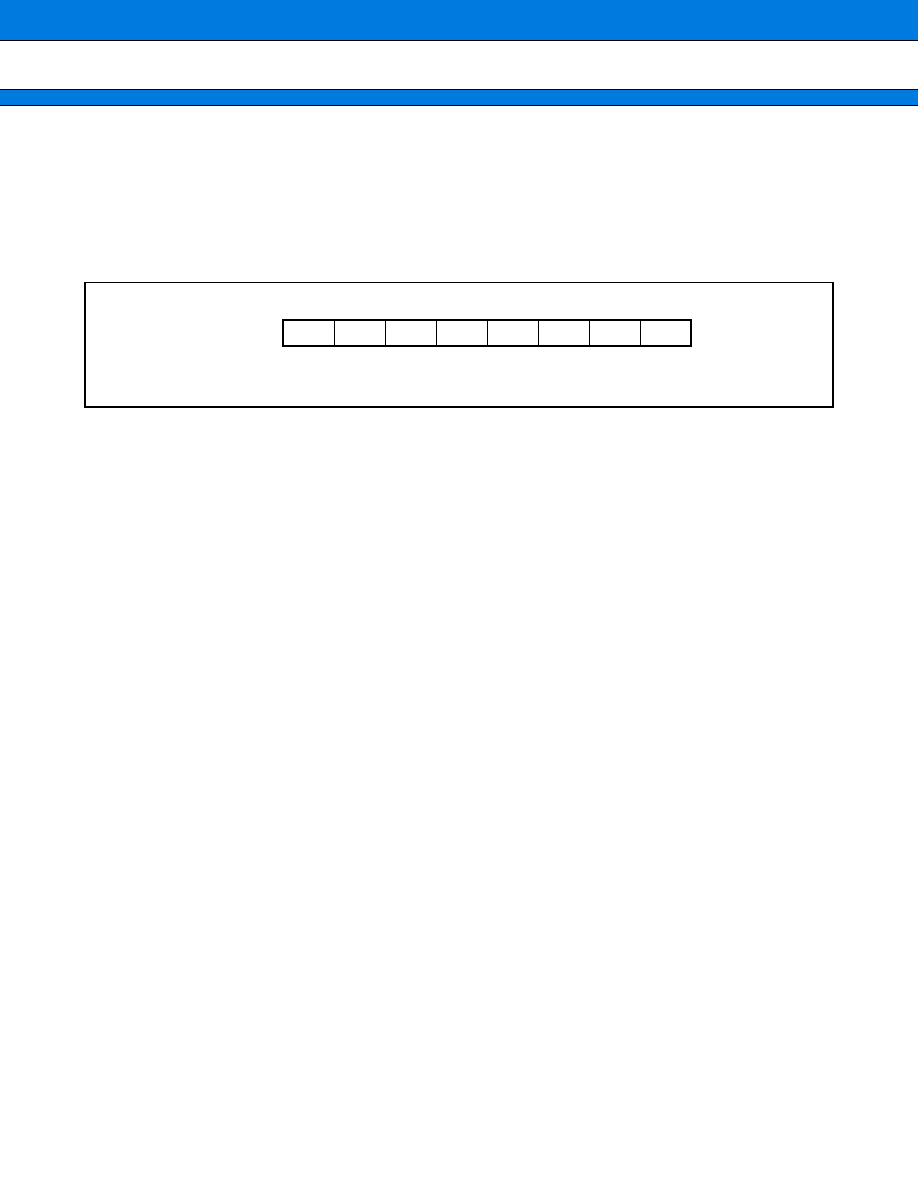

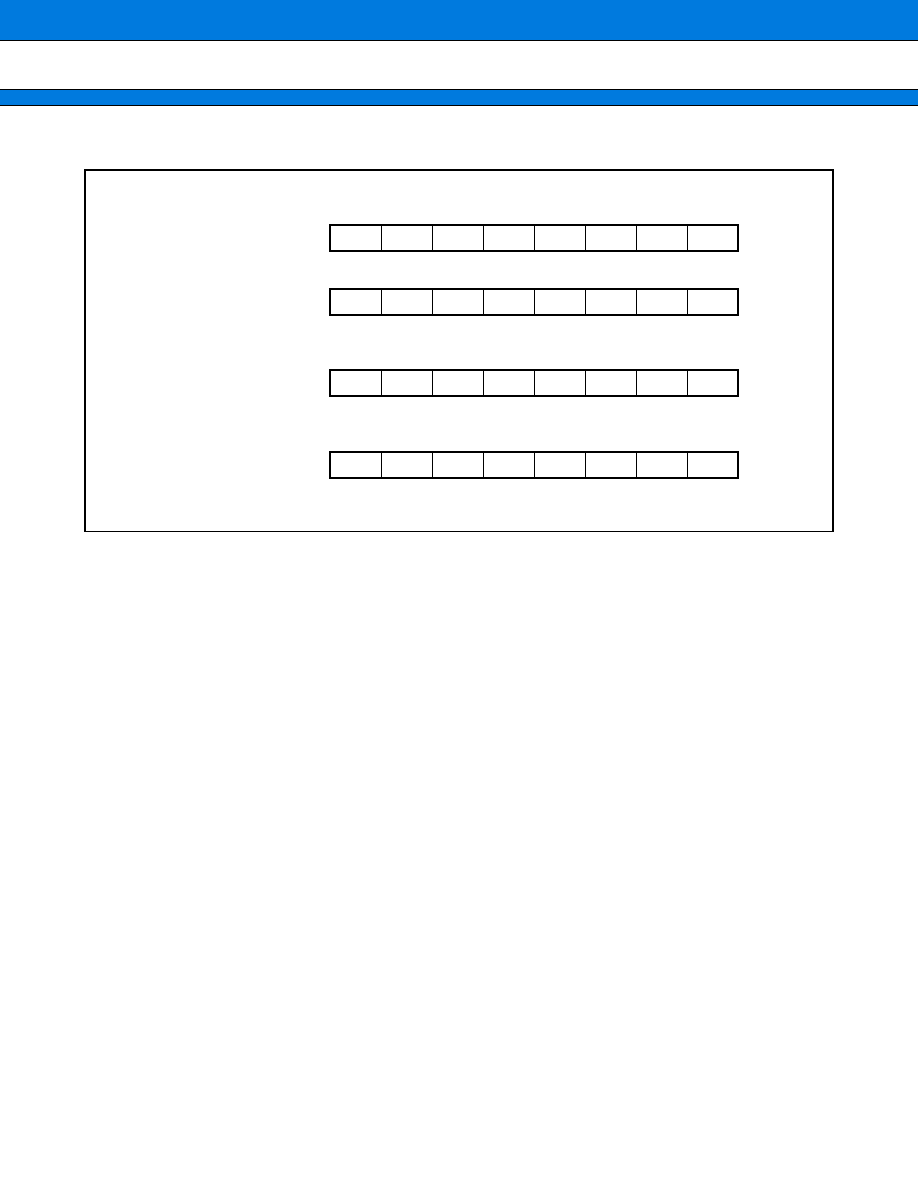

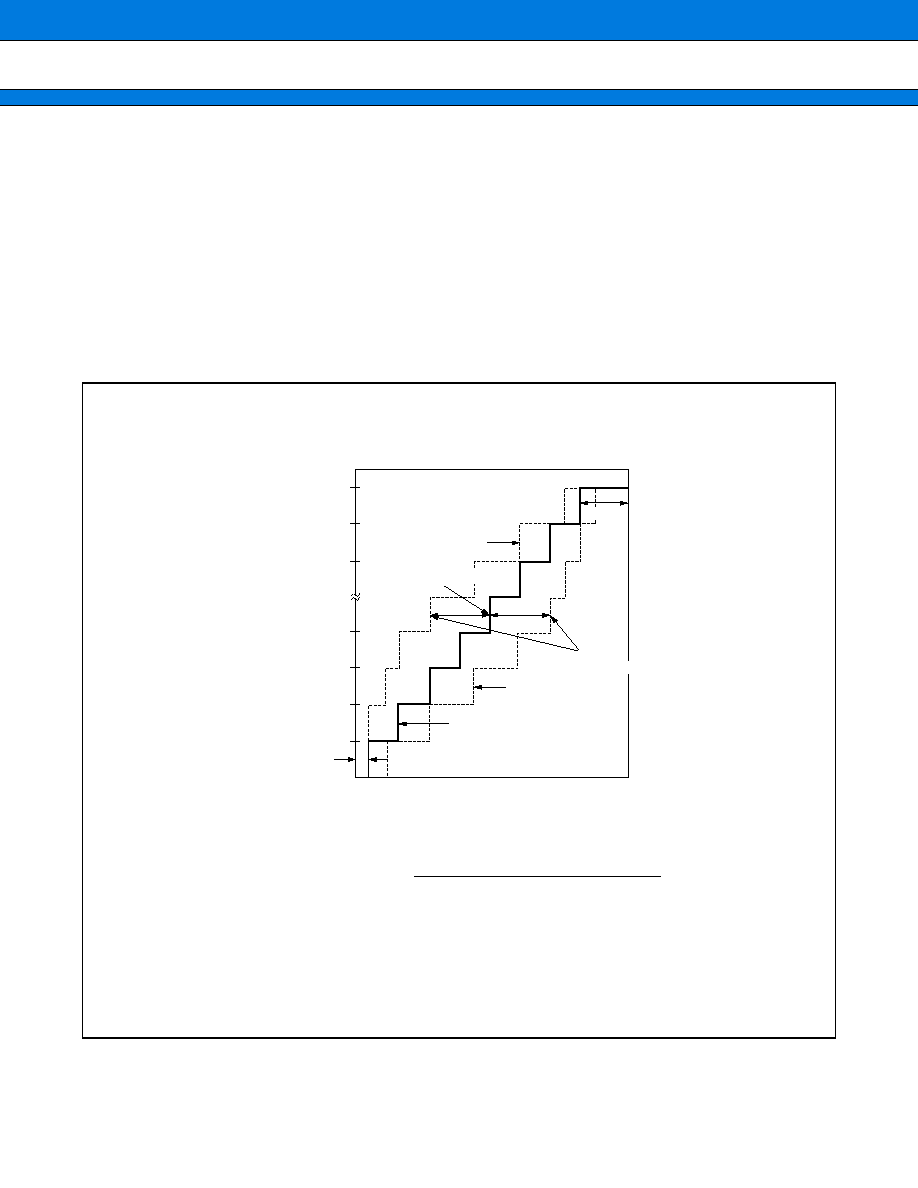

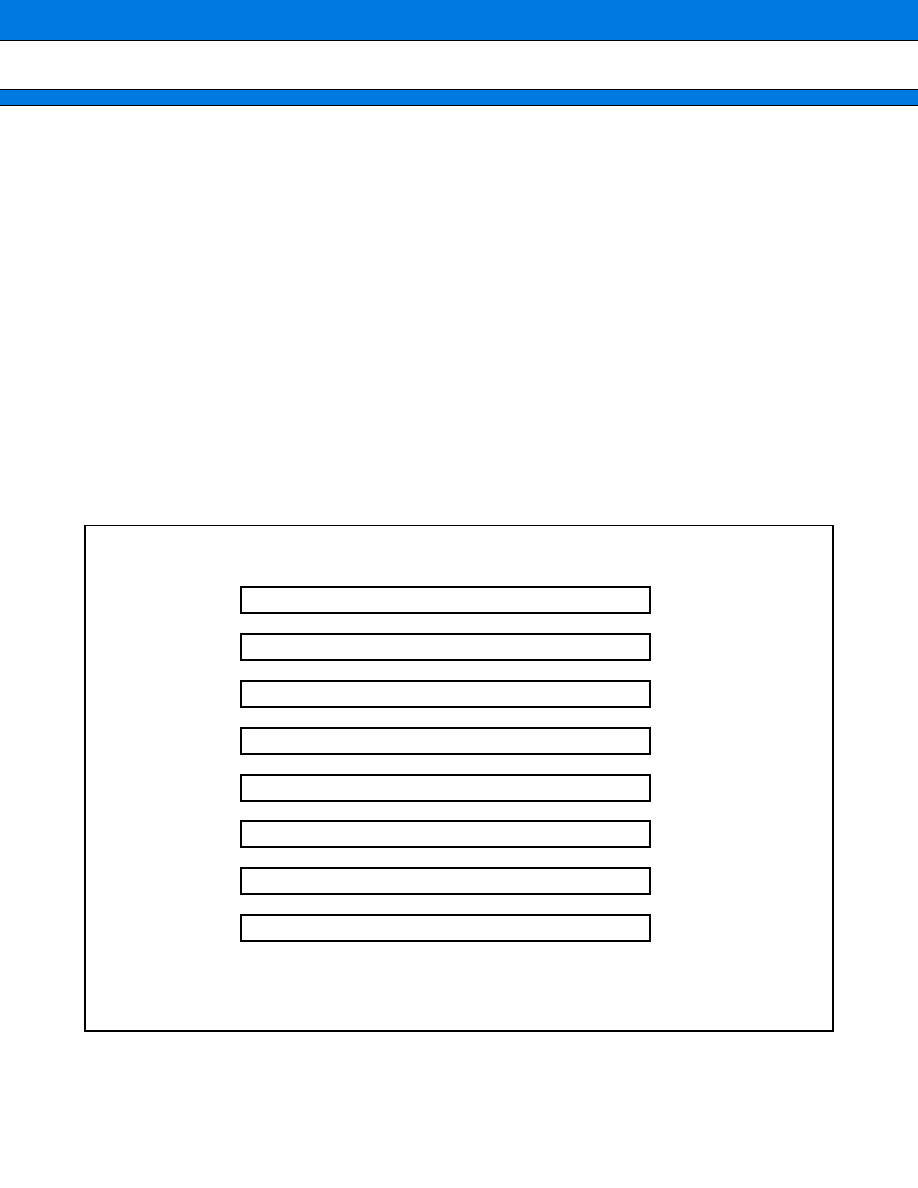

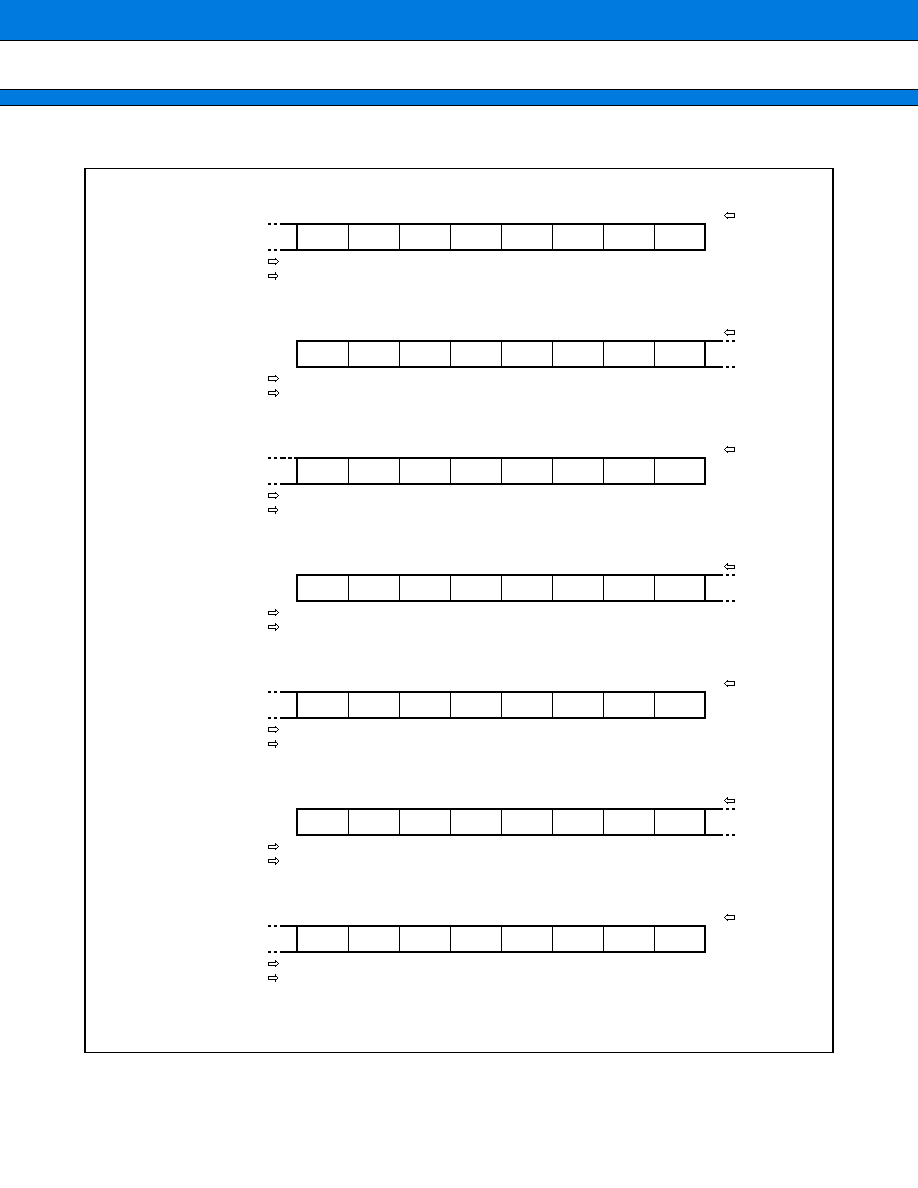

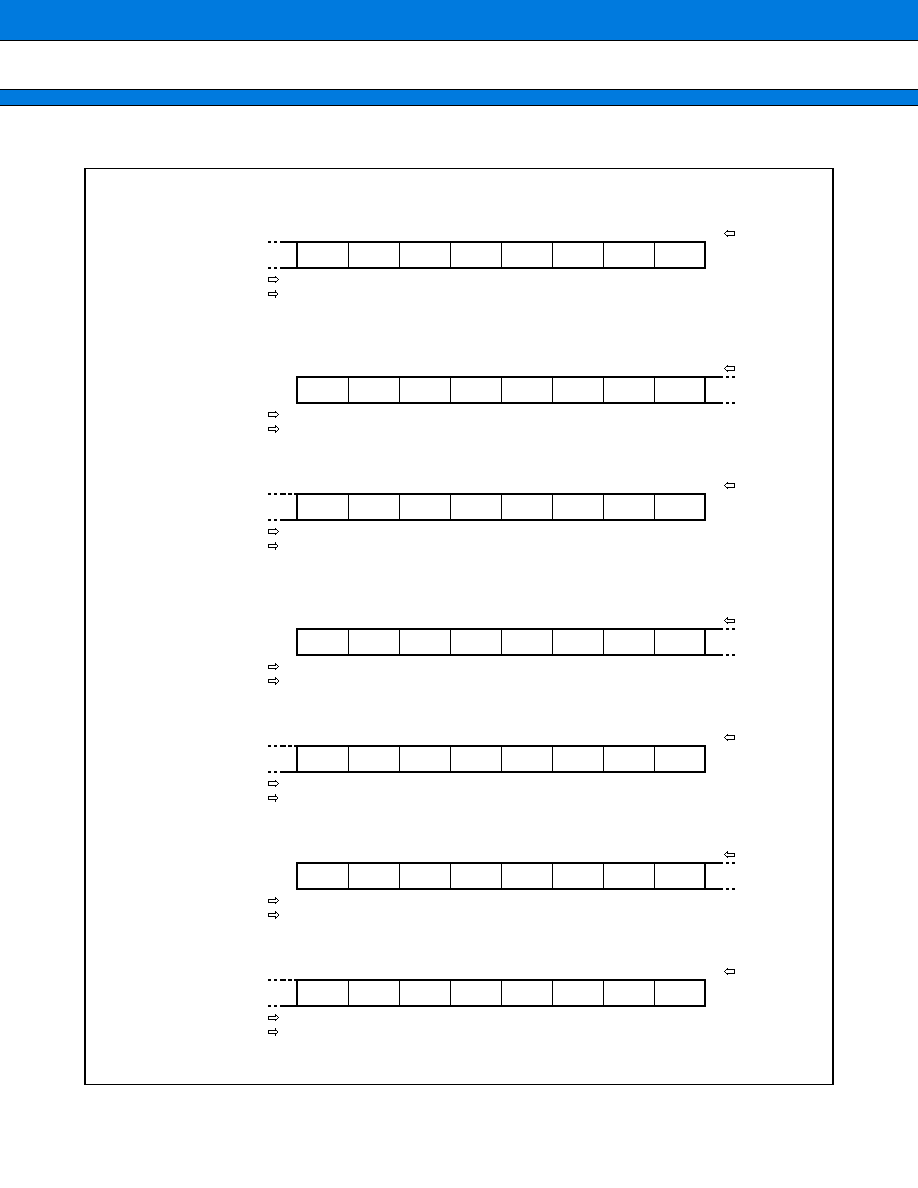

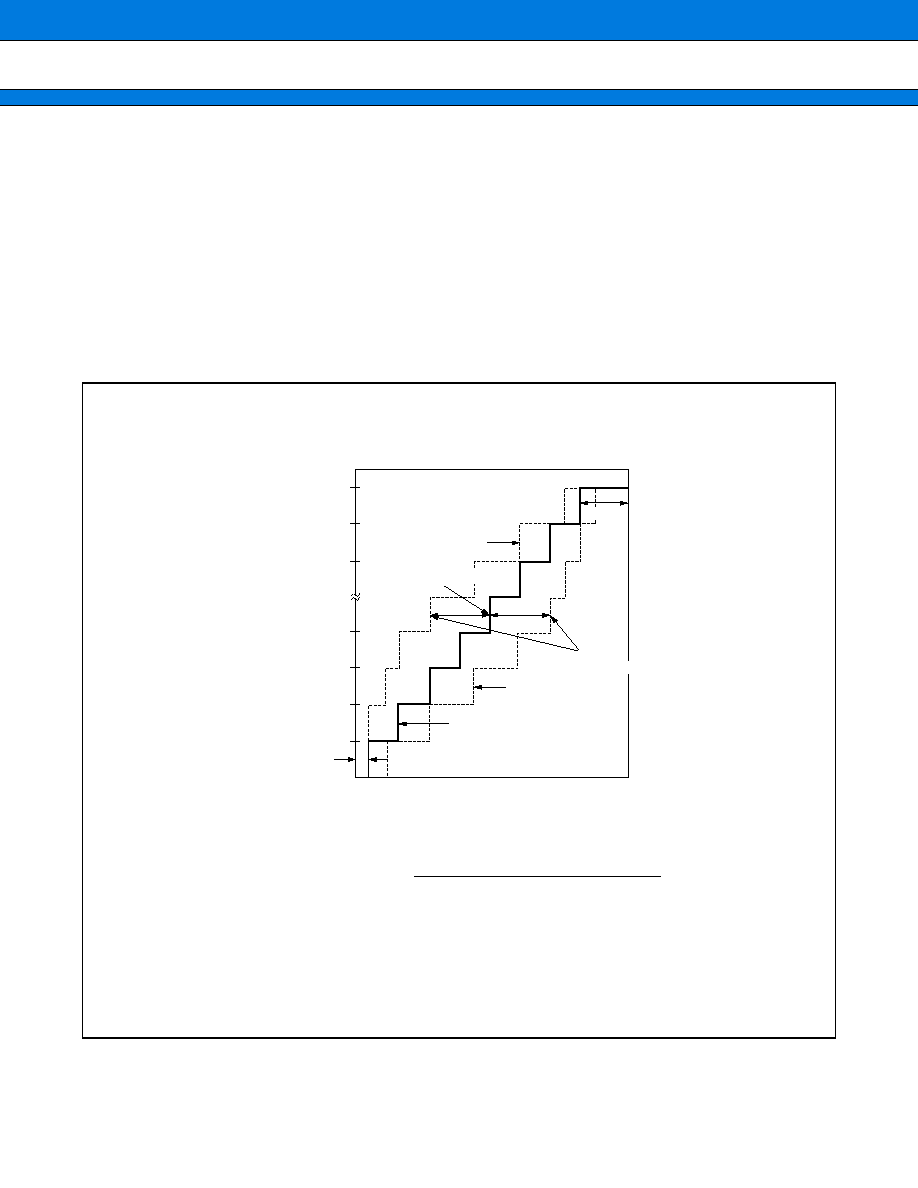

Memory Space

Internal memory area

00

:

0000

00

:

03FF

00

:

07FF

00

:

1000

00

:

1024

01

:

1000

01

:

1FFF

03

:

C000

03

:

FFFF

04

:

0000

04

:

3FFF

05

:

0000

05

:

07FF

08

:

0000

0F

:

4000

0F

:

FFFF

10

:

0000

10

:

07FF

18

:

0000

1F

:

4000

1F

:

FFFF

Flash Memory

on external bus

(F361GA)

Bootsector

128 K

128 K

128 K

64 K

16 K

16 K

32 K

128 K

128 K

128 K

64 K

16 K

16 K

32 K

CAN

Fixed Reset Vector

Bootsector

Flash Memory

on F-bus

(FV360GA, F362GA)

Boot ROM

F-bus RAM

D-bus RAM

I-RAM

DMA

IO Area

Direct

Direct (short) addressing

0..0FF

:

Byte access

0..1FF

:

Halfword access (16 bit)

0..3FF

:

Word access (32 bit)

01

:

1000 - 01

:

1400 on F361GA

03

:

D000 - 03

:

FFFF on F361GA, F362GA

04

:

0000 - 04

:

0FFF on F361GA, F362GA

0F

:

F000 - 0F

:

F7FF on F361GA

Addresses for CAN and flash

memory on external bus depend

on settings for the chip select areas

CS7 and CS1 respectively.

The addresses given here are valid

for the CS1 and CS7 settings done

in the Boot ROM.

MB91360G Series

29

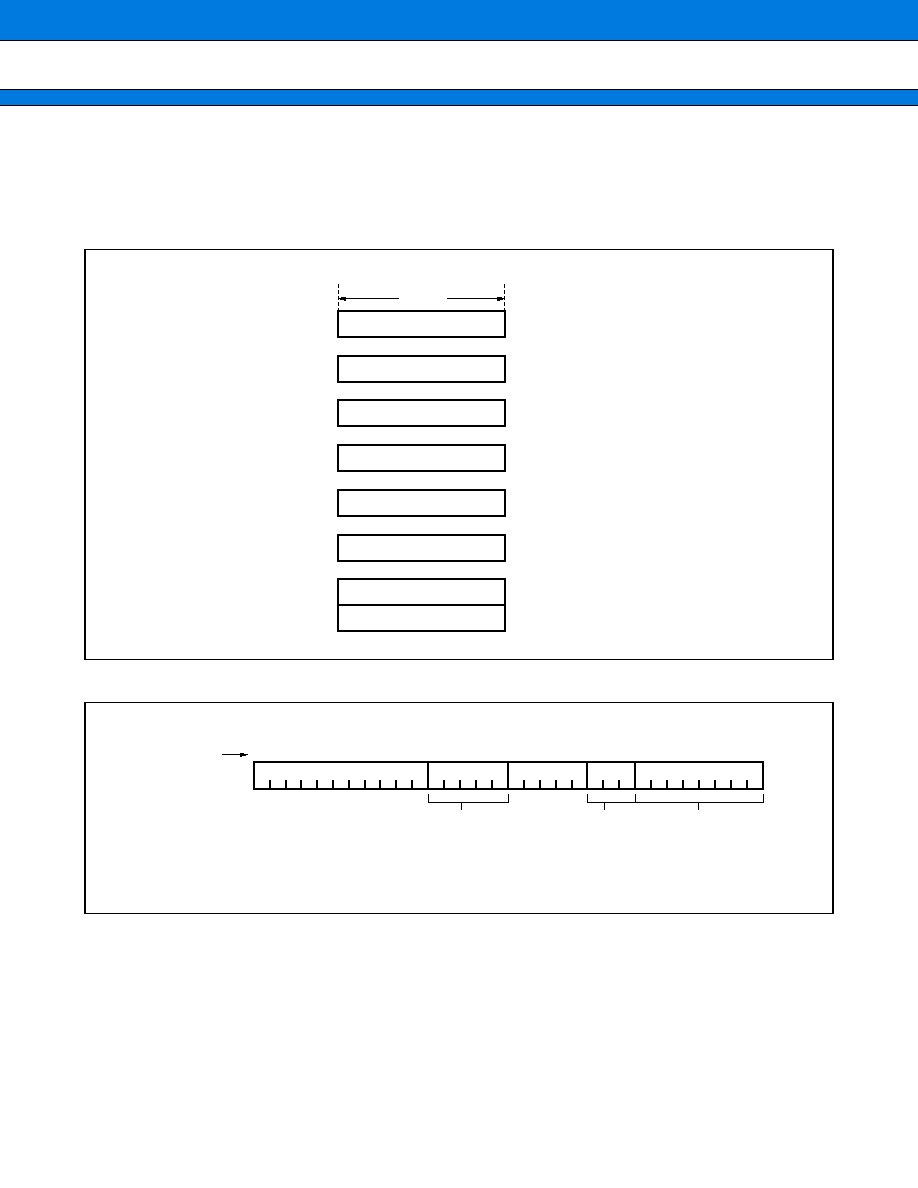

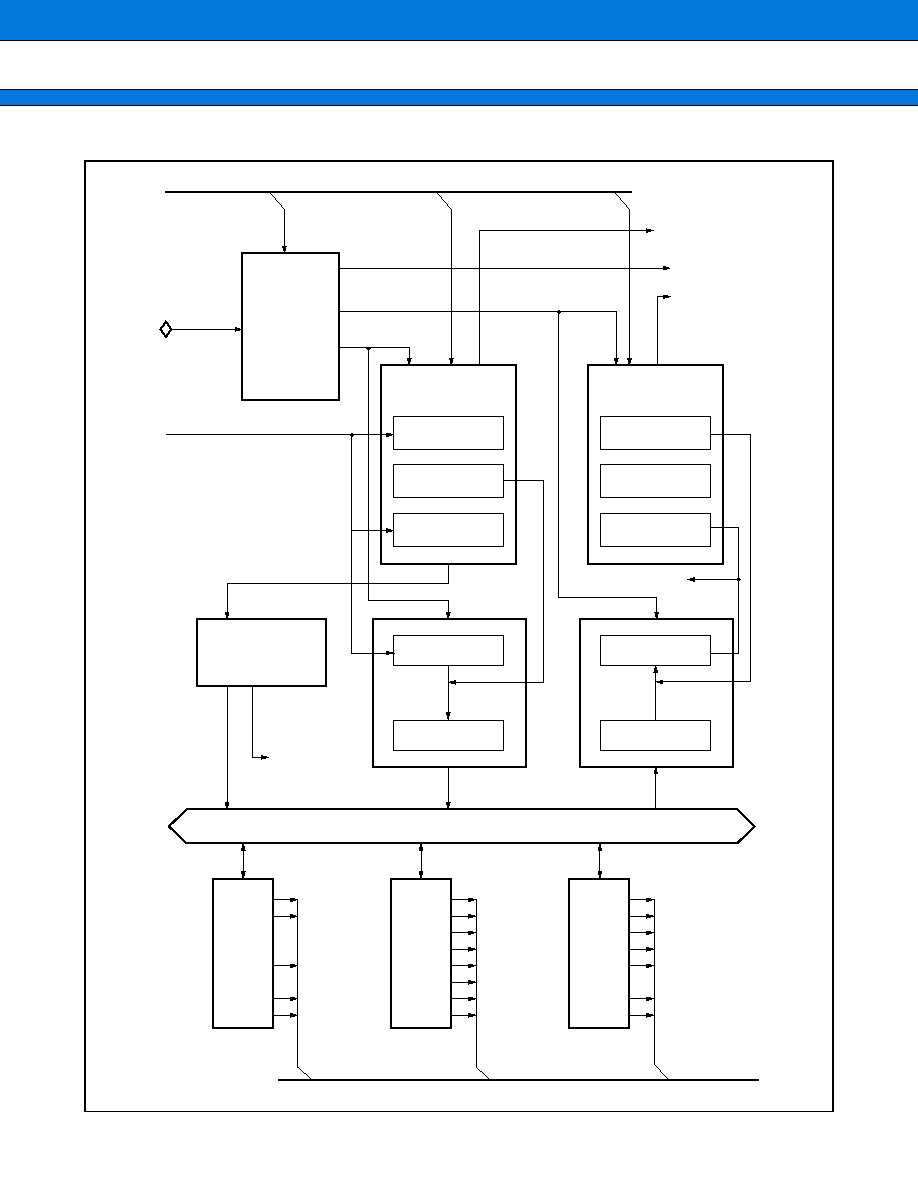

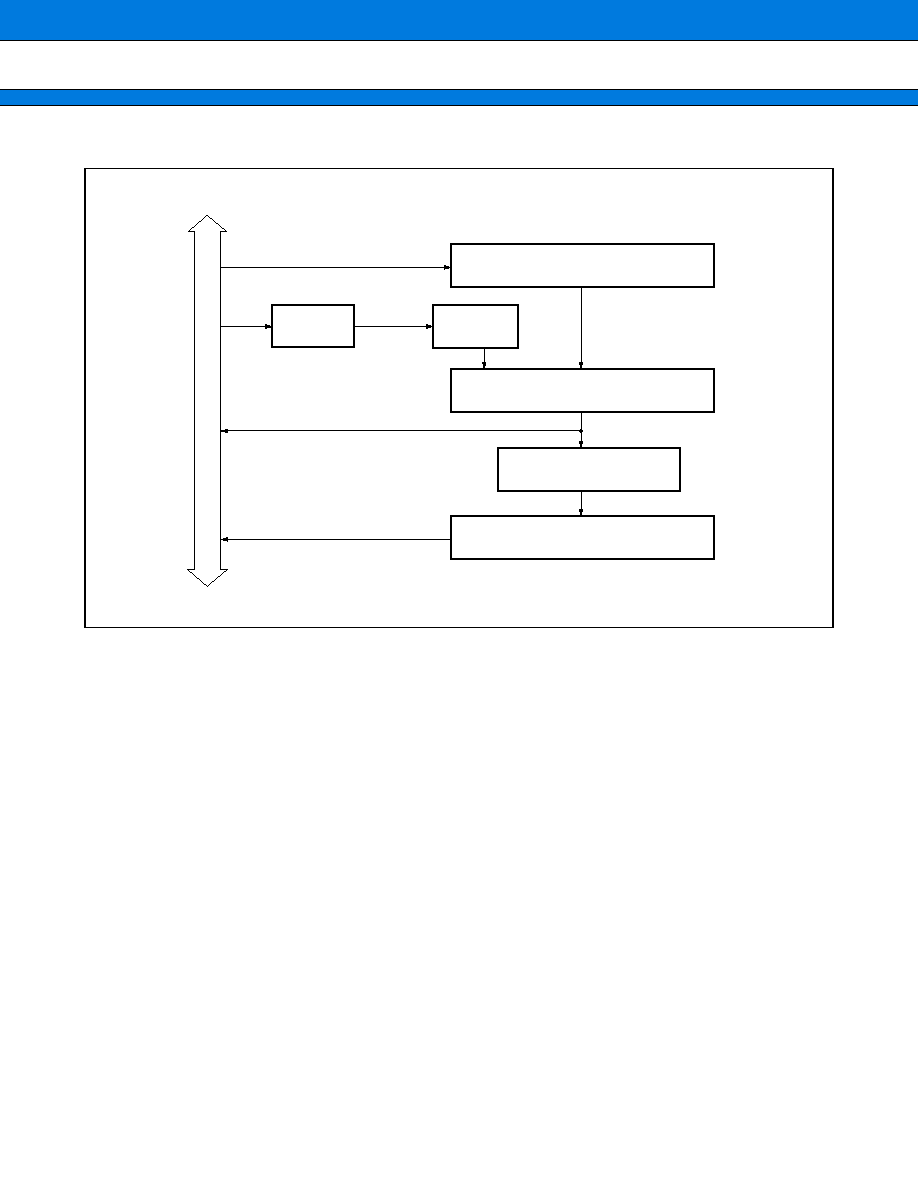

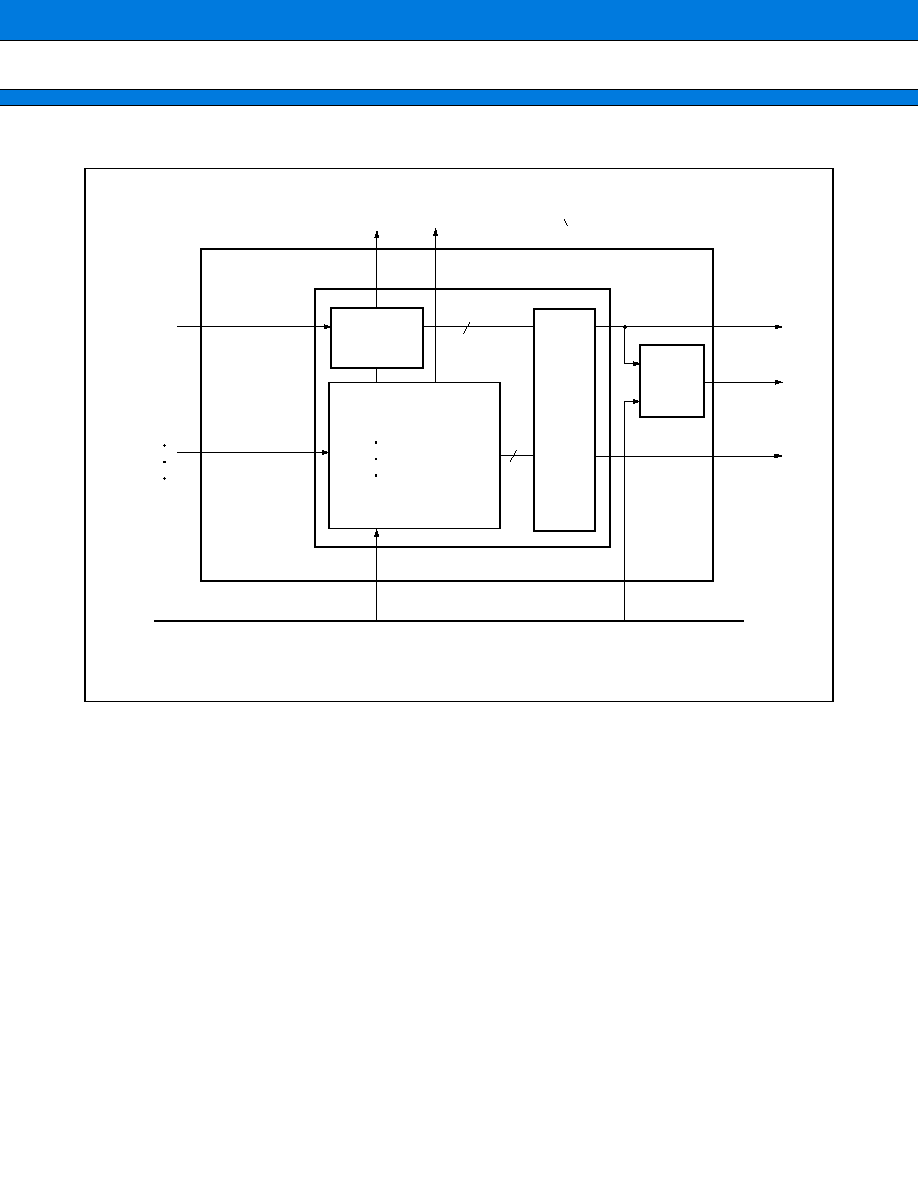

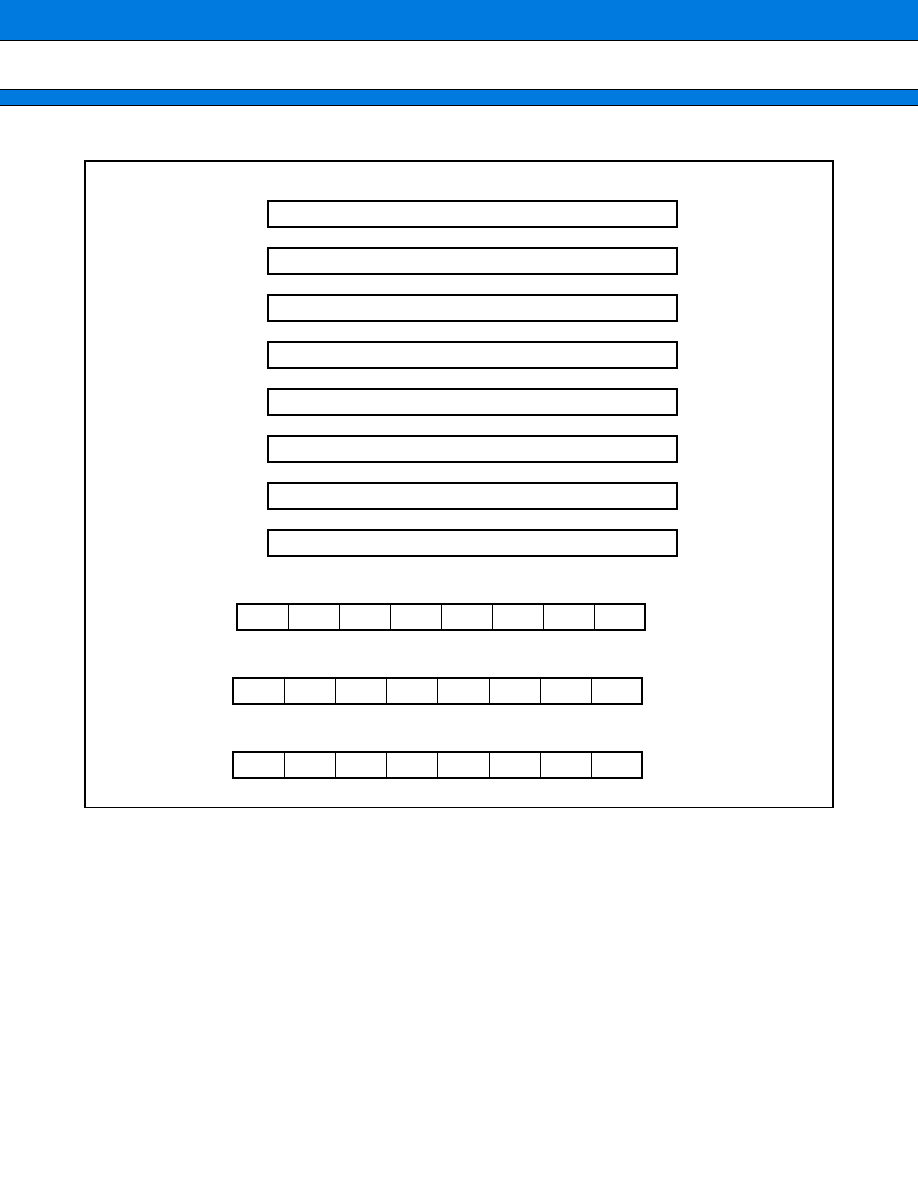

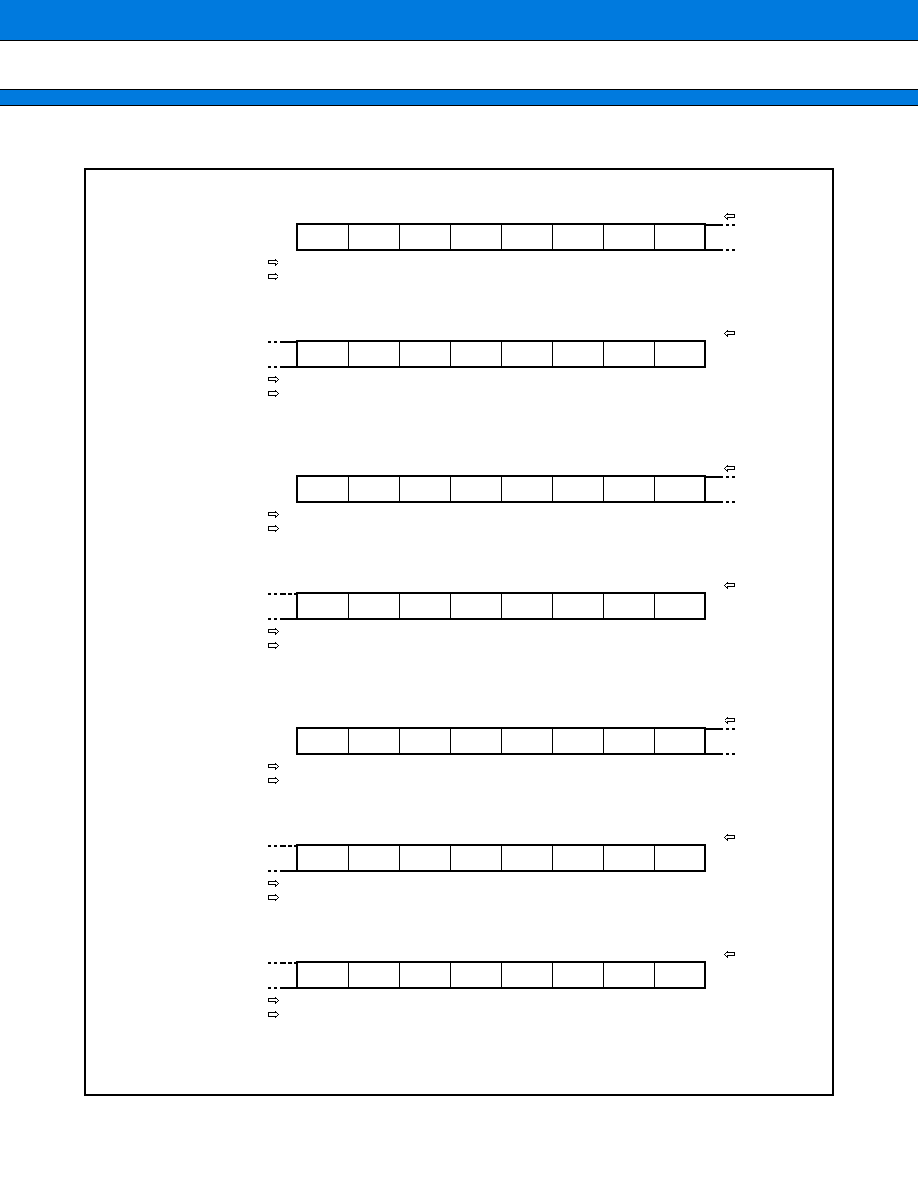

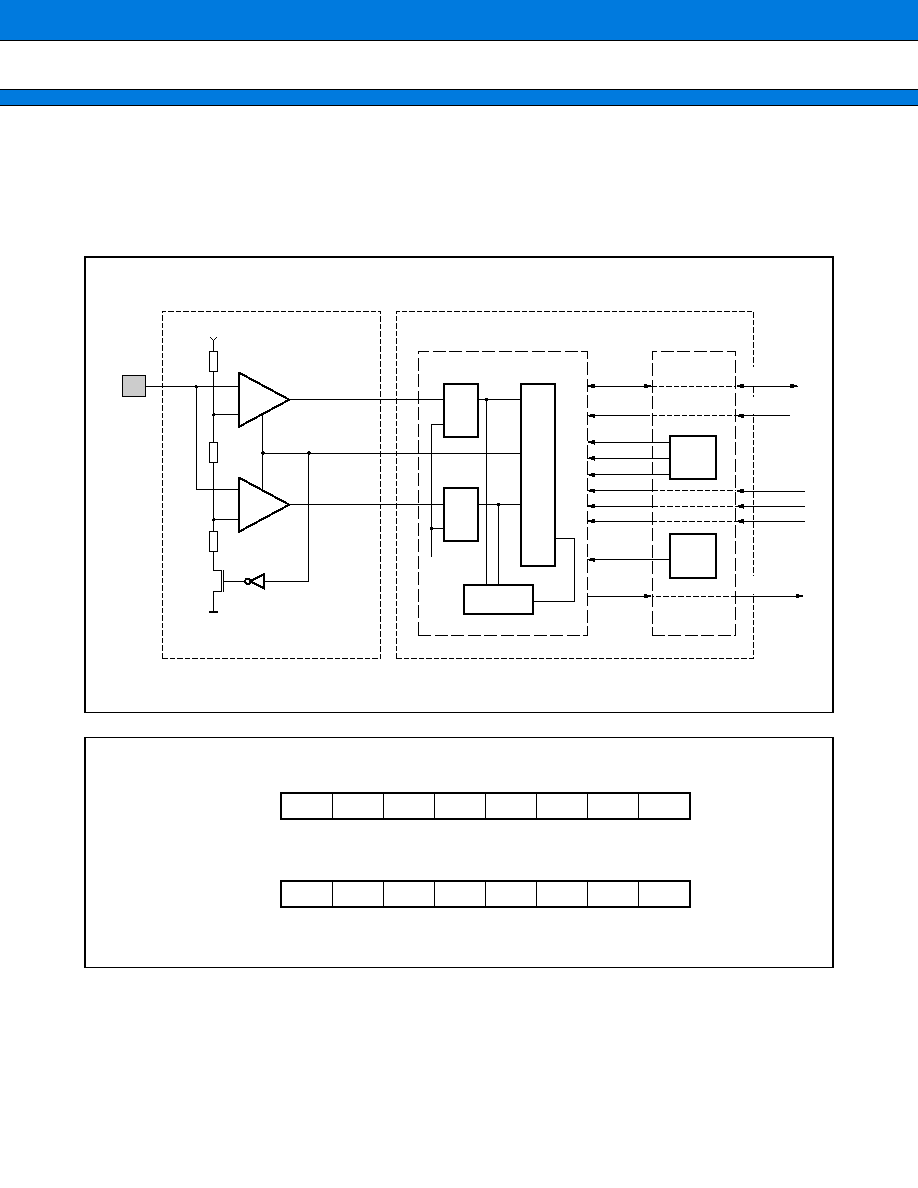

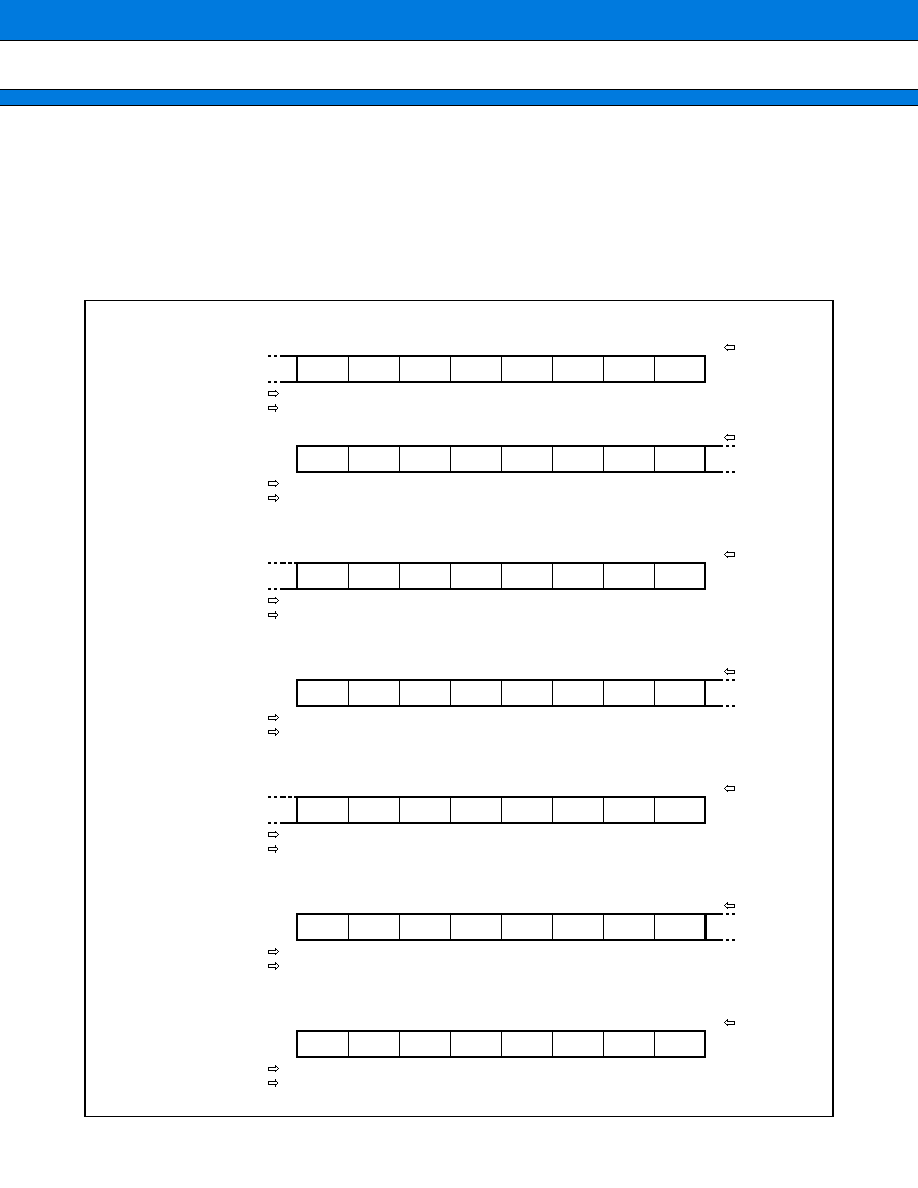

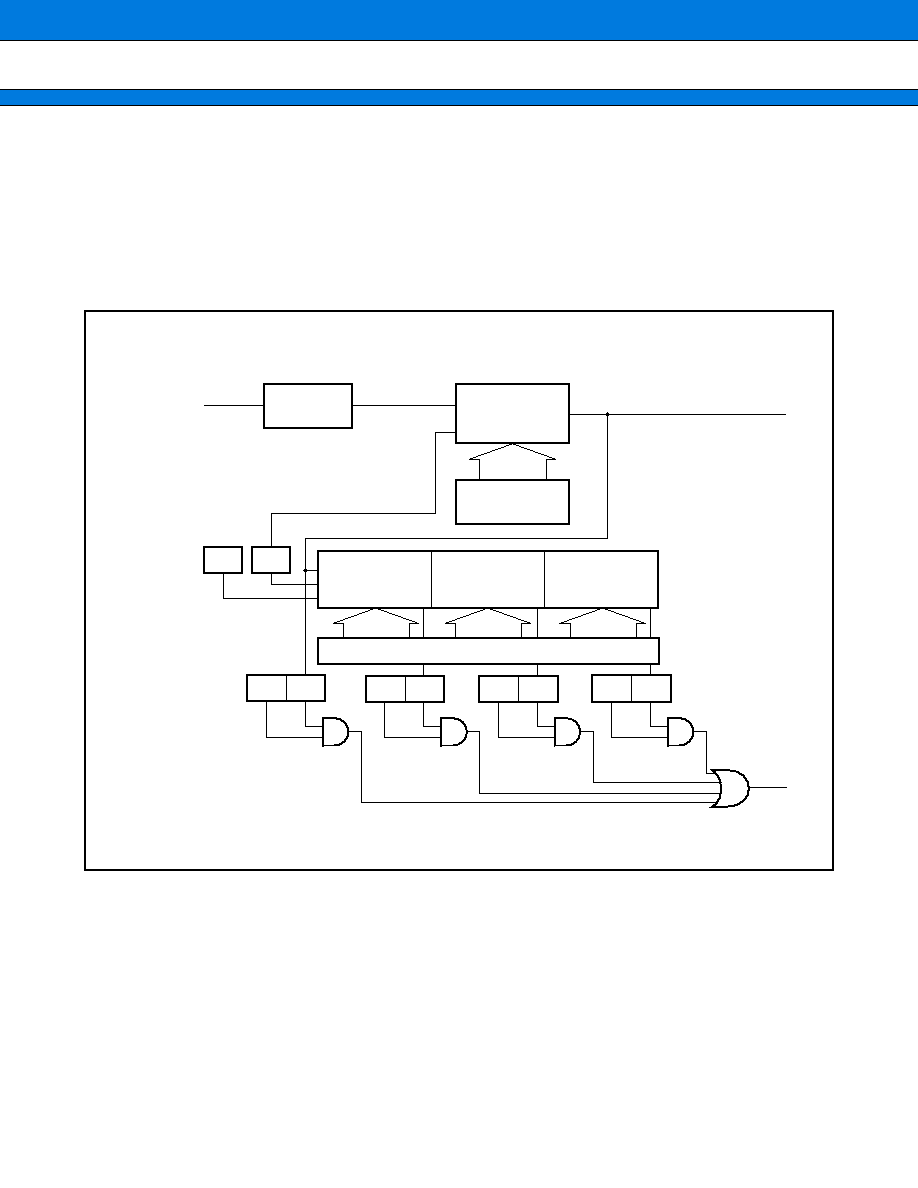

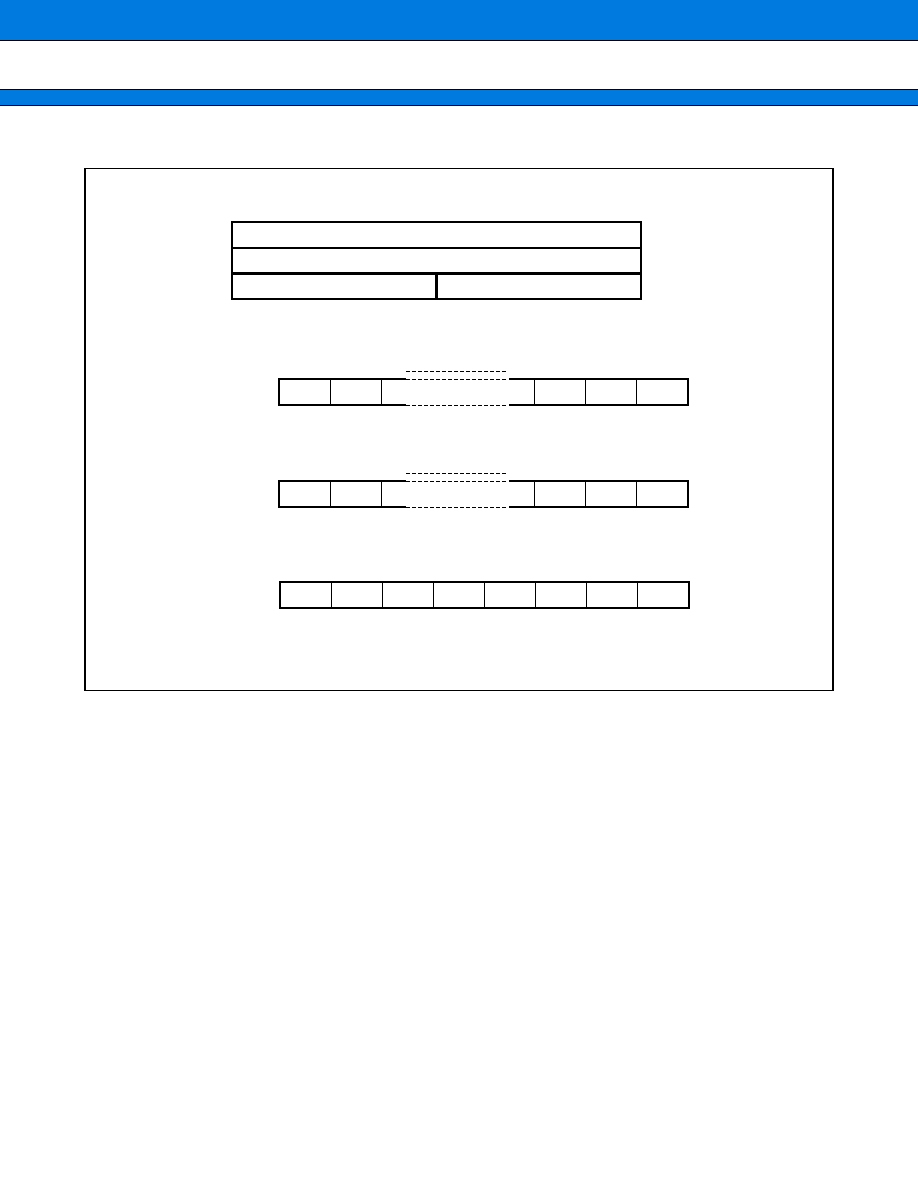

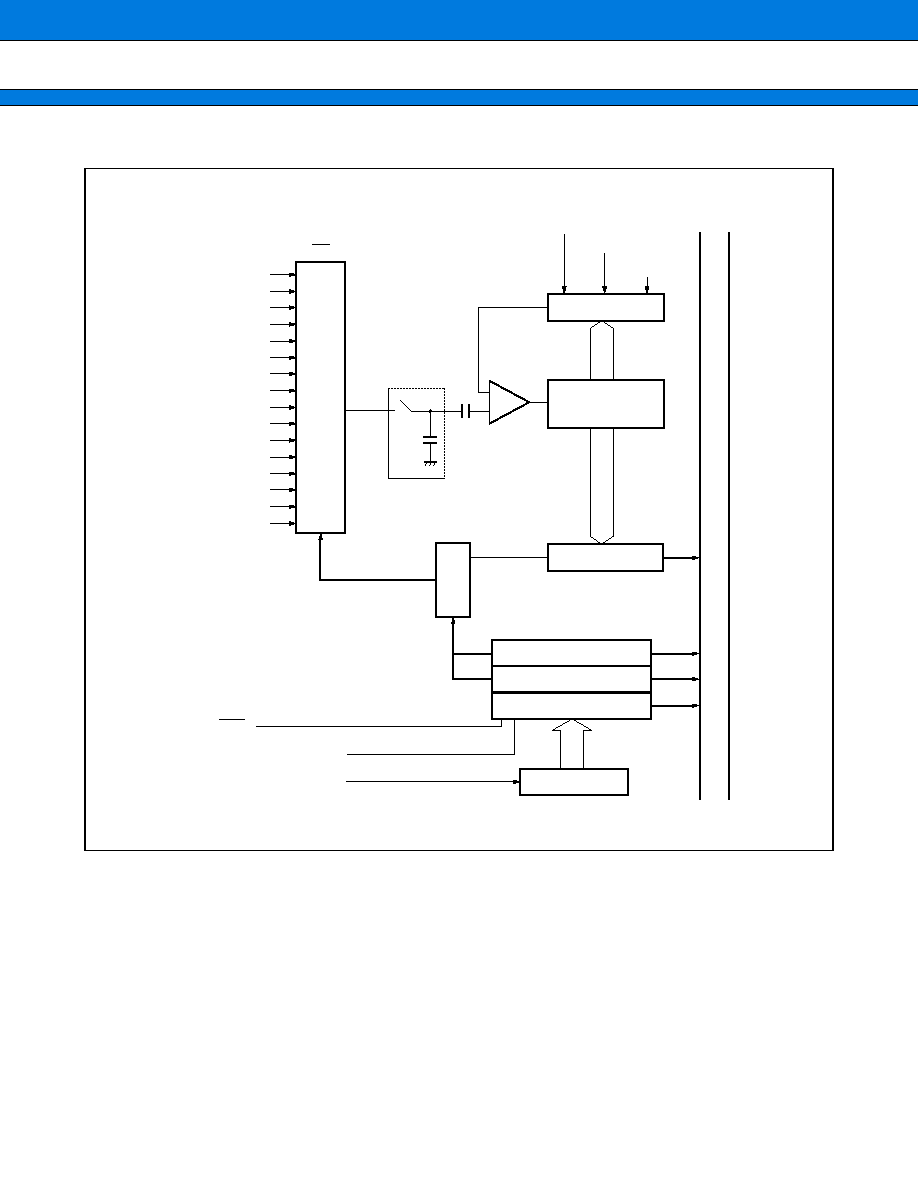

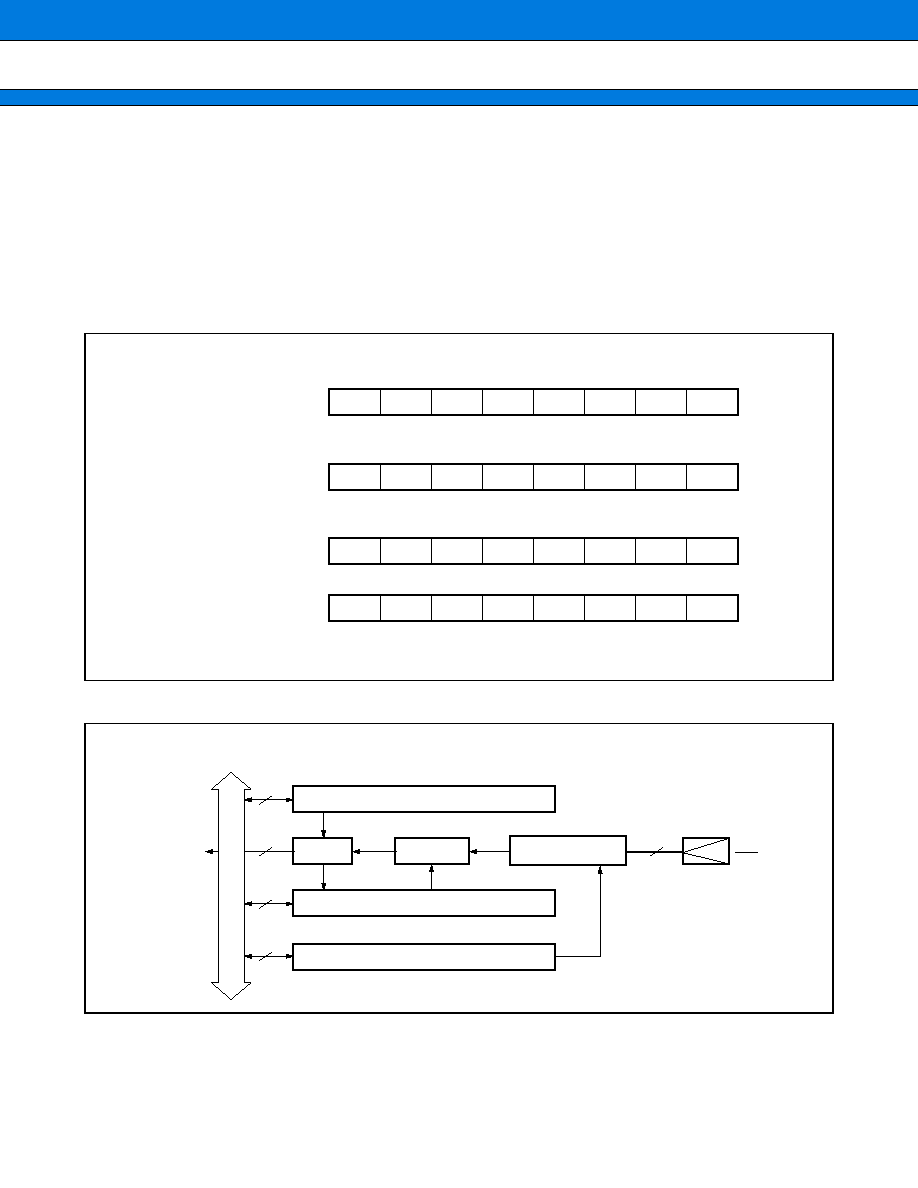

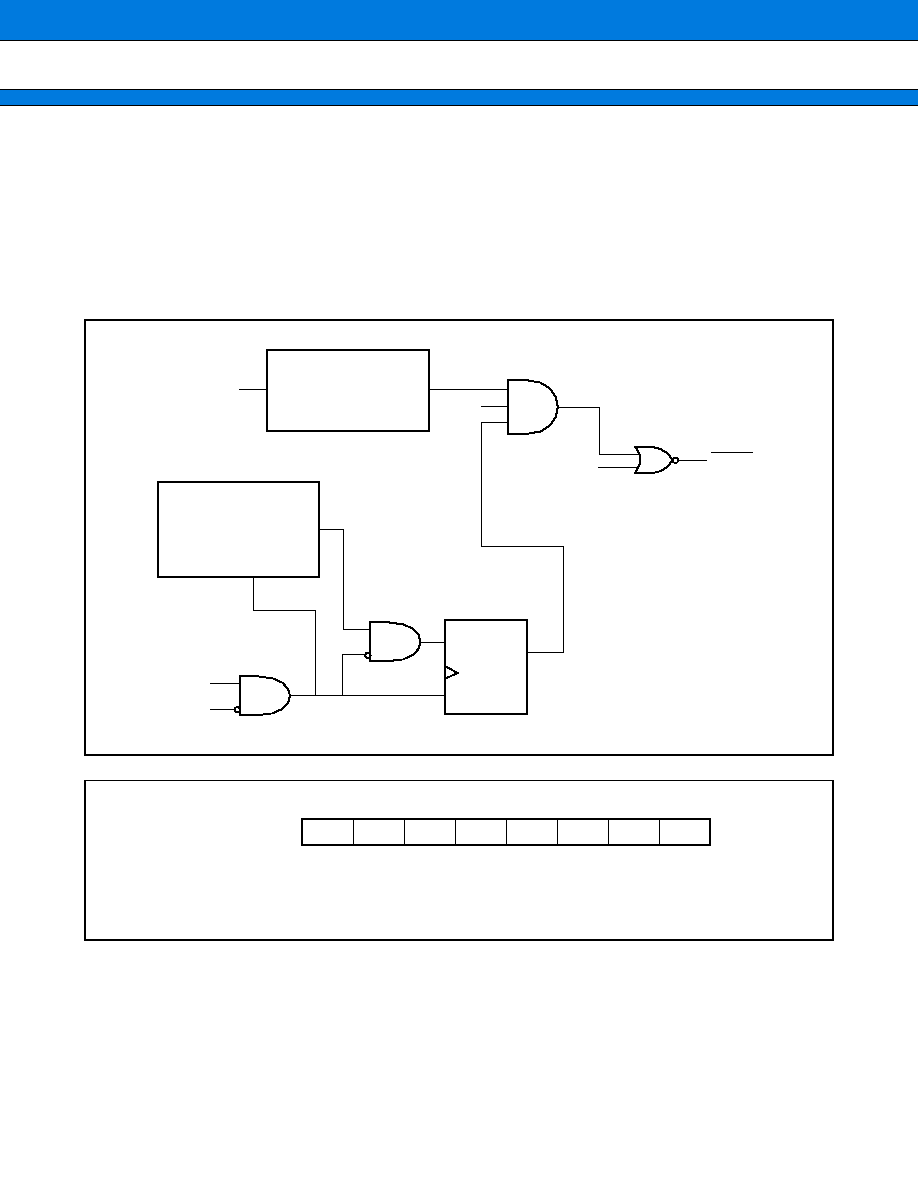

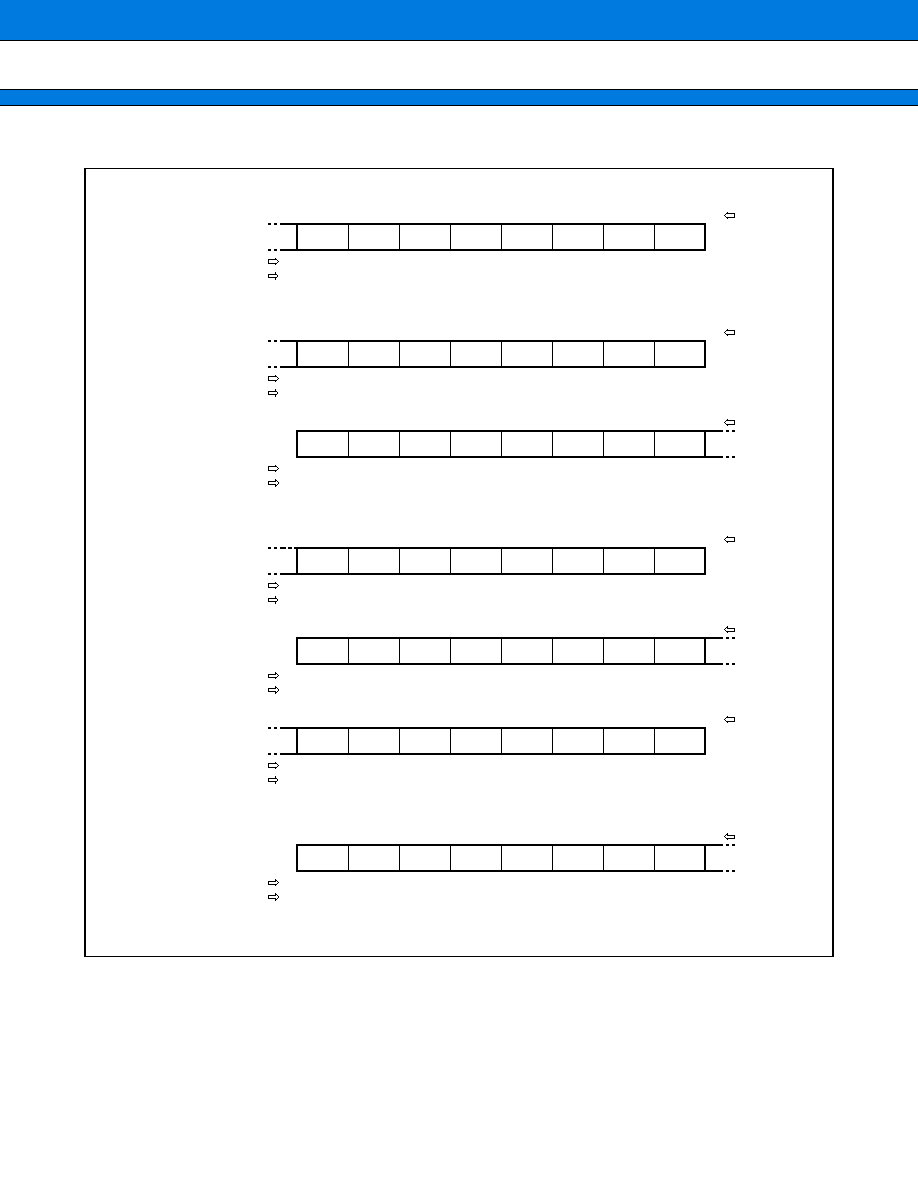

2.

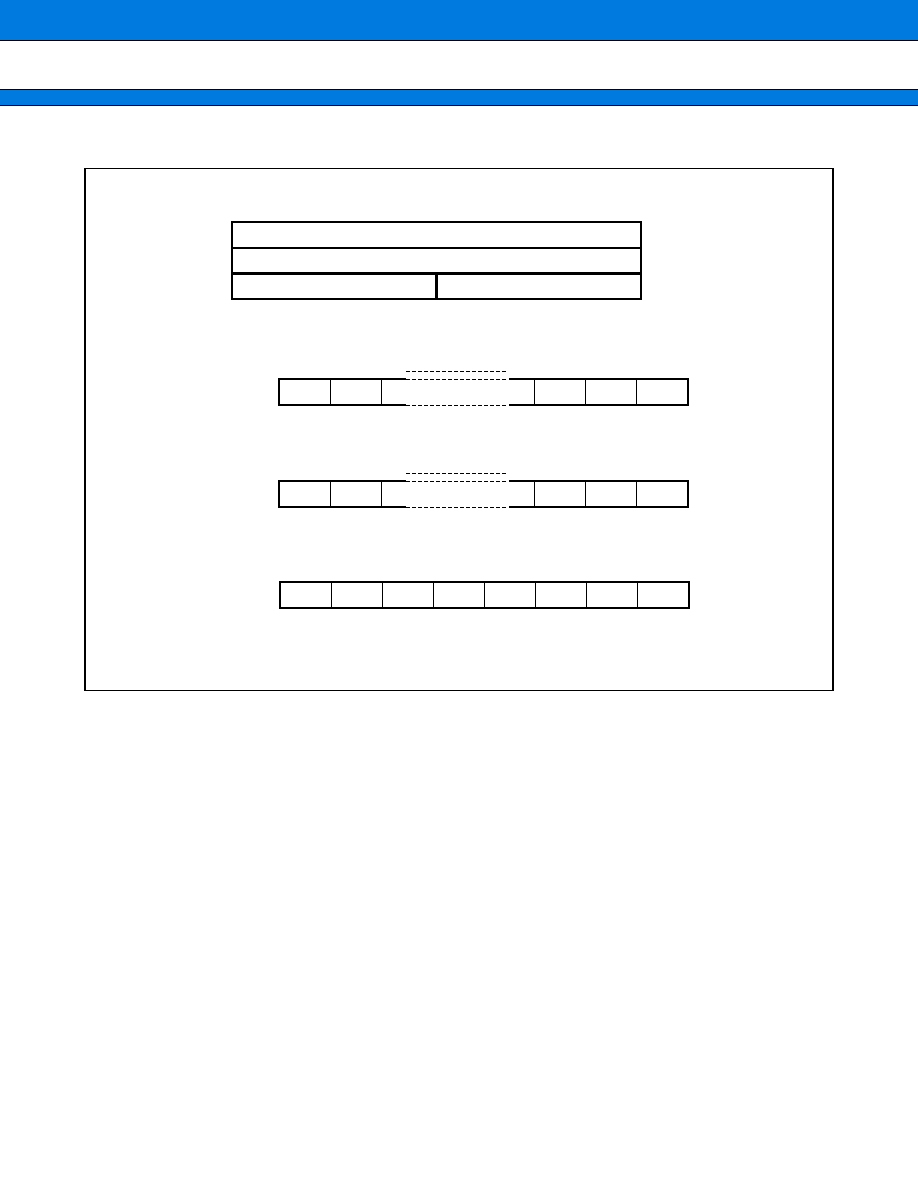

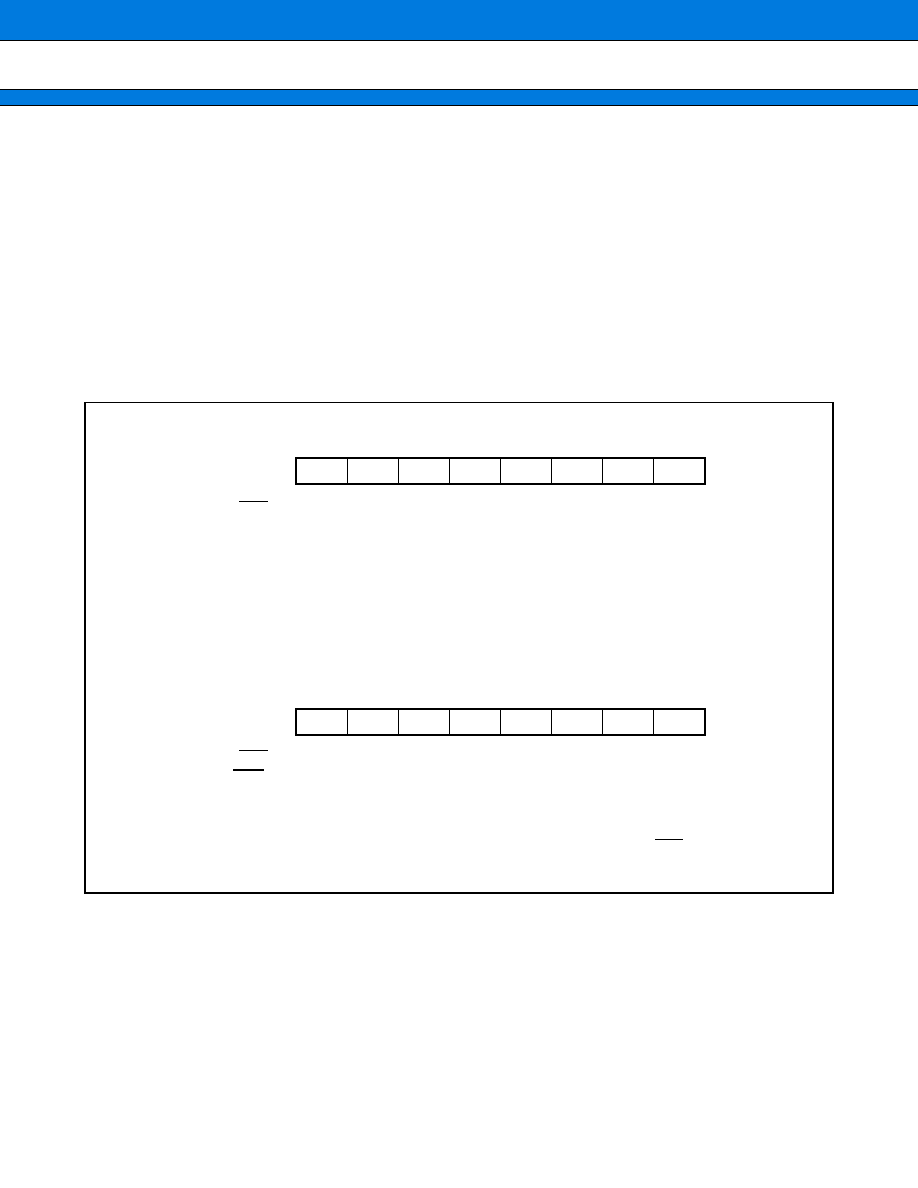

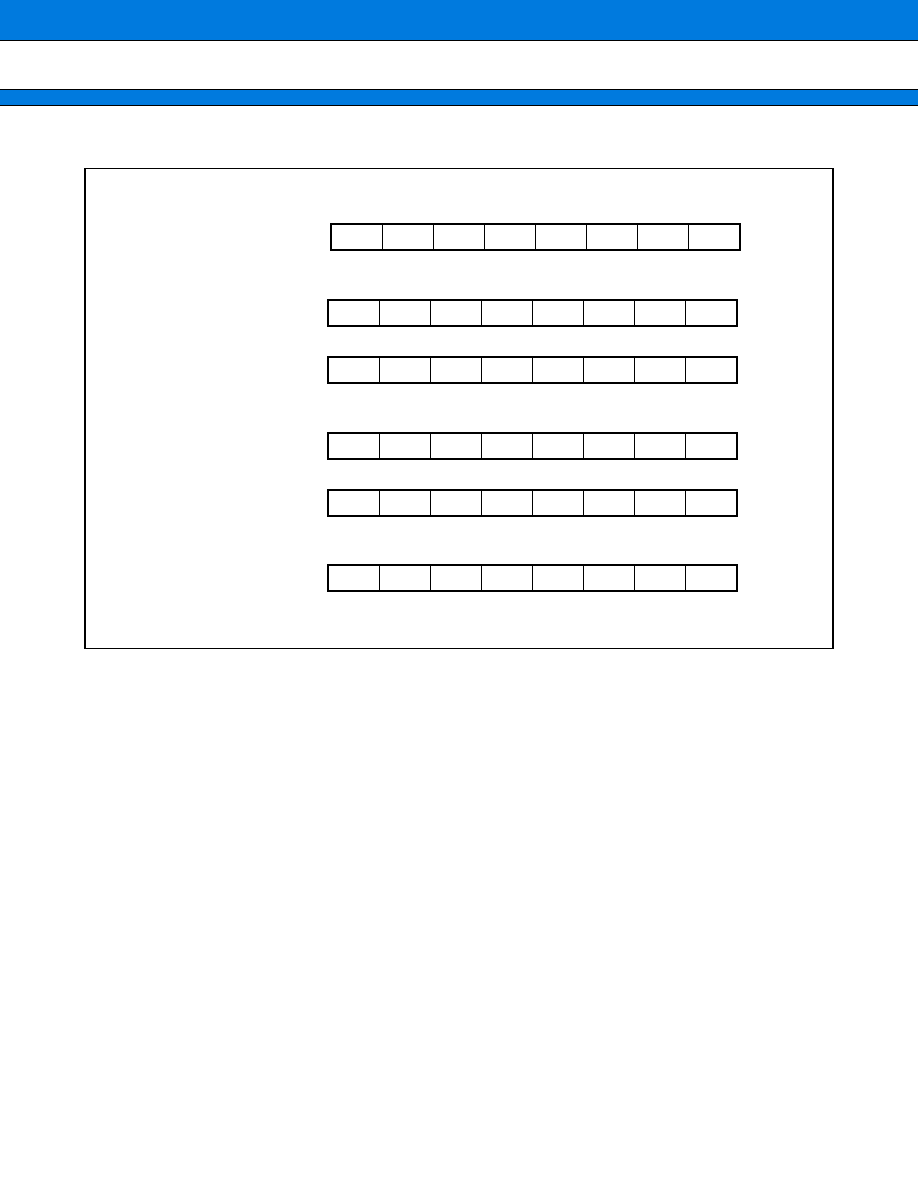

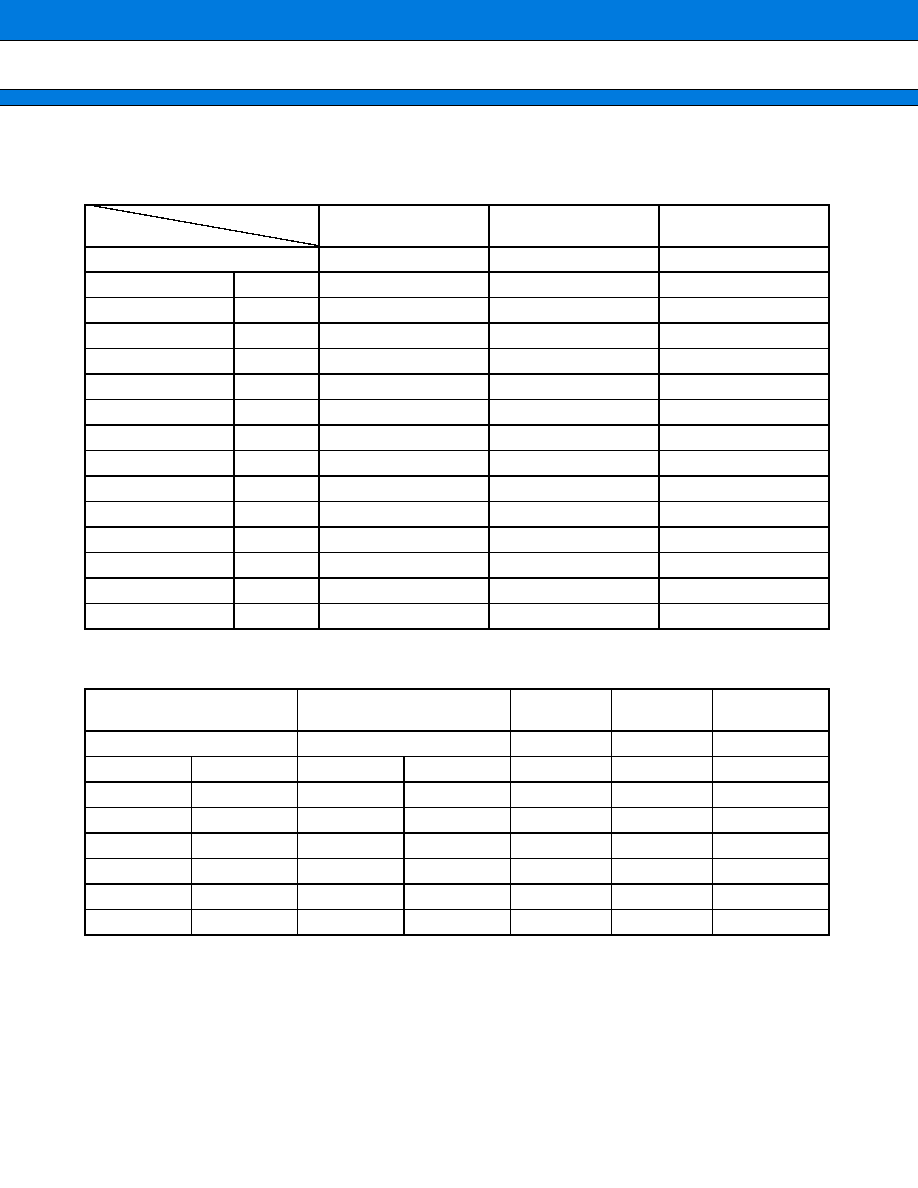

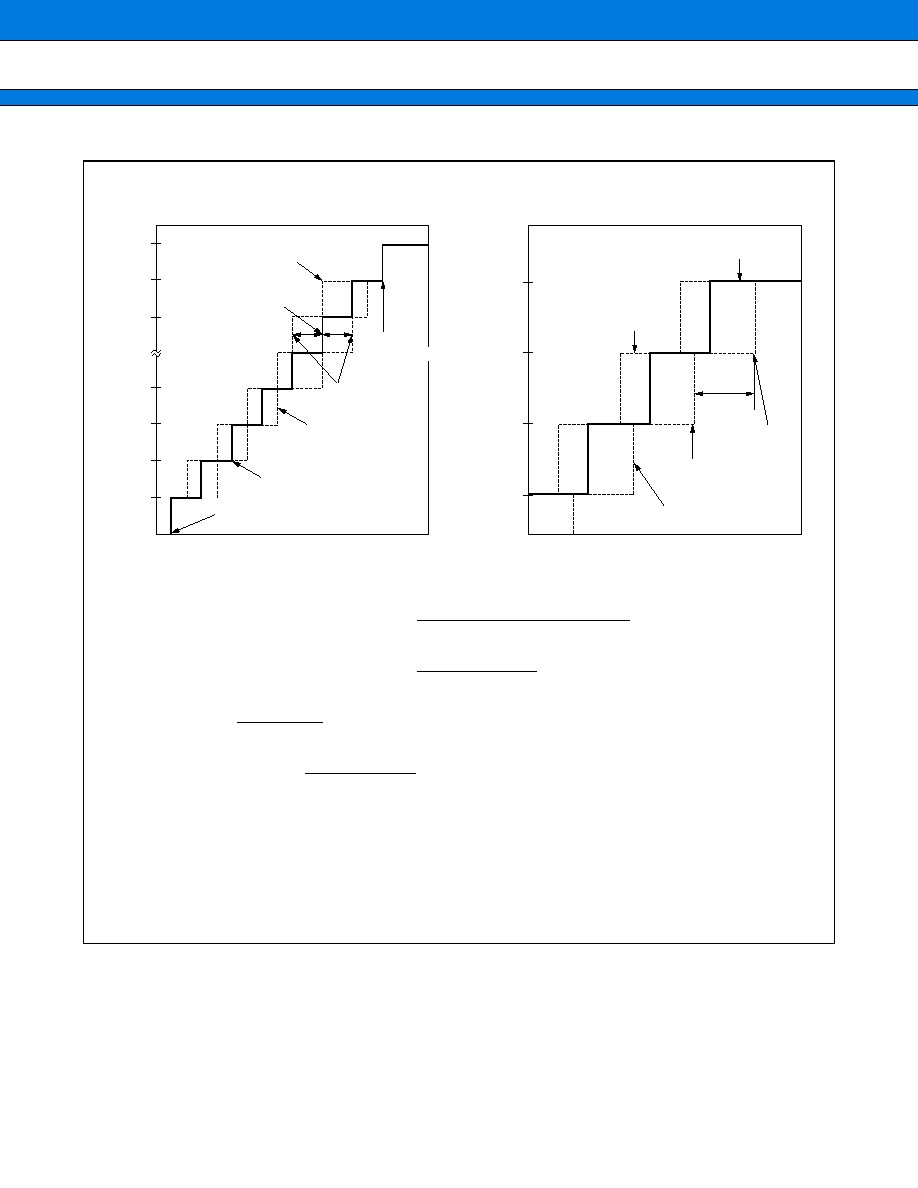

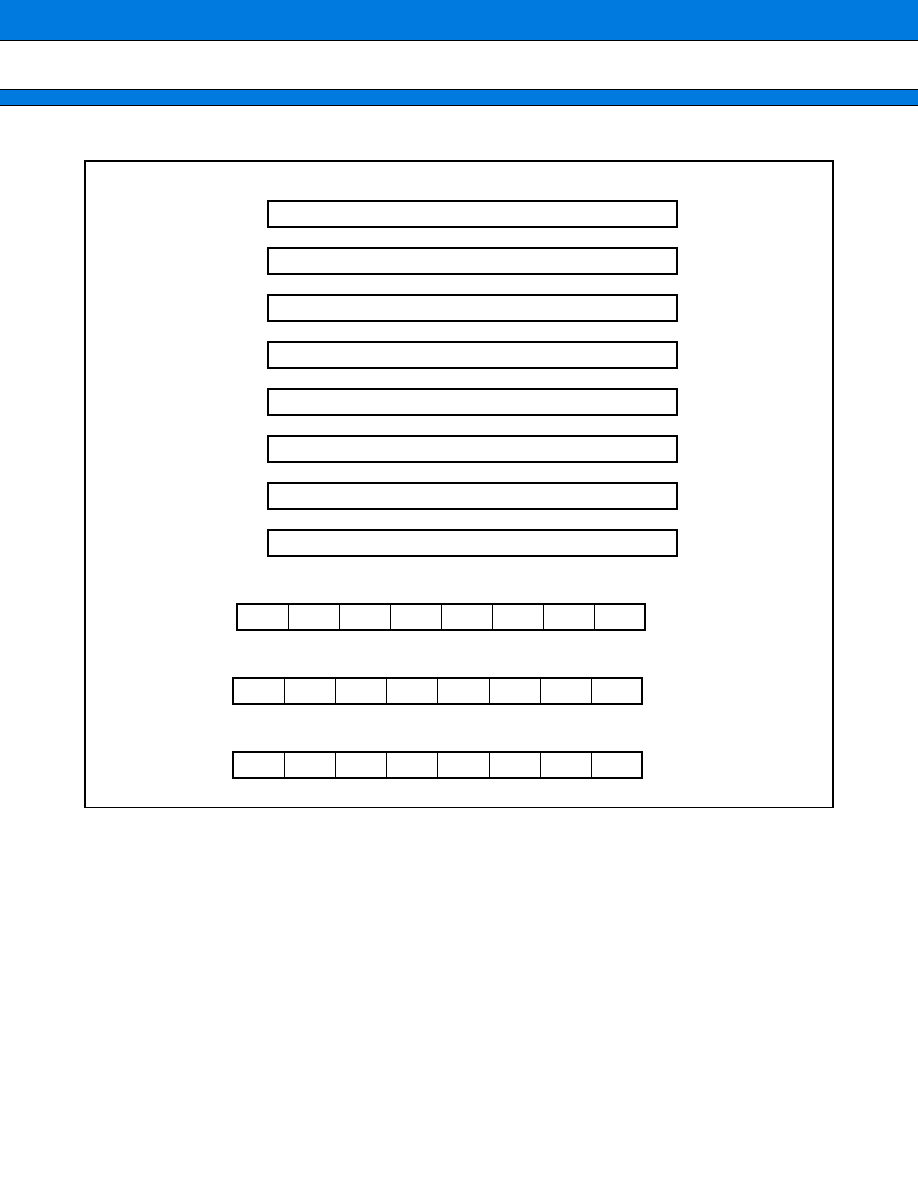

Dedicated Registers

Each of the dedicated registers is used for a particular purpose. The dedicated registers consist of the program

counter (PC) , program status (PS) , table base register (TBR) , return pointer (RP) , system stack pointer (SS

P) , user stack pointer (USP) , and multiplication and division result registers (MDH/MDL) .

(1) Program status (PS)

PC

PS

TBR

RP

SSP

USP

MDH

MDL

XXXX XXXX

H

(Indeterminate)

XXXX XXXX

H

(Indeterminate)

XXXX XXXX

H

(Indeterminate)

XXXX XXXX

H

(Indeterminate)

XXXX XXXX

H

(Indeterminate)

0000 0000

H

000F FC00

H

32 bits

Program counter

Program status

Table base register

Return pointer

System stack pointer

User stack pointer

Multiplication and division

results resisters

Initial value

31

Bit position

20

16

ILM

SCR

CCR

10

7

8

0

CCR : Condition Code Register

SCR : System Condition Code Register

ILM : Interrupt Level Mask

MB91360G Series

30

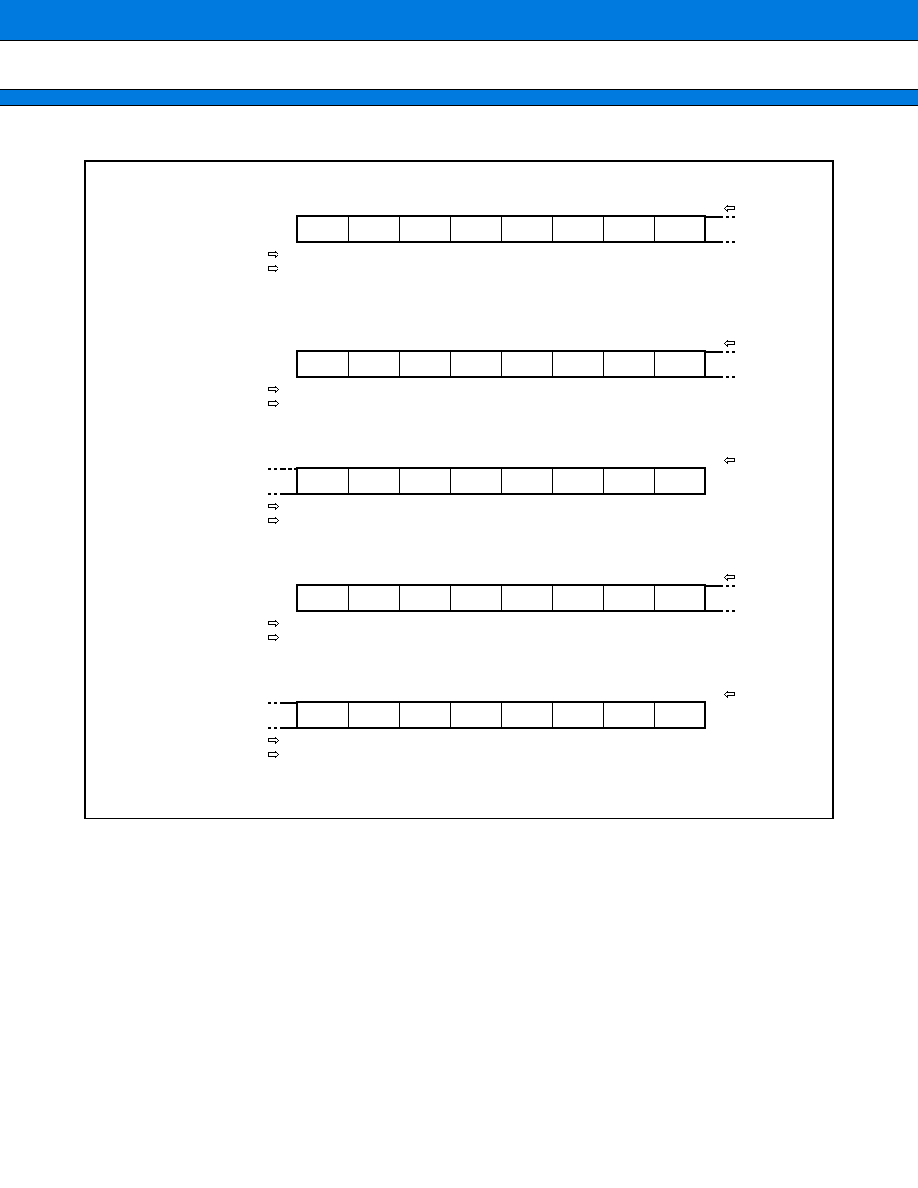

(2) Condition Code Register (CCR)

(3) System Condition Code Register (SCR)

(4) Interrupt Level Mask Register (ILM)

(Bit)

Initial value

--00XXXX

B

7

6

5

4

3

2

1

0

S

I

N

Z

V

C

(Bit)

Initial value

XX0

B

10

9

8

D1

D0

T

(Bit)

Initial value

01111

B

20

19

18

17

16

ILM4 ILM3 ILM2 ILM1 ILM0

MB91360G Series

31

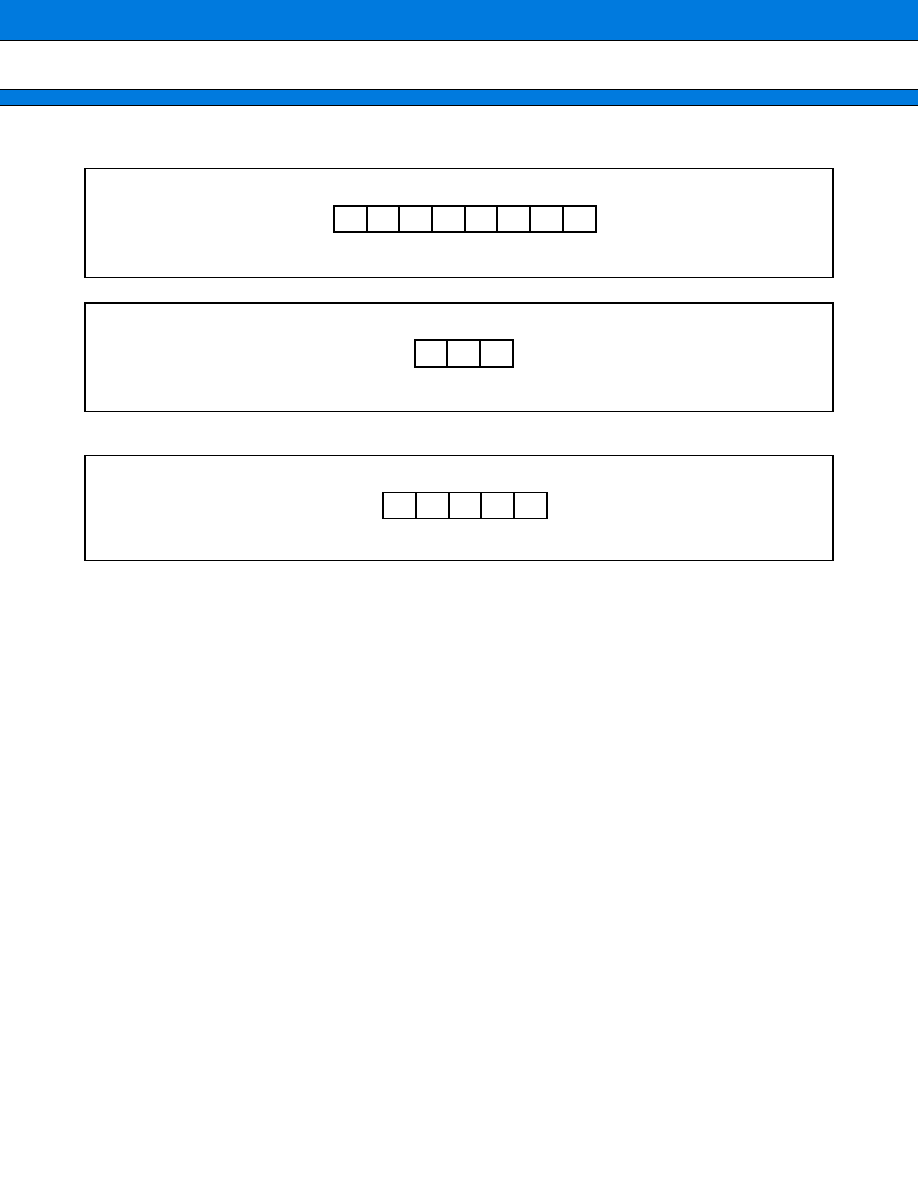

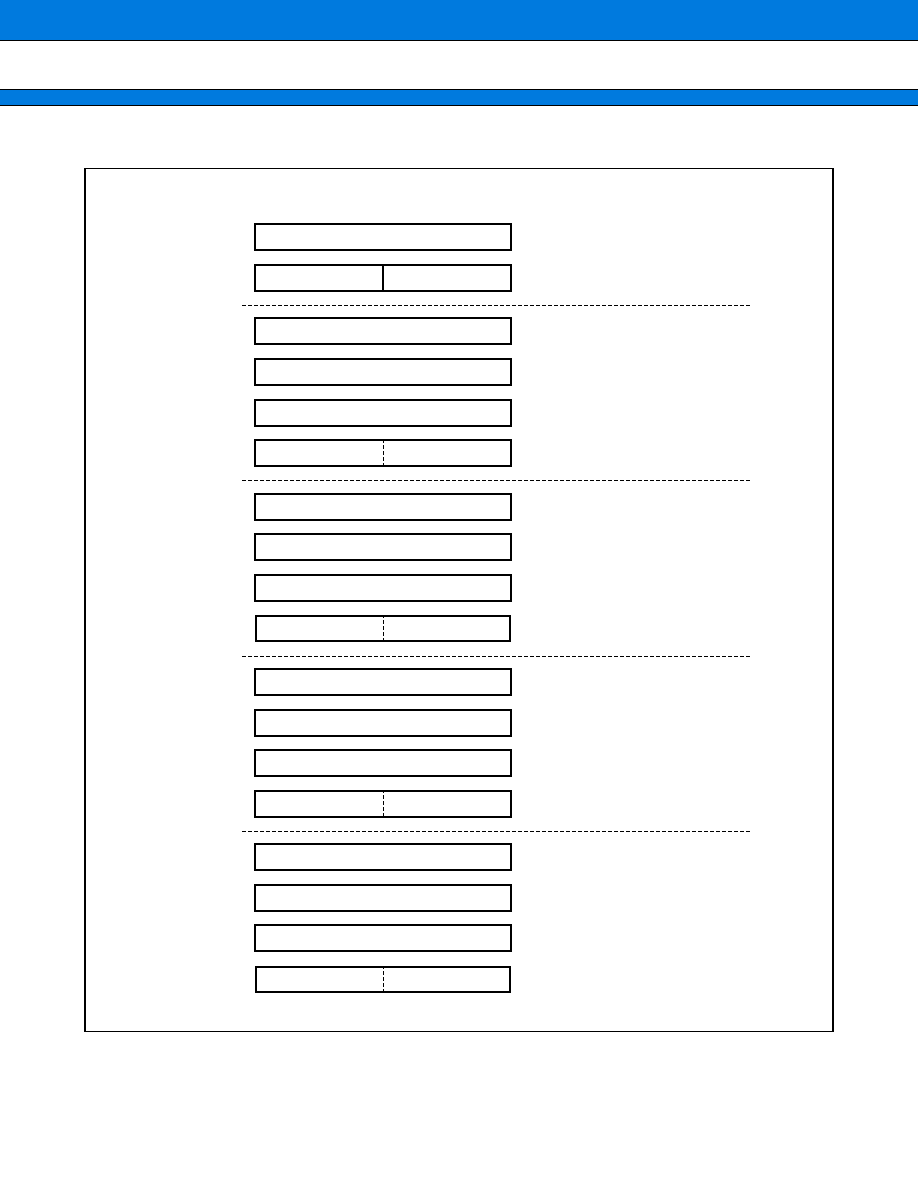

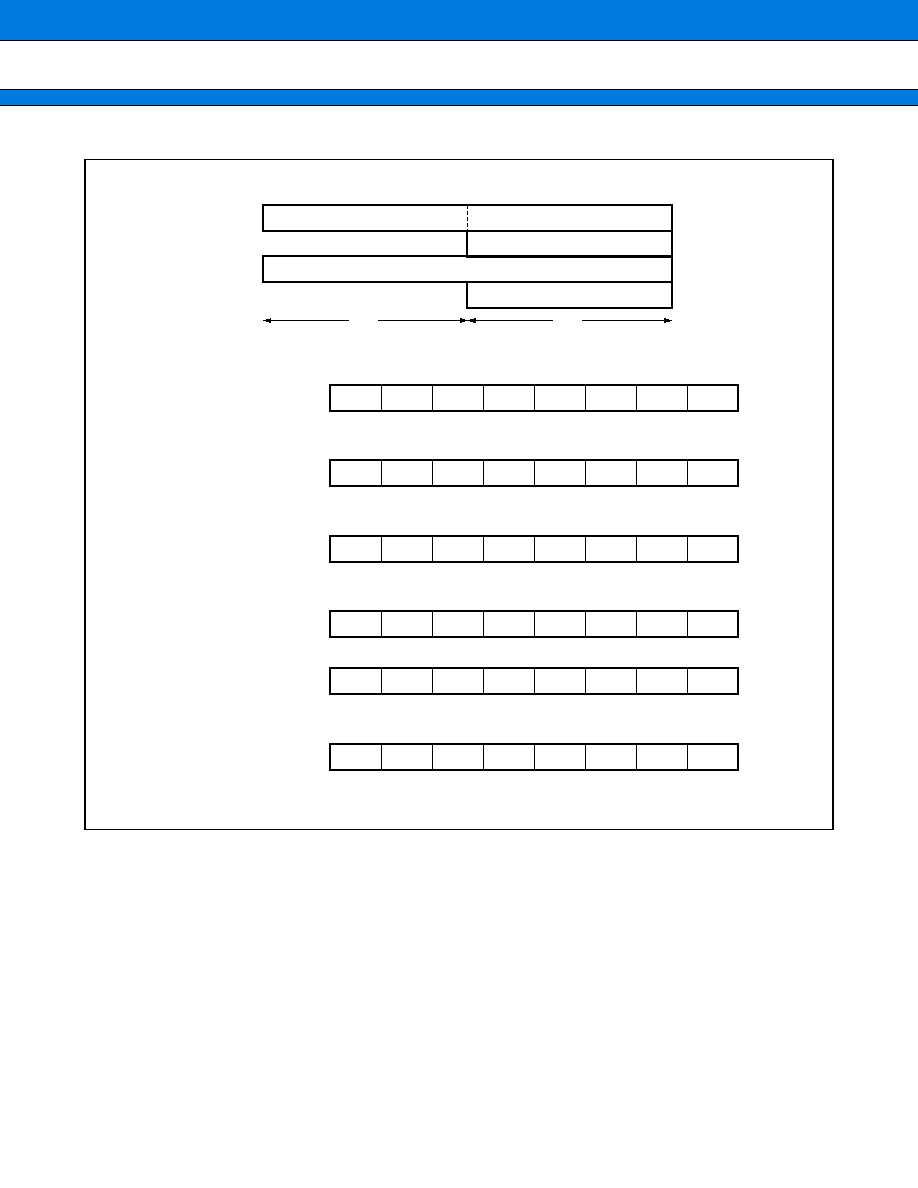

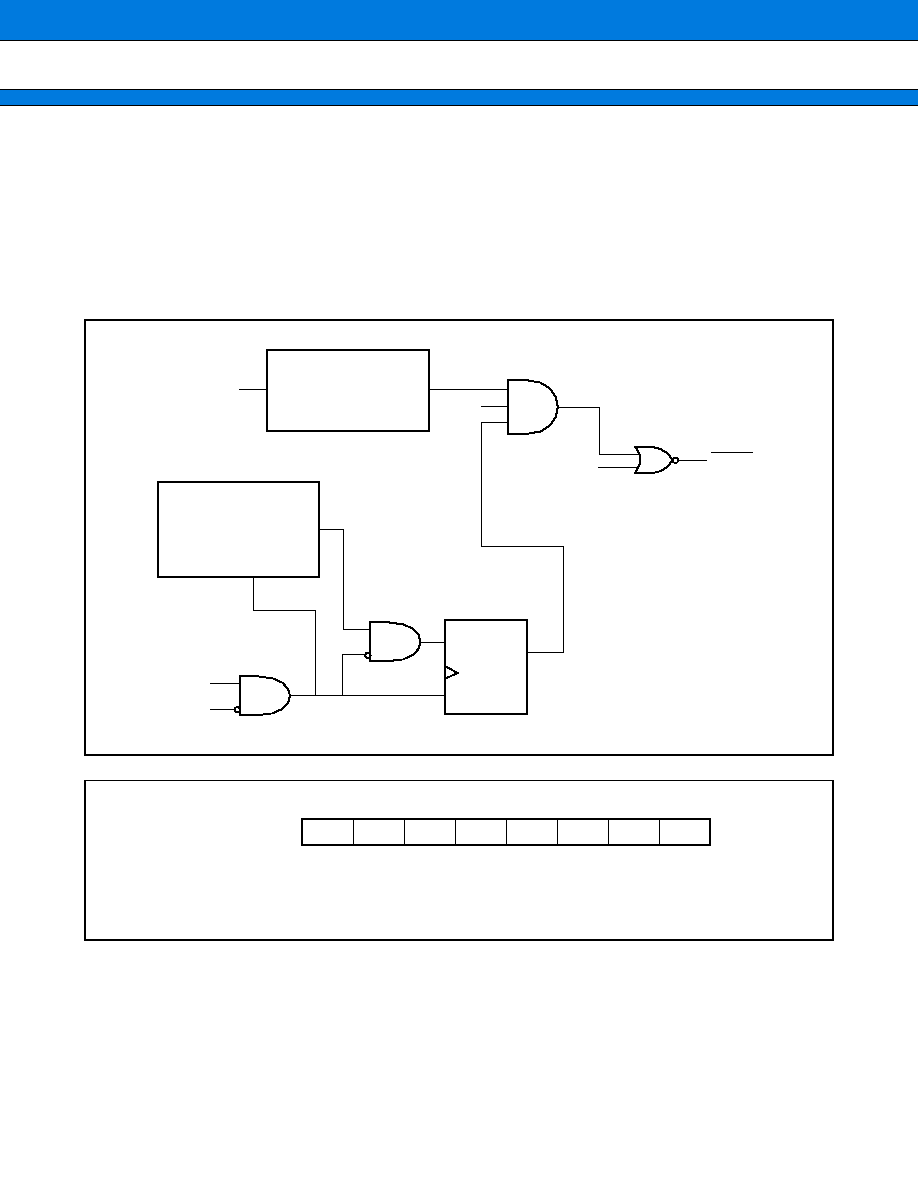

3.

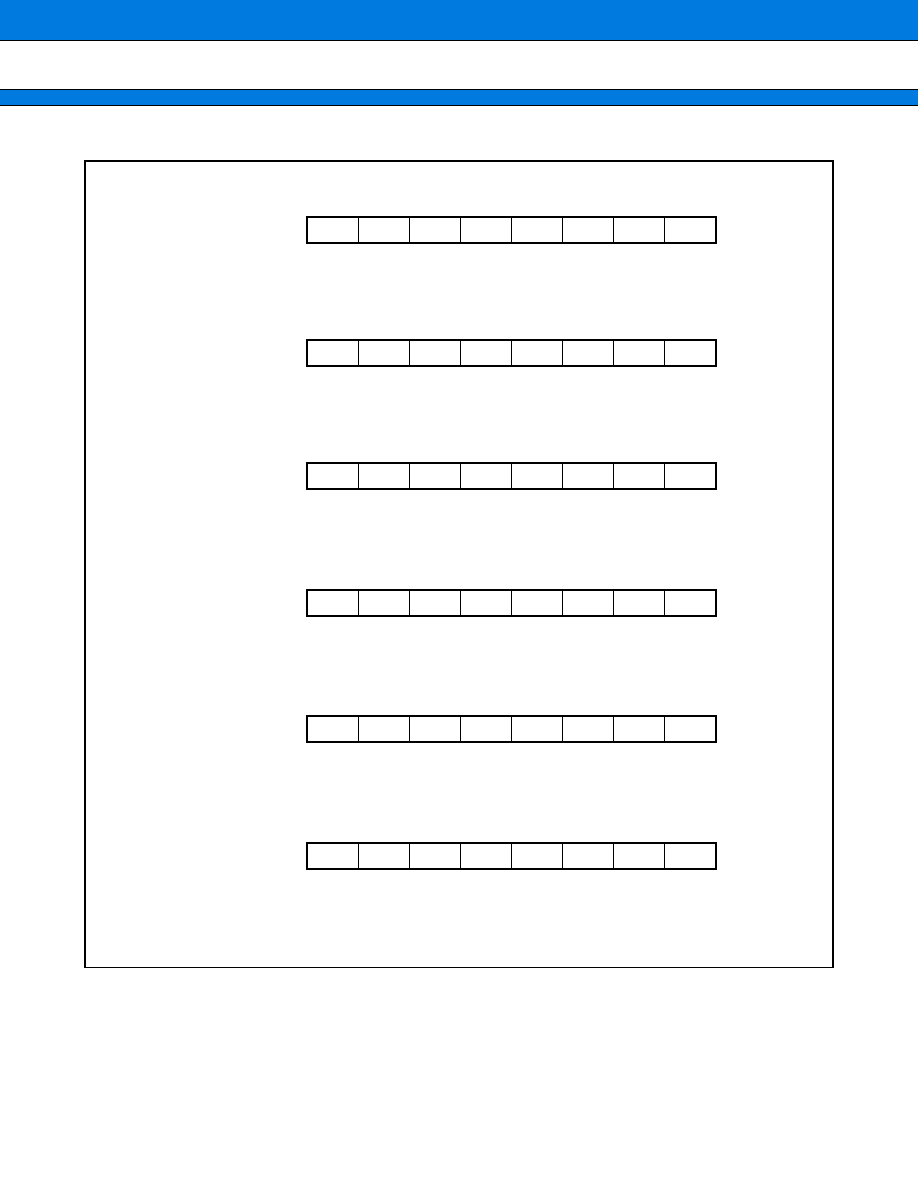

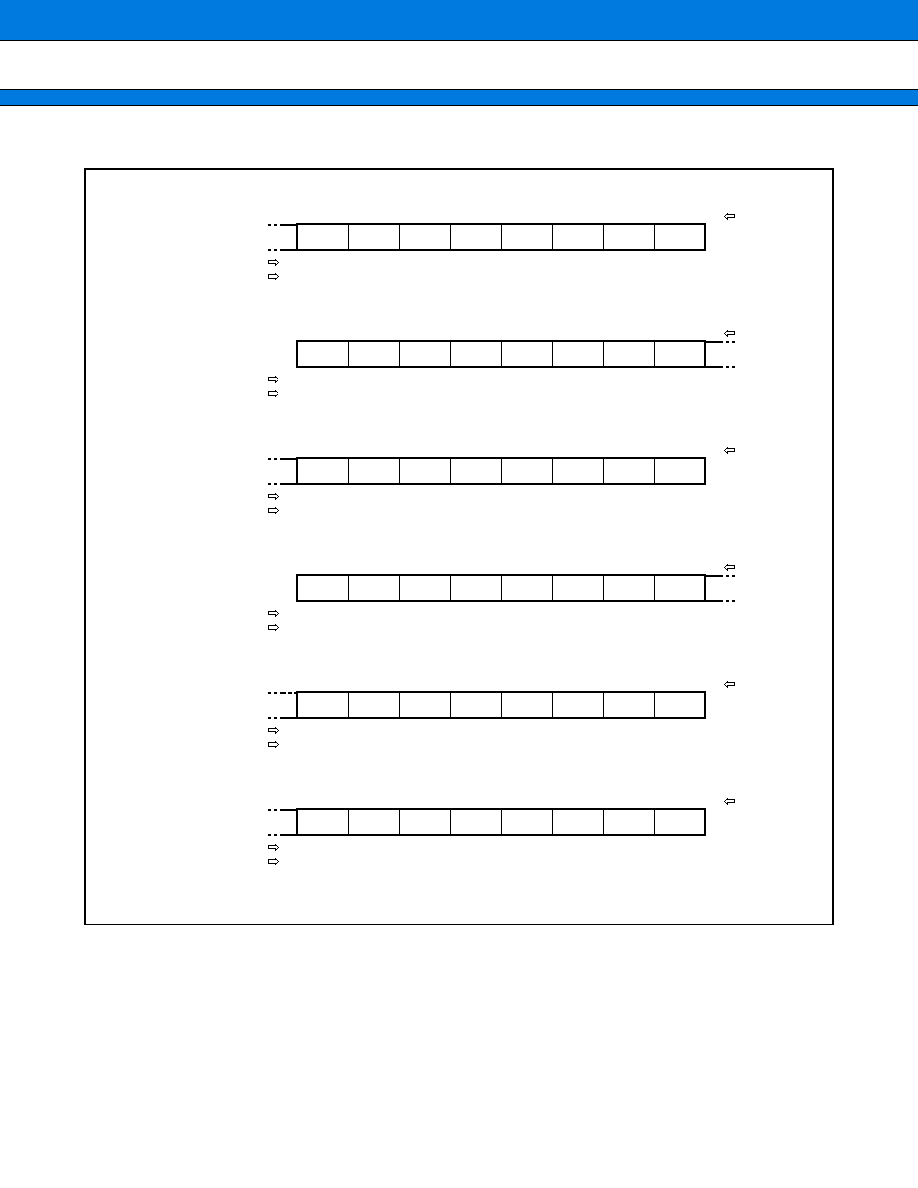

General-Purpose Registers

The general-purpose registers are CPU registers R0 to R15. The register are used as the accumulator for

operations and as pointers (a field indicating an address) for memory access. The user can specify the purpose

for which the general-purpose registers are used.

Among 16 general-purpose registers, the following registers assume a special purpose. This enhances some

instructions.

The initial value of R0 to R14 after a reset is indeterminate. The initial value of R15 is 00000000

H

(SSP value) .

R13

: Virtual accumulator (AC)

R14

: Frame pointer (FP)

R15

: Stack pointer (SP)

R0

R1

R12

R13

R14

R15

AC (Accumulator)

FP (Frame Pointer)

SP (Stack Pointer)

XXXX XXXX

H

XXXX XXXX

H

0000 0000

H

32-bits

Initial value

Register bank structure

MB91360G Series

32

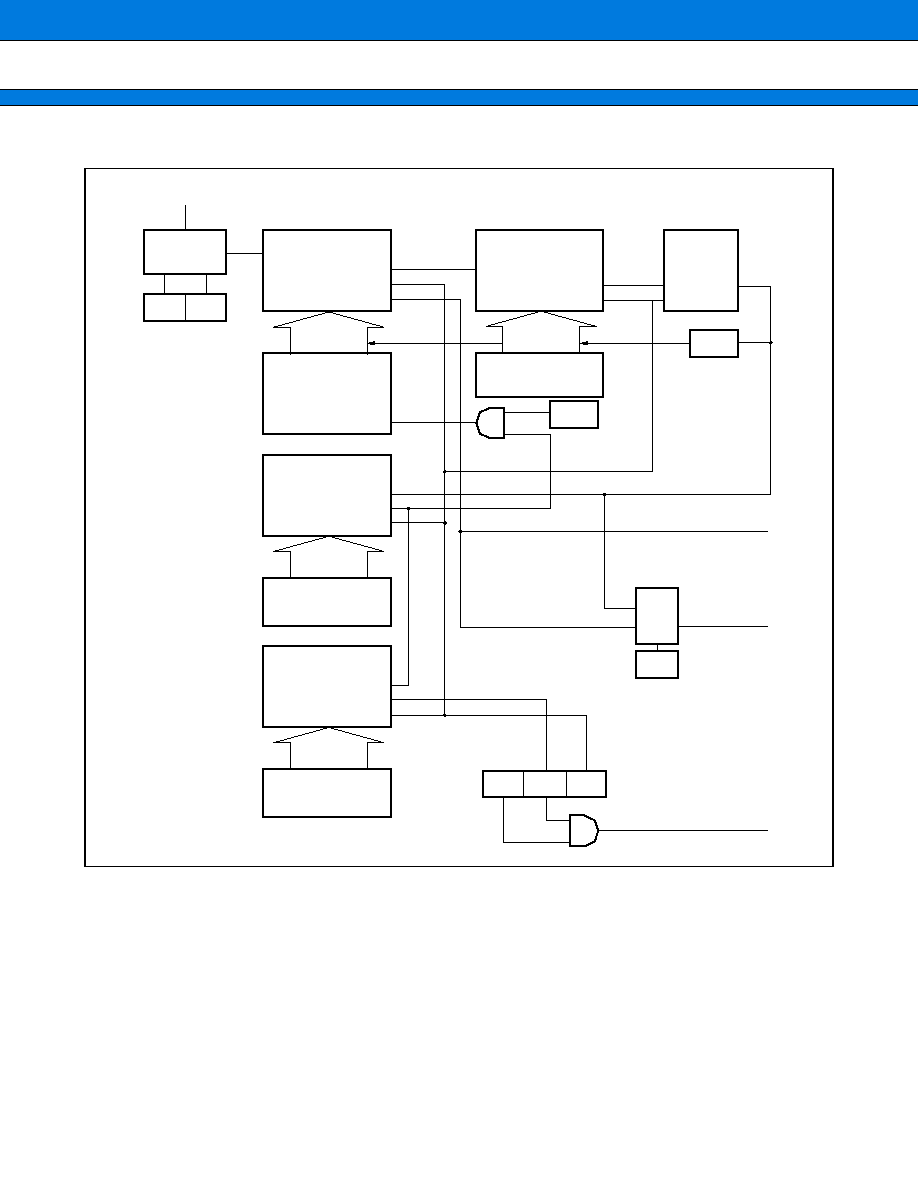

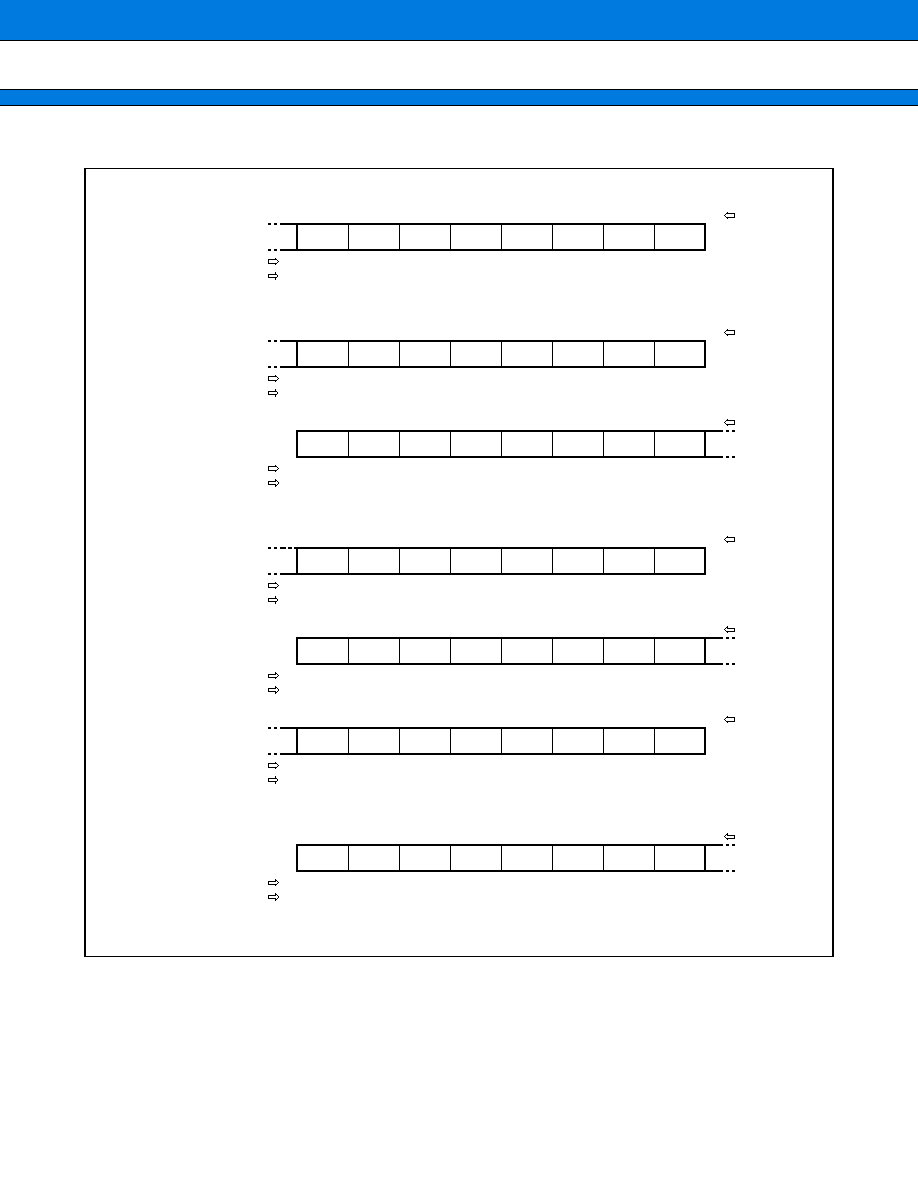

s

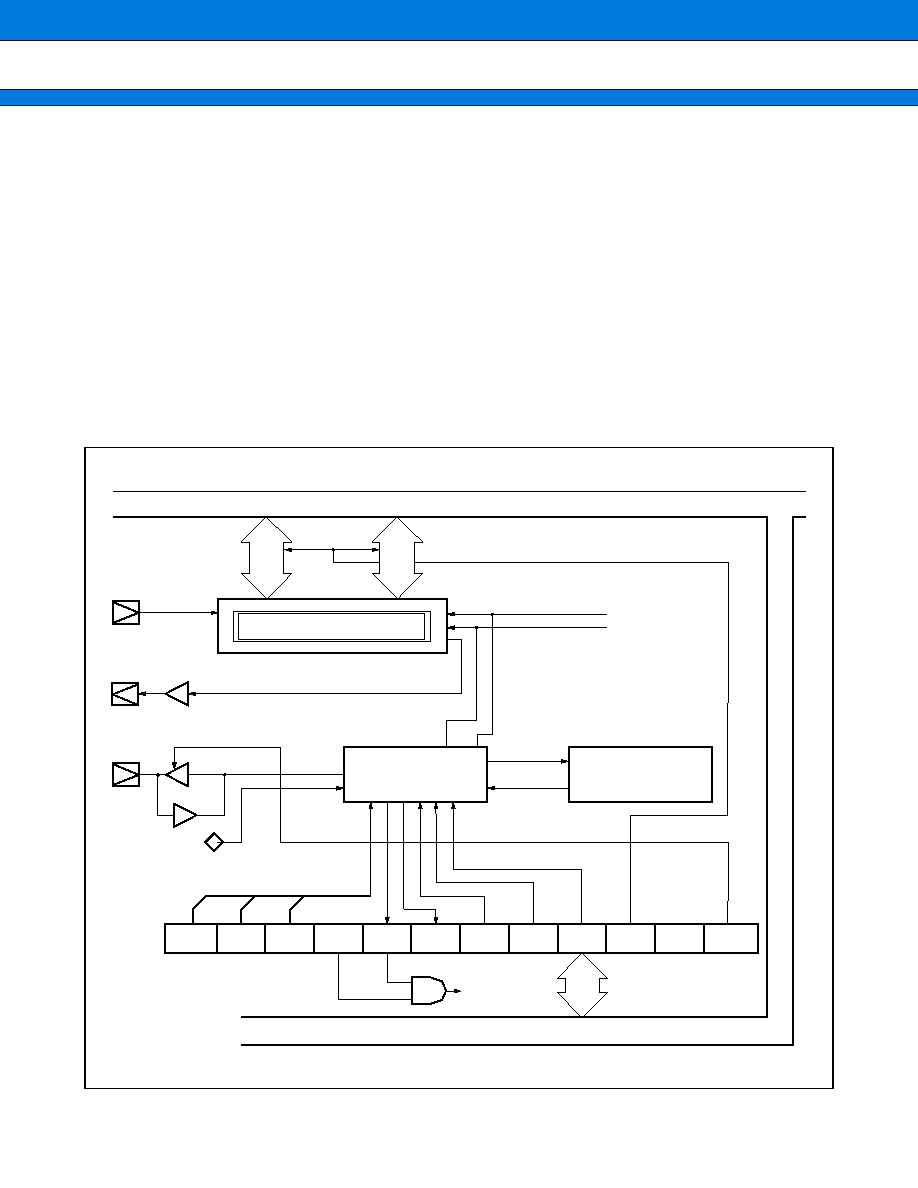

MODE SETTING

The FR50 series of devices uses mode pins (MD2 to MD0) and a mode register (MODR) to set the operation

mode.

(1) Mode Pins

Three mode pins (MD2 to MD0) are used to specify the reset mode vector access area.

(2) Mode Register (MODR)

The data to be written to 0000_7FDH using mode vector fetch is called mode data.

MODR is located at 0000_07FDH. After an operation mode has been set in MODR, the device operates in this

operation mode. MODR is set only when a reset factor (INIT level) occurs. User programs cannot write data to

MODR.

<

Mode Register (MODR)

>

[Bits 7 to 3] : (Reserved bits)

Always set 00000 at bits 7 to 3. Operation is not guaranteed when other values are set.

[Bit 2] : ROMA (internal ROM enable bit)

The ROMA bit is used to set whether to validate the internal ROM area (Fbus memory area) .

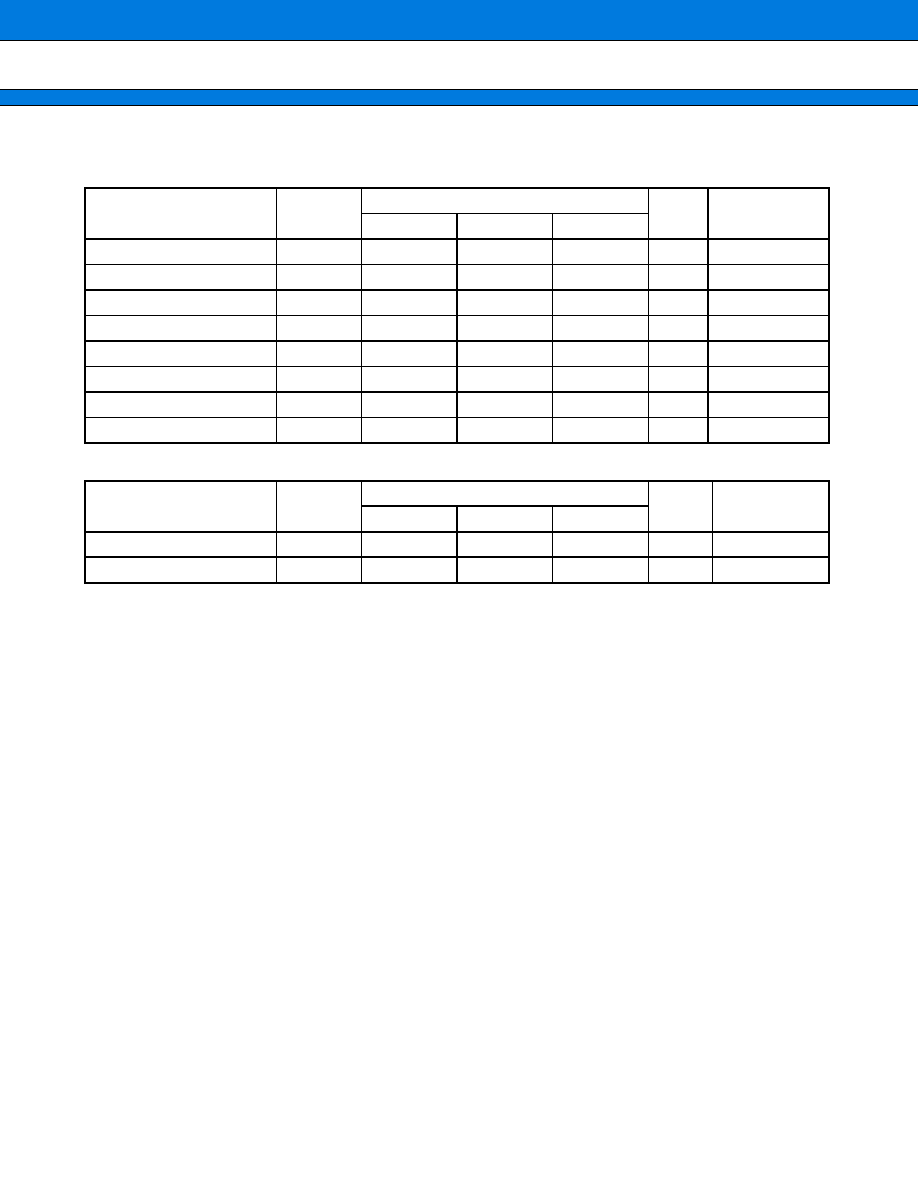

Mode Pins

Mode name

Reset vector

access area

Remarks

MD2

MD1

MD0

0

0

0

Internal ROM mode vector

Internal

0

0

1

External ROM mode vector

External

The mode register is used to set the bus

width.

remaining settings

Reserved

ROMA

Function

Remarks

0

External ROM mode

Access to the Fbus area is external.

1

Internal ROM mode

Address

Initial value

0000 07FD

H

XXXXXXXX

7

6

5

4

3

2

1

0

0

0

0

0

0

ROMA

WTH1

Operation mode setting bit

WTH0

MB91360G Series

33

[Bits 1 and 0] : WTH1 and WTH0 (bus width/single chip mode specifying bits)

The WTH1 and WTH0 bits are used to set the bus width (valid when operation mode is external bus mode) and

the single chip mode. When the operation mode is the external bus mode, this value is set at the BW1 and BW0

bits of AMD0 (CS0 area) .

(3) Fixed Vector

If MB91360 series devices are started in mode MD[2 : 0]

=

000, the internal fixed mode vector (FMV

=

0x06)

and the fixed reset vector are used. The fixed reset vector points to the start address of the internal Boot ROM.

This enables access to the F-bus area, to the internal CAN modules and the internal flash memory.

See also section Boot ROM.

WTH1

WTH0

Function

Remarks

0

0

8-bit bus width

External bus mode

0

1

16-bit bus width

External bus mode

1

0

32-bit bus width

External bus mode

1

1

Single chip mode

MB91360G Series

34

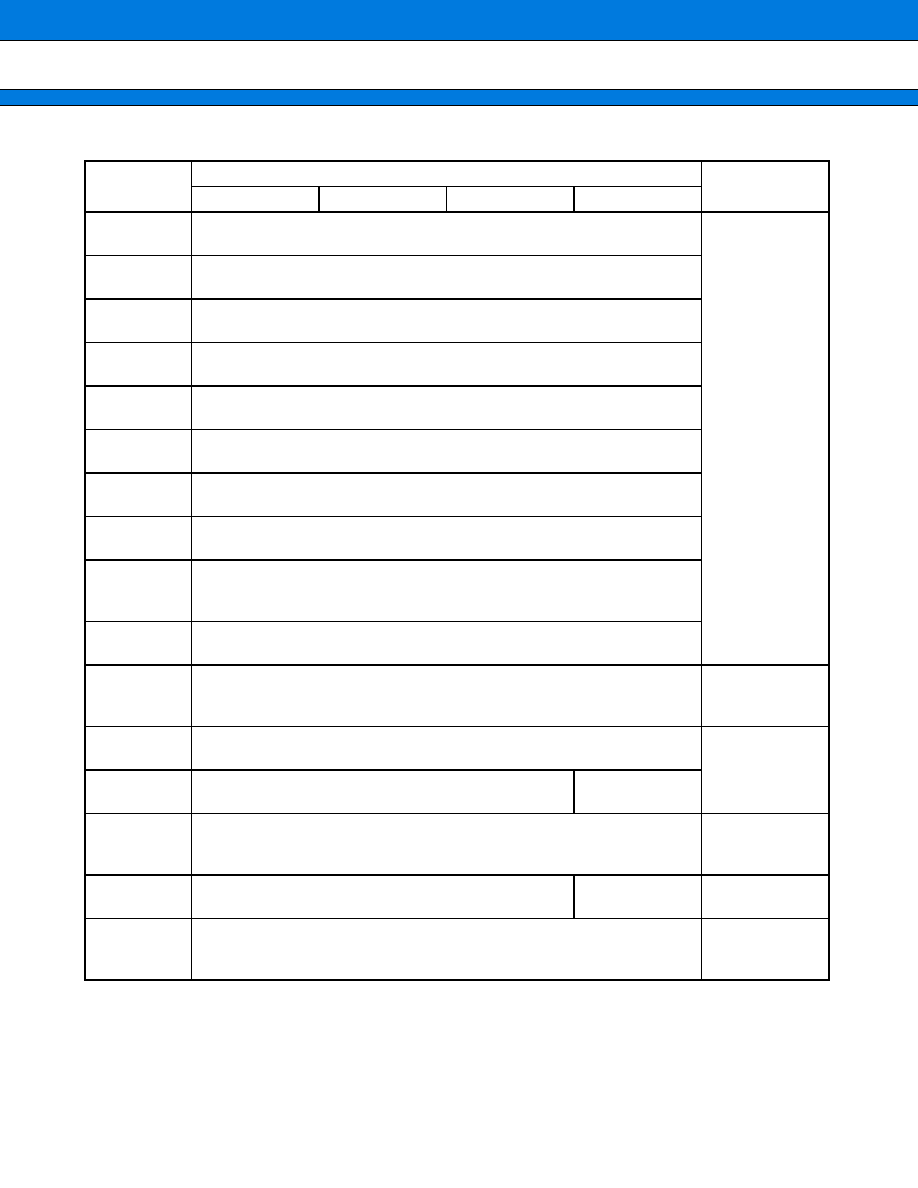

s

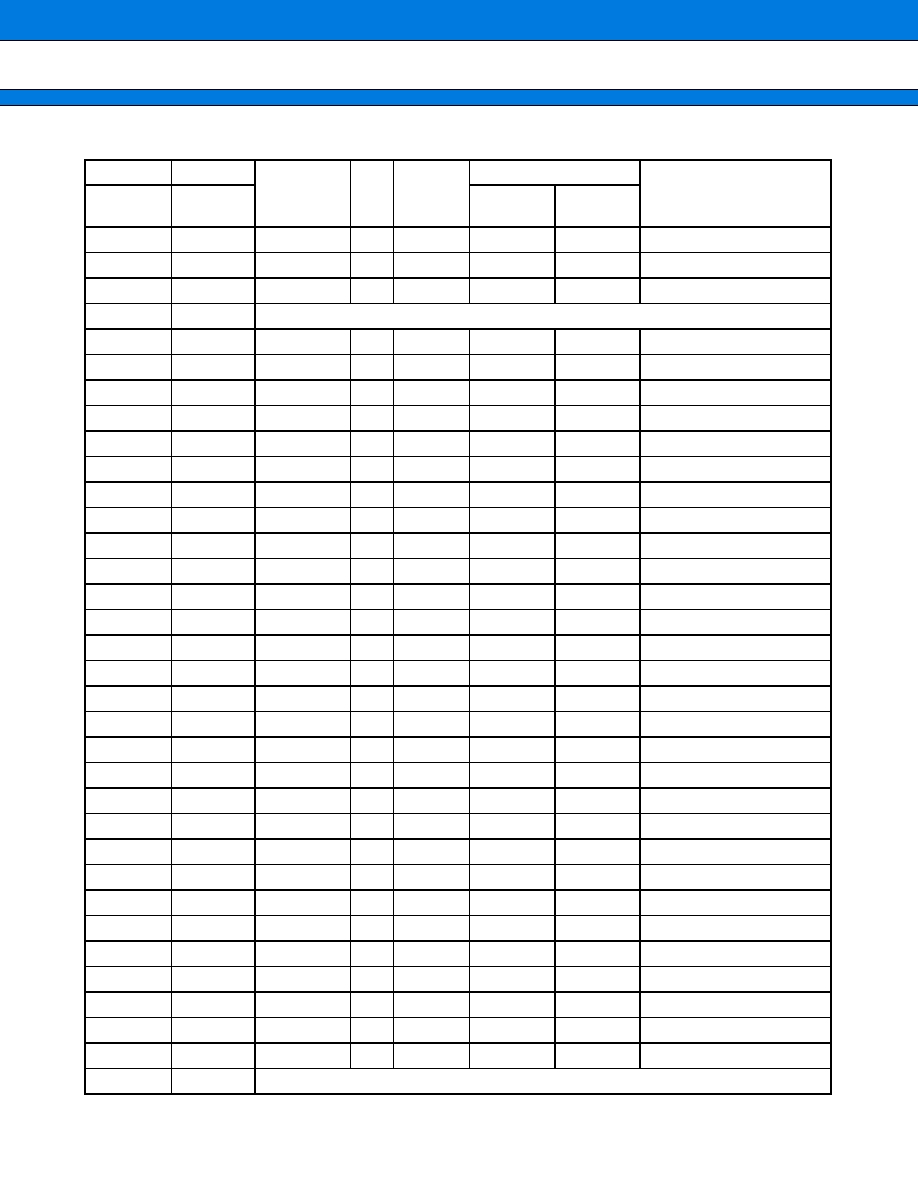

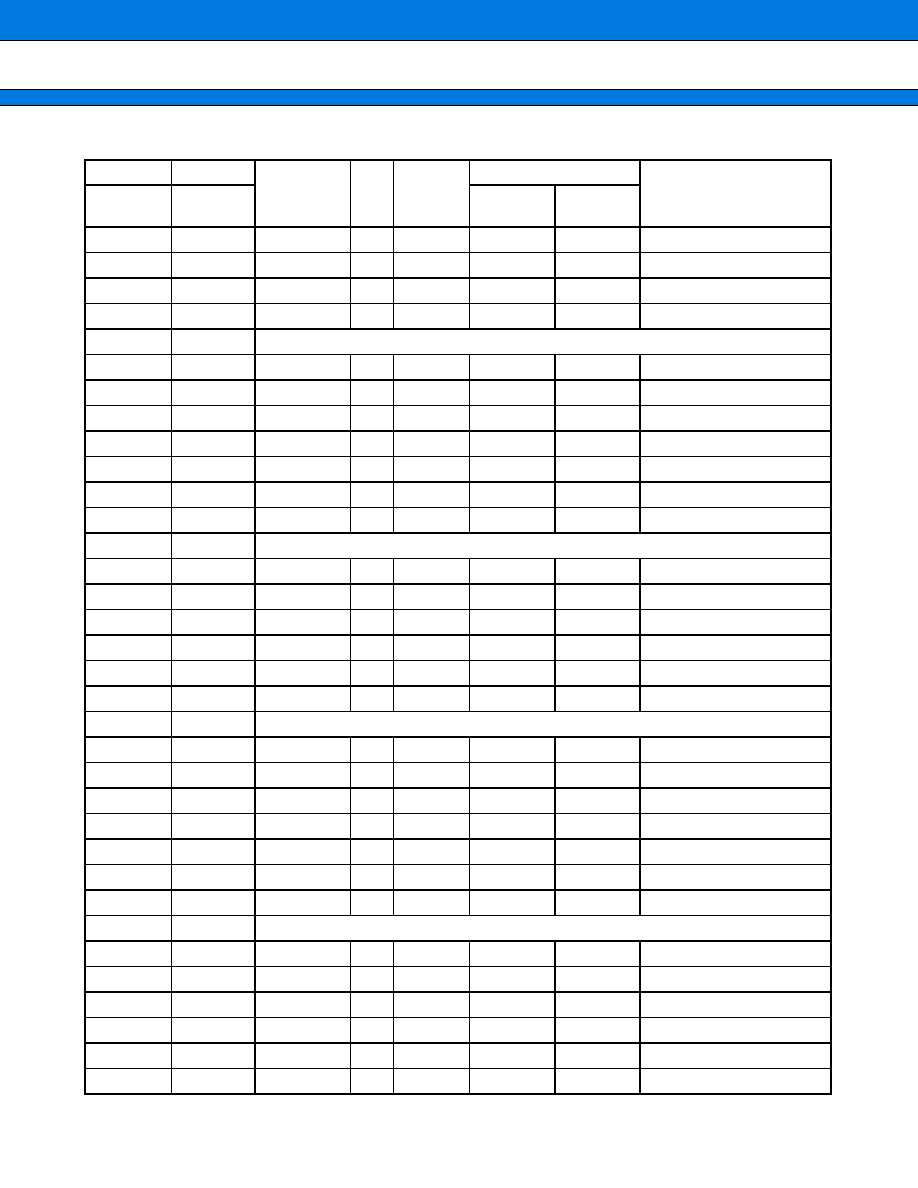

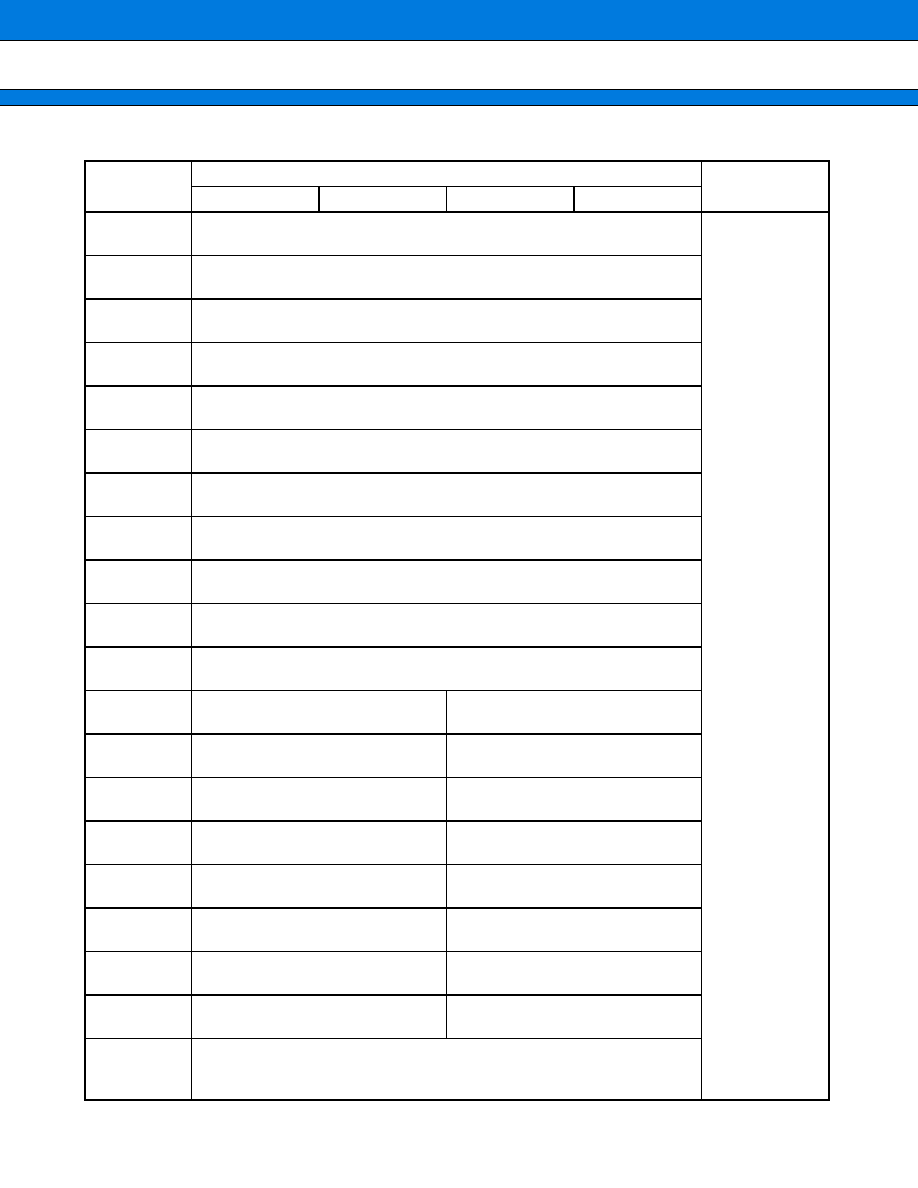

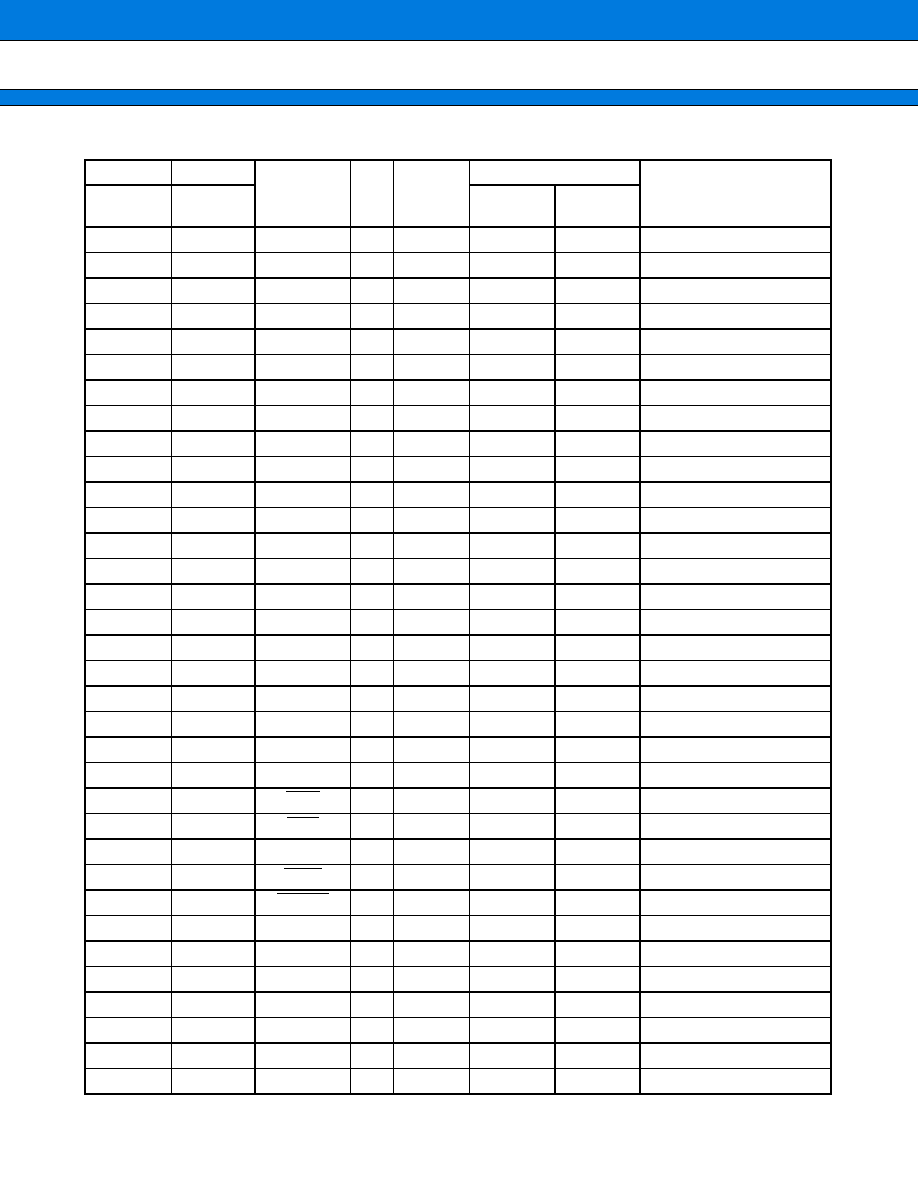

I/O MAP

(Continued)

Address

Register

Block

+

0

+

1

+

2

+

3

000000

H

reserved

reserved

reserved

reserved

T-unit

Port Data

Register

000004

H

reserved

reserved

reserved

PDR7 [R/W]

-111 - - - -

000008

H

PDR8 [R/W]

- - - - - XX -

PDR9 [R/W]

XXXXXXX1

PDRB [R/W]

- - - - - XXX

00000C

H

000010

H

PDRG [R/W]

XXXXXXXX

PDRH [R/W]

XXXXXXXX

PDRI [R/W]

X - - - X - - -

PDRJ [R/W]

XXXXXXXX

R-bus

Port Data

Register

000014

H

PDRK [R/W]

XXXXXXXX

PDRL [R/W]

XXXXXXXX

PDRM [R/W]

- - - - XXXX

PDRN [R/W]

- - XXXXXX

000018

H

PDRO [R/W]

XXXXXXXX

PDRP [R/W]

- - XXXXX

PDRQ [R/W]

- - XXXXX

PDRR [R/W]

XXXXXXXX

00001C

H

PDRS [R/W]

XXXXXXXX

000020

H

to

00003C

H

Reserved

000040

H

EIRR [R/W]

00000000

ENIR [R/W]

00000000

ELVR [R/W]

00000000 00000000

Ext int/NMI

000044

H

DICR [R/W]

- - - - - - - 0

HRCL [R/W]

0 - - 11111

CLKR2 [R/W]

- - - - - 000

reserved

DLYI/I-unit

RTC

000048

H

TMRLR0 [W]

XXXXXXXX XXXXXXXX

TMR0 [R]

XXXXXXXX XXXXXXXX

Reload Timer 0

00004C

H

TMCSR0 [R/W]

- - - - 0000 - - - 00000

000050

H

TMRLR1 [W]

XXXXXXXX XXXXXXXX

TMR1 [R]

XXXXXXXX XXXXXXXX

Reload Timer 1

000054

H

TMCSR1 [R/W]

- - - - 0000 - - - 00000

000058

H

TMRLR2 [W]

XXXXXXXX XXXXXXXX

TMR2 [R]

XXXXXXXX XXXXXXXX

Reload Timer 2

00005C

H

TMCSR2 [R/W]

- - - - 0000 - - - 00000

000060

H

SSR0 [R/W]

00001 - 00

SIDR0 [R/W]

XXXXXXXX

SCR0 [R/W]

00000100

SMR0 [R/W]

00 - - 0 - 0 -

UART0

000064

H

ULS0 [R/W]

- - - - 0000

MB91360G Series

35

(Continued)

(Continued)

Address

Register

Block

+

0

+

1

+

2

+

3

000068

H

UTIM0/UTIMR0 [R/W]

00000000 00000000

DRCL0 [W]

- - - - - - - -

UTIMC0 [R/W]

0 - - - 0 - 01

U-TIMER 0

00006C

H

SSR1 [R/W]

00001 - 00

SIDR1 [R/W]

XXXXXXXX

SCR1 [R/W]

00000100

SMR1 [R/W]

00 - - 0 - 0 -

UART1

000070

H

ULS1 [R/W]

- - - - 0000

000074

H

UTIM1/UTIMR1 [R/W]

00000000 00000000

DRCL1 [W]

- - - - - - - -

UTIMC1 [R/W]

0 - - - - - 01

U-TIMER 1

000078

H

SSR2 [R/W]

00001 - 00

SIDR2 [R/W]

XXXXXXXX

SCR2 [R/W]

00000100

SMR2 [R/W]

00 - - 0 - 0 -

UART2

00007C

H

ULS2 [R/W]

- - - - 0000

000080

H

UTIM2/UTIMR2 [R/W]

00000000 00000000

DRCL2 [W]

- - - - - - - -

UTIMC2 [R/W]

0 - - - 0 - 01

U-TIMER2

000084

H

SMCS0 [R/W]

00000010 - - - - 00-0

SES0 [R/W]

- - - - - - 00

SDR0 [R/W]

00000000

SIO 0

000088

H

SMCS1 [R/W]

00000010 - - - - 00 - 0

SES1 [R/W]

- - - - - - 00

SDR1 [R/W]

00000000

SIO 1

00008C

H

CDCR0 [R/W]

0 - - - 1111

Reserved

CDCR1 [R/W]

0 - - - 1111

Reserved

SIO 0/1

Prescaler

000090

H

Reserved

000094

H

IBCR [R/W]

00000000

IBSR [R]

00000000

IADR [R/W]

-XXXXXXX

ICCR [R/W]

- - 0XXXXX

I

2

C (old)

new I

2

C

from addr 0x184

000098

H

IDAR [R/W]

XXXXXXXX

IDBL [R/W]

- - - - - - - 0

00009C

H

ADMD [R/W, W]

- - - X0000

ADCH [R/W]

00000000

ADCS [R/W, W]

0000 - - 00

A/D Converter

0000A0

H

ADCD [R/W]

000000XX XXXXXXXX

ADBL [R/W]

- - - - - - - 0

0000A4

H

DACR [R/W]

- - - - - 000

DADR0 [R/W]

- - - - - - XX XXXXXXXX

DAC

0000A8

H

DADR1 [R/W]

- - - - - - XX XXXXXXXX

DDBL [R/W]

- - - - - - - 0

0000AC

H

IOTDBL0 [R/W]

- - - - - 000

ICS01 [R/W]

00000000

IOTDBL1 [R/W]

- - - - - 000

ICS23 [R/W]

00000000

Input Capture

0, 1, 2, 3

0000B0

H

IPCP0 [R]

XXXXXXXX XXXXXXXX

IPCP1 [R]

XXXXXXXX XXXXXXXX

0000B4

H

IPCP2 [R]

XXXXXXXX XXXXXXXX

IPCP3 [R]

XXXXXXXX XXXXXXXX

MB91360G Series

36

(Continued)

(Continued)

Address

Register

Block

+

0

+

1

+

2

+

3

0000B8

H

OCS0/1 [R/W]

- - - 0 - - 00 0000 - - 00

reserved

Output Compare

0, 1, 2.3

0000BC

H

OCCP0 [R/W]

XXXXXXXX XXXXXXXX

OCCP1 [R/W]

XXXXXXXX XXXXXXXX

0000C0

H

OCCP2 [R/W]

XXXXXXXX XXXXXXXX

OCCP3 [R/W]

XXXXXXXX XXXXXXXX

0000C4

H

Reserved

0000C8

H

TCDT0 [R/W]

XXXXXXXX XXXXXXXX

TCCS0 [R/W]

- 0000000

Free Running

Counter 0 for

ICU/OCU

0000CC

H

TCDT1 [R/W]

XXXXXXXX XXXXXXXX

TCCS1 [R/W]

- 0000000

Free Running

Counter 1 for

ICU/OCU

0000D0

H

ZPD0 [R/W]

00000010

PWC0 [R/W]

- - 000 - - 0

ZPD1 [R/W]

00000010

PWC1 [R/W]

00000 - - 0

SMC 0, 1

0000D4

H

ZPD2 [R/W]

00000010

PWC2 [R/W]

- - 000 - - 0

ZPD3 [R/W]

00000010

PWC3 [R/W]

00000 - - 0

SMC 2, 3

0000D8

H

PWC20 [R/W]

XXXXXXXX

PWC10 [R/W]

XXXXXXXX

PWS20 [R/W]

- 0000000

PWS10 [R/W]

- - 000000

SMC 0

0000DC

H

PWC21 [R/W]

XXXXXXXX

PWC11 [R/W]

XXXXXXXX

PWS21 [R/W]

- 0000000

PWS11 [R/W]

- - 000000

SMC 1

0000E0

H

PWC22 [R/W]

XXXXXXXX

PWC12 [R/W]

XXXXXXXX

PWS22 [R/W]

- 0000000

PWS12 [R/W]

- - 000000

SMC 2

0000E4

H

PWC23 [R/W]

XXXXXXXX

PWC13 [R/W]

XXXXXXXX

PWS23 [R/W]

- 0000000

PWS13 [R/W]

- - 000000

SMC 3

0000E8

H

SMDBL0 [R/W]

- - - - - - - 0

SMDBL1 [R/W]

- - - - - - 0

SMDBL2 [R/W]

- - - - - - - 0

SMDBL3 [R/W]

- - - - - - - 0

SMC 0, 1, 2, 3

0000EC

H

SGDBL [R/W]

- - - - - - - 0

SGCR [R, R/W]

0 - - - - - 00 000 - - 000

Sound

generator

0000F0

H

SGAR [R/W]

00000000

SGFR [R/W]

XXXXXXXX

SGTR [R/W]

XXXXXXXX

SGDR [R/W]

XXXXXXXX

0000F4

H

WTDBL [R/W]

- - - - - - - 0

WTCR [R, R/W]

00000000 000 - 0000

Real Time Clock

(WatchTimer)

0000F8

H

WTBR [R/W]

- - XXXXXX XXXXXXXX XXXXXXXX

0000FC

H

WTHR [R/W]

- - - 00000

WTMR [R/W]

- - 000000

WTSR [R/W]

- - 000000

000100

H

TMRLR3 [W]

XXXXXXXX XXXXXXXX

TMR3 [R]

XXXXXXXX XXXXXXXX

Reload Timer 3

000104

H

TMCSR3 [R/W]

- - - - XX - - - - - XXXXX

MB91360G Series

37

(Continued)

(Continued)

Address

Register

Block

+

0

+

1

+

2

+

3

000108

H

TMRLR4 [W]

XXXXXXXX XXXXXXXX

TMR4 [R]

XXXXXXXX XXXXXXXX

Reload Timer 4

00010C

H

TMCSR4 [R/W]

- - - - XX - - - - - XXXXX

000110

H

TMRLR5 [W]

XXXXXXXX XXXXXXXX

TMR5 [R]

XXXXXXXX XXXXXXXX

Reload Timer 5

000114

H

TMCSR5 [R/W]

- - - - XX - - - - - XXXXX

000118

H

GCN10 [R/W]

00110010 00010000

PDBL0 [R/W]

- - - 00000

GCN20 [R/W]

- - - - 0000

PWM Control 0

00011C

H

GCN11 [R/W]

00110010 00010000

PDBL1 [R/W]

- - - 00000

GCN21 [R/W]

- - - - 0000

PWM Control 1

000120

H

PTMR0 [R]

11111111 11111111

PCSR0 [W]

XXXXXXXX XXXXXXXX

PWM0

000124

H

PDUT0 [W]

XXXXXXXX XXXXXXXX

PCNH0 [R/W]

0000000 -

PCNL0 [R/W]

000000 - 0

000128

H

PTMR1 [R]

11111111 11111111

PCSR1 [W]

XXXXXXXX XXXXXXXX

PWM1

00012C

H

PDUT1 [W]

XXXXXXXX XXXXXXXX

PCNH1 [R/W]

0000000 -

PCNL1 [R/W]

000000 - 0

000130

H

PTMR2 [R]

11111111 11111111

PCSR2 [W]

XXXXXXXX XXXXXXXX

PWM2

000134

H

PDUT2 [W]

XXXXXXXX XXXXXXXX

PCNH2 [R/W]

0000000 -

PCNL2 [R/W]

000000 - 0

000138

H

PTMR3 [R]

11111111 11111111

PCSR3 [W]

XXXXXXXX XXXXXXXX

PWM3

00013C

H

PDUT3 [W]

XXXXXXXX XXXXXXXX

PCNH3 [R/W]

0000000 -

PCNL3 [R/W]

000000 - 0

000140

H

PTMR4 [R]

11111111 11111111

PCSR4 [W]

XXXXXXXX XXXXXXXX

PWM4

000144

H

PDUT4 [W]

XXXXXXXX XXXXXXXX

PCNH4 [R/W]

0000000 -

PCNL4 [R/W]

000000 - 0

000148

H

PTMR5 [R]

11111111 11111111

PCSR5 [W]

XXXXXXXX XXXXXXXX

PWM5

00014C

H

PDUT5 [W]

XXXXXXXX XXXXXXXX

PCNH5 [R/W]

0000000 -

PCNL5 [R/W]

000000 - 0

000150

H

PTMR6 [R]

11111111 11111111

PCSR6 [W]

XXXXXXXX XXXXXXXX

PWM6

000154

H

PDUT 6 [W]

XXXXXXXX XXXXXXXX

PCNH6 [R/W]

0000000 -

PCNL6 [R/W]

000000 - 0

MB91360G Series

38

(Continued)

* : Old and new I

2

C share this bit.

(Continued)

Address

Register

Block

+

0

+

1

+

2

+

3

000158

H

PTMR7 [R]

11111111 11111111

PCSR7 [W]

XXXXXXXX XXXXXXXX

PWM7

00015C

H

PDUT7 [W]

XXXXXXXX XXXXXXXX

PCNH7 [R/W]

0000000 -

PCNL7 [R/W]

000000 - 0

000160

H

Reserved

000164

H

CMCR [R/W]

11111111 0000000

CMPR [R/W]

- - - -1001 1 - - -0001

Clock Modulation

000168

H

CMLS0 [R/W]

01110111 1111111

CMLS1 [R/W]

01110111 1111111

00016C

H

CMLS2 [R/W]

01110111 1111111

CMLS3 [R/W]